数据库管理251期 2024-10-11

- [数据库管理-第251期 一个十年+的PC DIY爱好者看NUMA(20241011)](#数据库管理-第251期 一个十年+的PC DIY爱好者看NUMA(20241011))

-

- [1 NB & UMA](#1 NB & UMA)

-

- [1.1 主板设计](#1.1 主板设计)

- [1.2 UMA](#1.2 UMA)

- [2 Chipset & CPU](#2 Chipset & CPU)

- [3 NUMA](#3 NUMA)

- [4 优化](#4 优化)

- 总结

数据库管理-第251期 一个十年+的PC DIY爱好者看NUMA(20241011)

作者:胖头鱼的鱼缸(尹海文)

Oracle ACE Pro: Database(Oracle与MySQL)

PostgreSQL ACE Partner

10年数据库行业经验,现主要从事数据库服务工作

拥有OCM 11g/12c/19c、MySQL 8.0 OCP、Exadata、CDP等认证

墨天轮MVP、年度墨力之星,ITPUB认证专家、专家百人团成员,OCM讲师,PolarDB开源社区技术顾问,HaloDB外聘技术顾问,OceanBase观察团成员,青学会MOP技术社区(青年数据库学习互助会)技术顾问

圈内拥有"总监"、"保安"、"国产数据库最大敌人"等称号,非著名社恐(社交恐怖分子)

公众号:胖头鱼的鱼缸;CSDN:胖头鱼的鱼缸(尹海文);墨天轮:胖头鱼的鱼缸;ITPUB:yhw1809。

除授权转载并标明出处外,均为"非法"抄袭

NUMA作为现代计算机的重要概念,作为一个估摸从2010年开始接触PC DIY的人,也是拥有十几年的PC DIY经验,对电脑硬件还是有比较深入的了解,本期就瞎扯一下NUMA。

1 NB & UMA

在我刚刚接触PC DIY的时候,估摸着就是P45向X58(二者均为芯片组)主板转变的时候,我的第一台电脑正好是P45主板,而第二台电脑就是X58主板。正好赶上了这波变化,可能大家对这两代主板并不大了解,但是说到另一件事情可能大家就会比较清楚了,X58主板对应的CPU就是第一代酷睿i系列处理器(i3、i5、i7,i9都是后话了,今年又换成了Ultra系列处理器了)。

1.1 主板设计

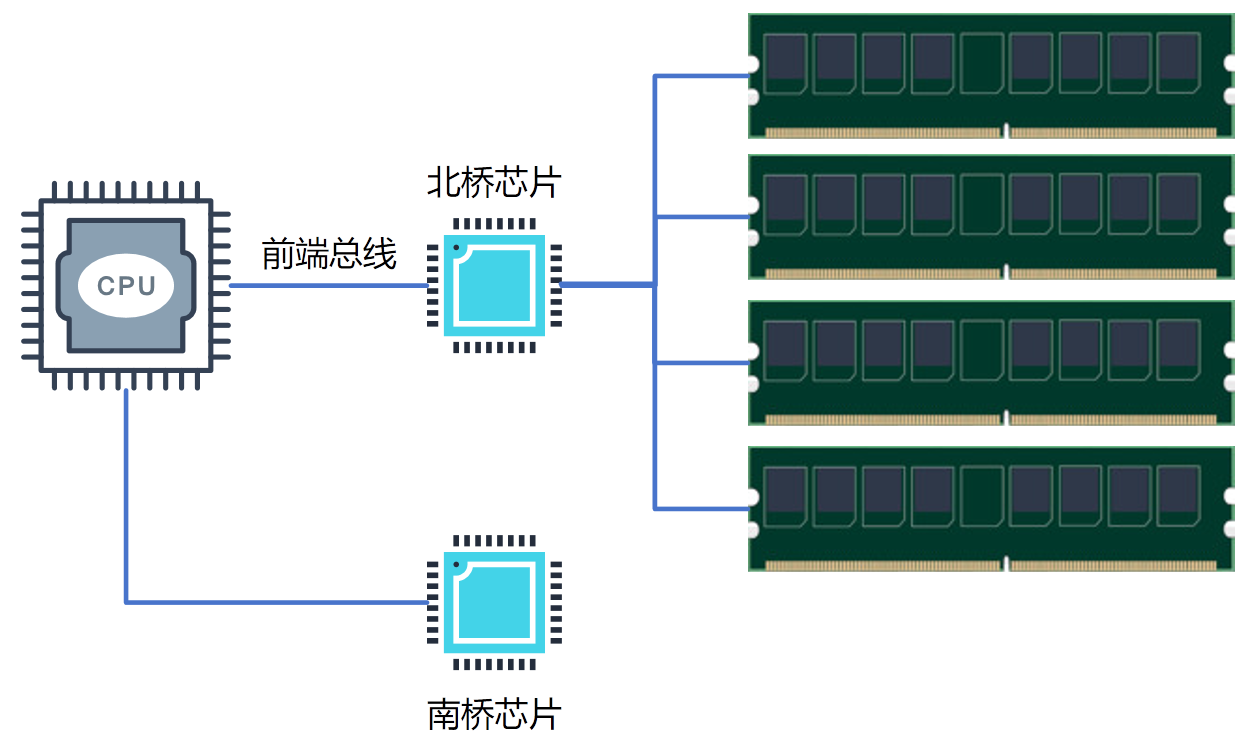

在P45主板的时候,主板上还自带了两个芯片,分别是北桥(NB)和南桥(SB)芯片(同时期的服务器主板设计也是类似的):

- 北桥芯片:系统控制芯片,主要负责CPU与内存、CPU与PCI-E之间的通信。掌控项目多为高速设备,如:CPU、Host Bus。后期北桥集成了内存控制器、Cache高速控制器。一般来说北桥芯片在主板上离CPU更近。

- 南桥芯片:即系统I/O芯片(SI/O):主要管理中低速外部设备;集成了中断控制器、DMA控制器。

这里可以看到,北桥和南桥芯片是负责不同的内容的,而其中最重要的一件事情就是内存控制器是集成在北桥之中的,CPU要访问内存需要使用前端总线(FSB)到北桥后再到多条内存:

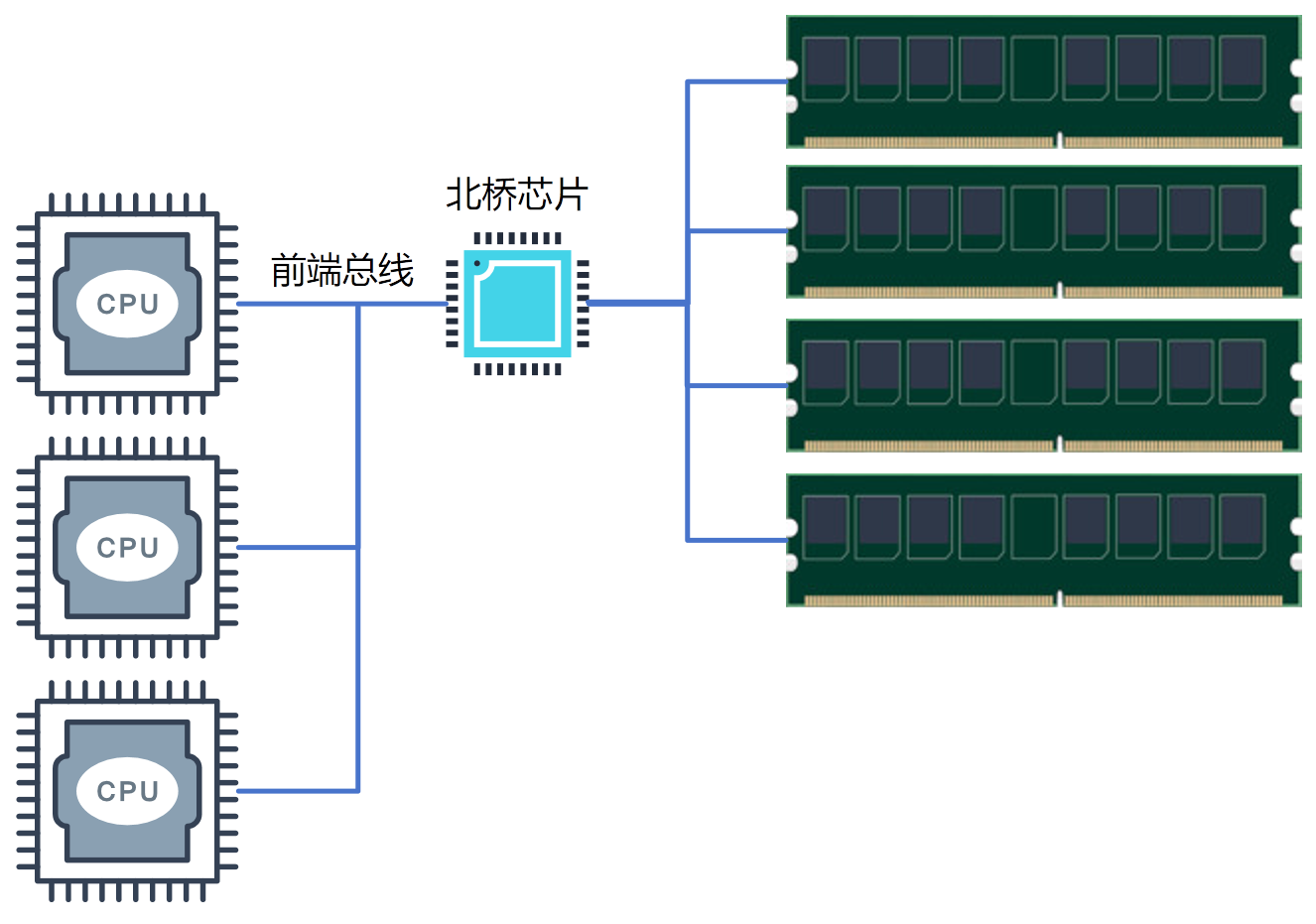

在服务器多CPU环境中多个CPU访问内存就需要通过前端总线经过北桥芯片访问多条内存:

1.2 UMA

UMA,Uniform Memory Access,一致性内存访问。通过北桥芯片中的内存控制器访问内存的这种架构就是UMA,总线模型保证了CPU所有的内存访问都是一致的,不用考虑不同内存地址的差异。

但是这种设计也带来了一些问题:

- CPU需要先通过主板电路访问北桥芯片中的内存控制器,内存控制器再通过主板电路到多条内存的DIMM接口访问内存,传输链路较长

- 在多CPU场景下的单一的前端总线设计会造成传输瓶颈

2 Chipset & CPU

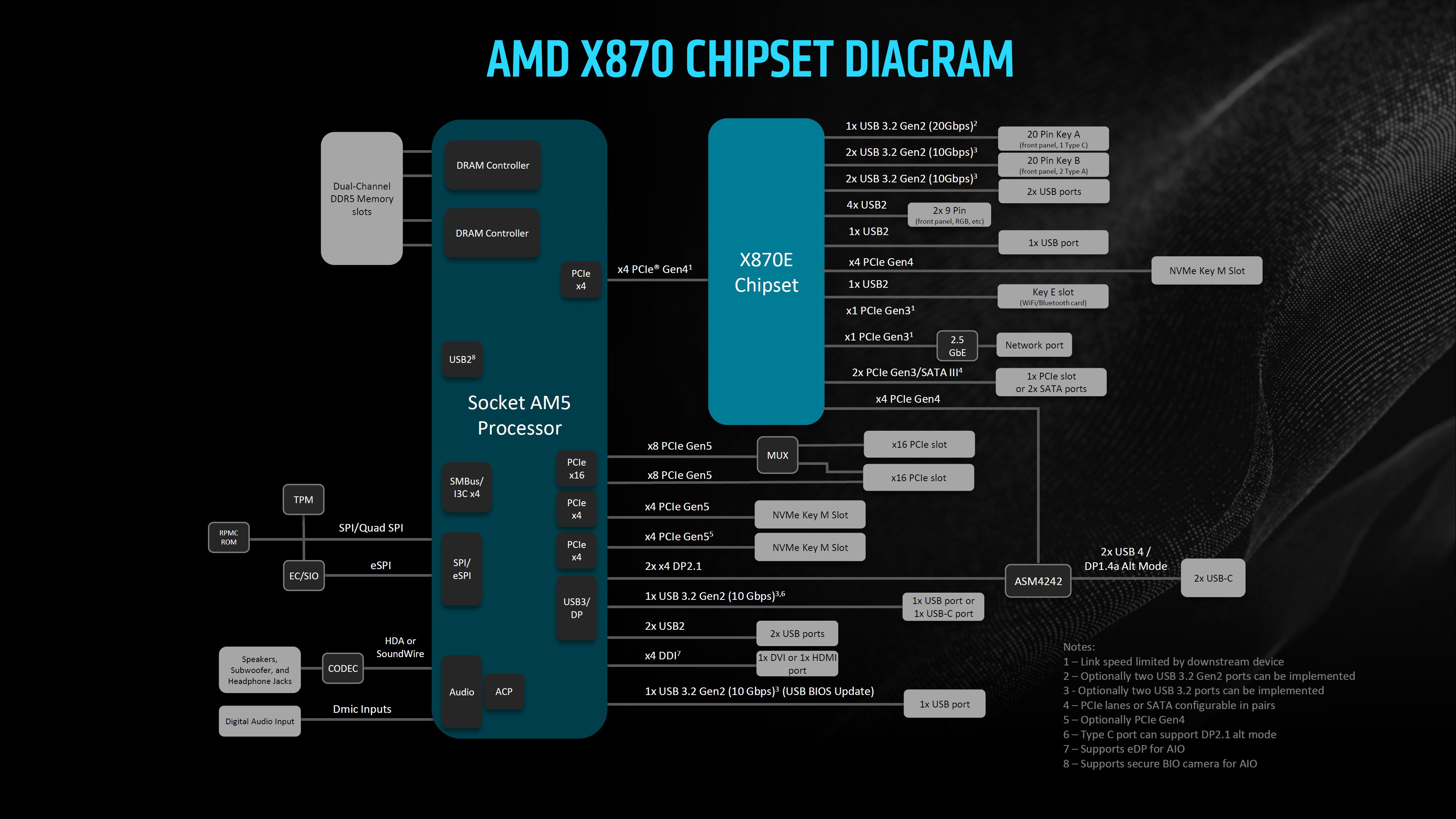

从X58开始,CPU和主板的相关设计就产生了较大的变化,其中比较重要的一点就是内存控制器被整合进了CPU内(当然还包括部分PCIe通道),而主板上北桥和南桥芯片的其他一些功能被整合进了芯片组。下面为AMD最新的桌面级X870E主板示意图,可以看到CPU与芯片组的分工:

这样的设计带来了以下一些变化:

- 减少了CPU核心到内存控制器的距离,减少了延时

- 每个CPU访问属于自己的部分内存,使得内存扩展变得容易且不易出现瓶颈

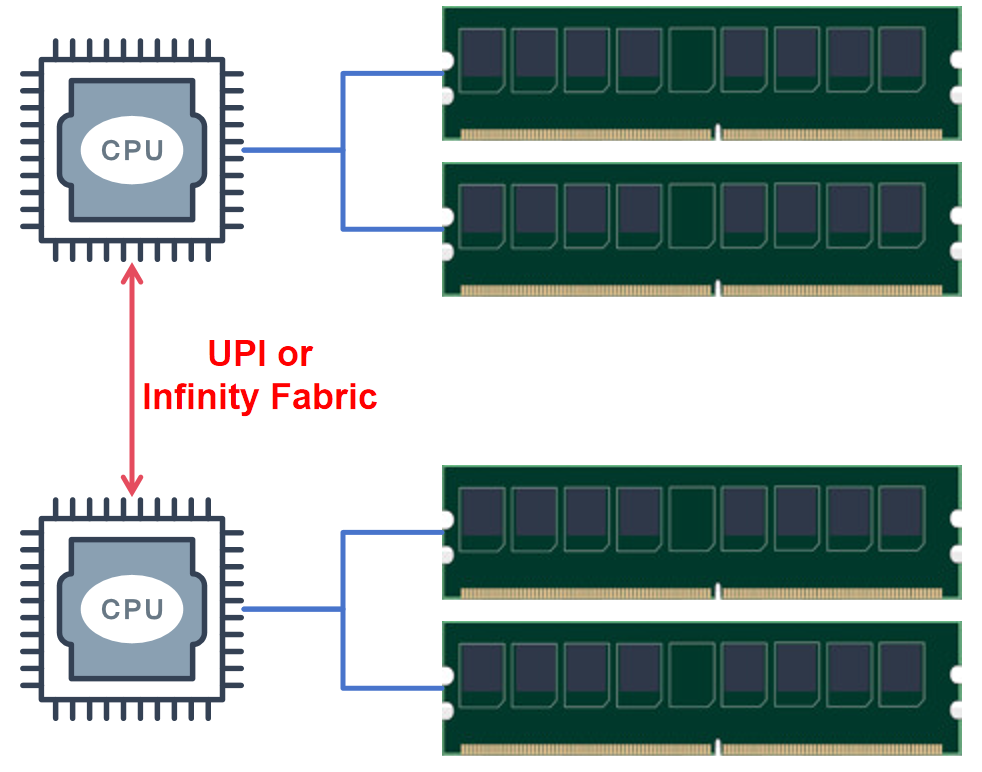

- 多个CPU之间使用Intel UPI(Ultra Path Interconnect)或AMD Infinity Fabric等技术互联进行交互数据

3 NUMA

正是由于设计的变化,尤其是每个CPU访问属于自己部分的内存,对于全局来说不是一致的,需要考虑不同内存地址的差异,NUMA(Non-Uniform Memory Access)也就应运而生。这里也带来了一些新的问题:

- 内存访问出现了本地和远程的区别,比如两份需要关联使用的数据分别存放CPU1和CPU2对应的内存中,需要关联使用时则需要使用UPI/Infinity Fabric在两个CPU之间交互

- 即便UPI/Infinity Fabric非常快但是相较于CPU内部数据交互,内存的远程访问延迟明显高于本地访问

- 多核心CPU中可能存在多个内存控制器,每个内存控制器有若干通道,会出现CPU内部多组NUMA的情况

4 优化

在一些对响应要求比较极端的系统中,会将一些操作制定到固定的NUMA节点中,以避免内存的远程访问,这需要对CPU逻辑核心、物理核心、内存控制器配置以及自身软件设计、负载和操作系统有深入了解。

增加单Socket CPU物理核心数量,优化CPU中内存控制器设计,减少CPU Socket的数量。

从CPU微码层面针对运行软件进行优化,以减少内存远程访问。

开辟独立的内存区域专门用于NUMA交互缓存,需要软件做出相关设计。

...

总结

本期非常基础的介绍了NUMA,更多关于NUMA深入的内容可以查看吕海波老师公众号『IT知识刺客』中的相关文章。

老规矩,知道写了些啥。