-

双击桌面的Quartus图标打开Quartus工具。

-

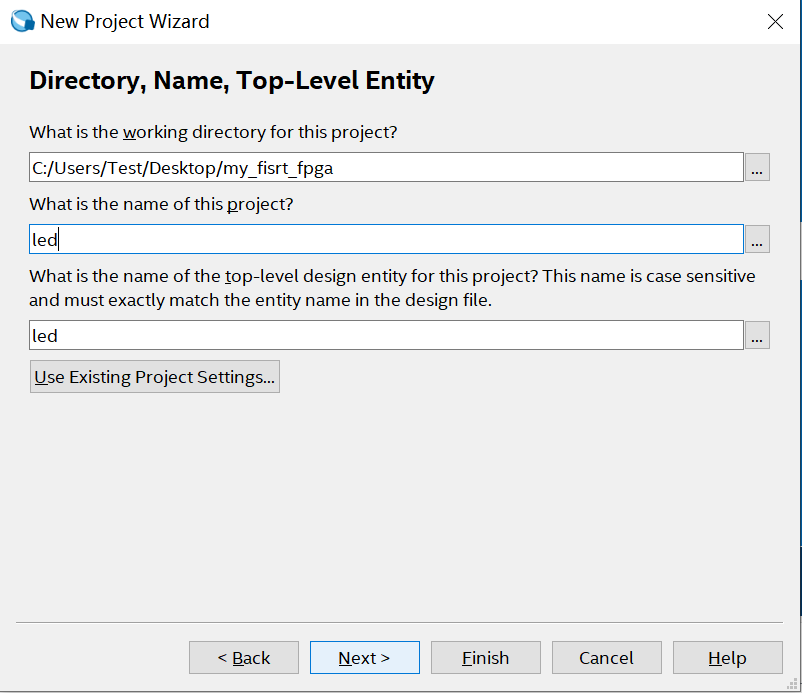

指定工程路径。

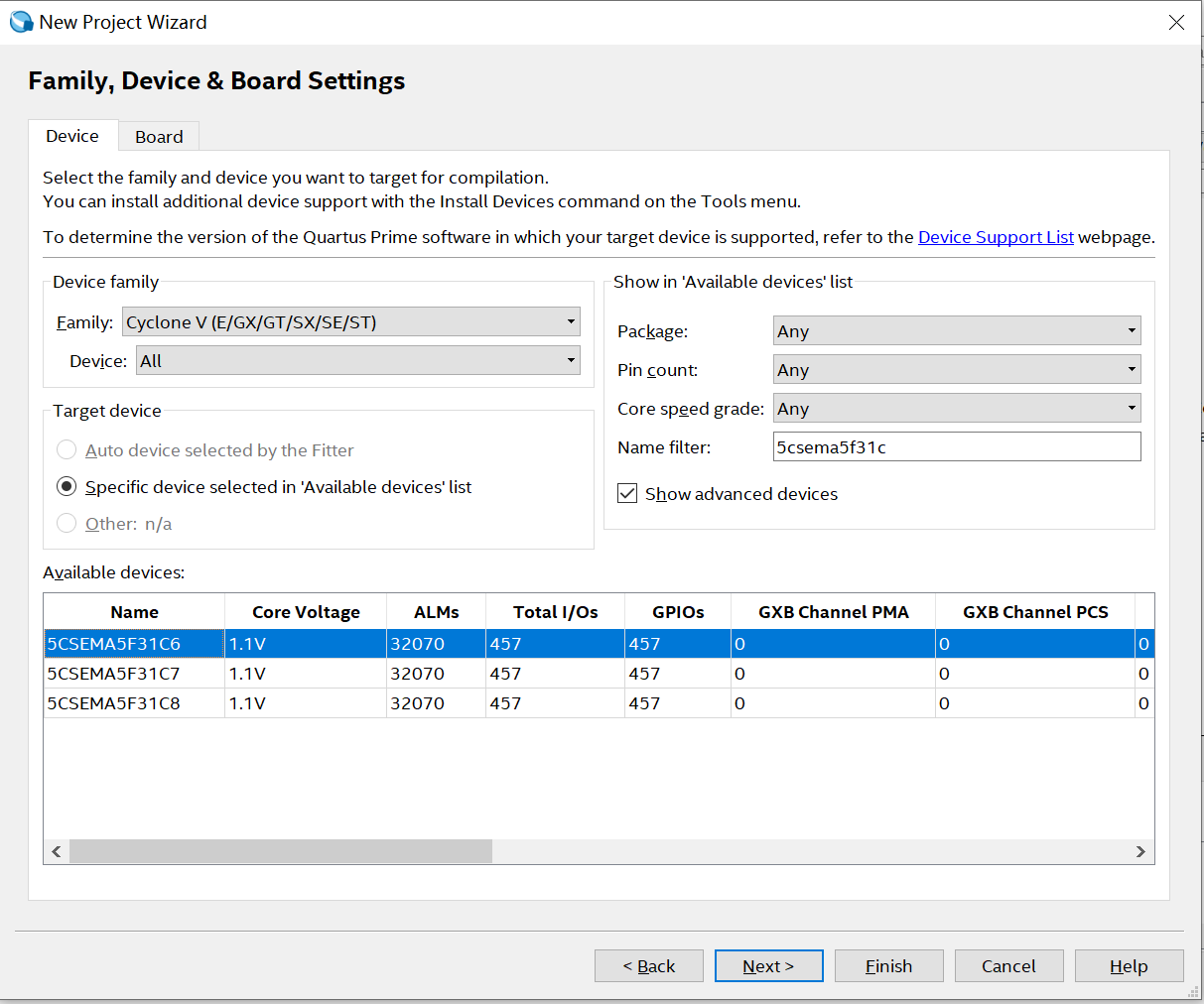

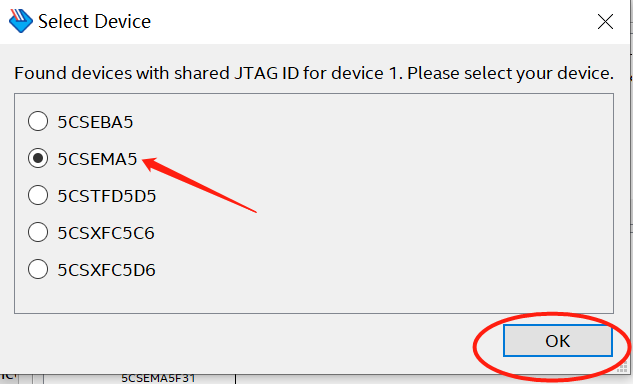

- 点击四次Next,选择5csema5f31c6器件(这个器件正好是DE1-SOC开发板上对应的FPGA device):

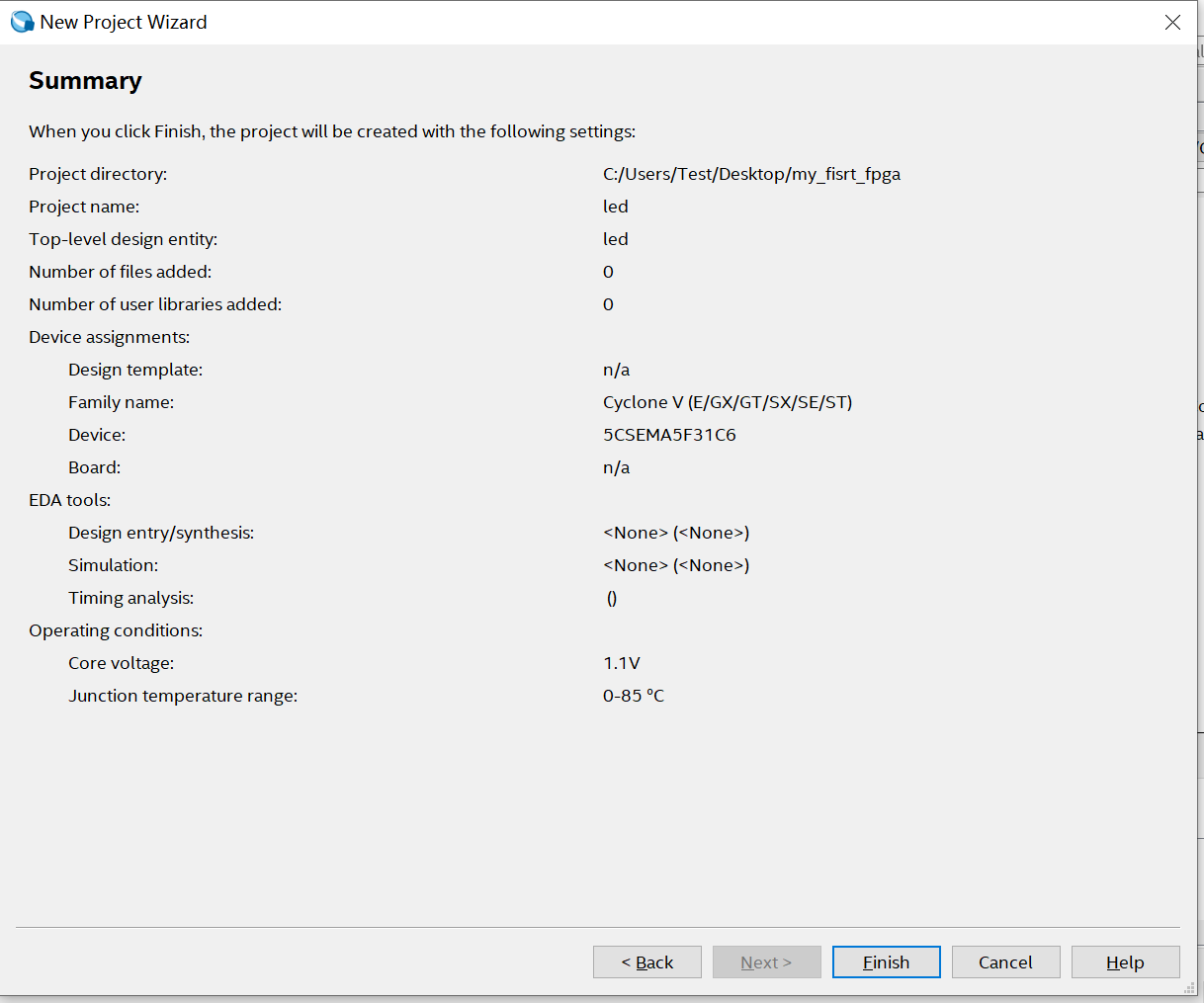

- 再点击三次Next,然后点击Finish,这样工程就创建好了。

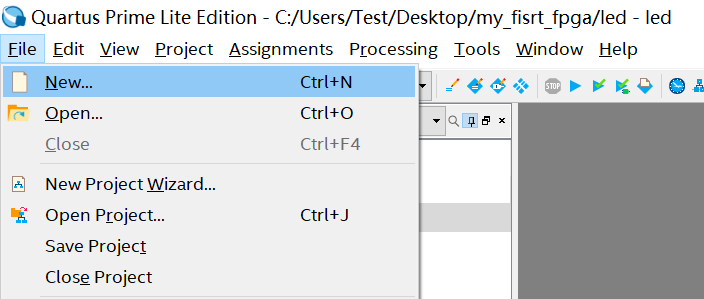

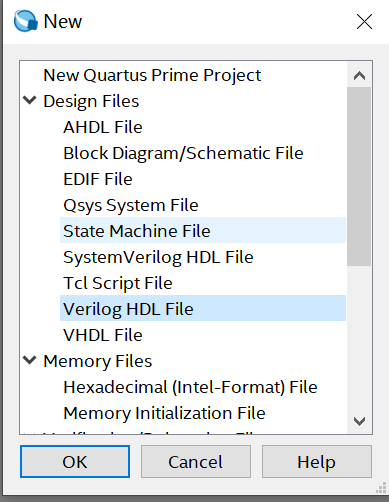

- 点击File------New,选择Verilog HDL File,点击OK来创建top文件。

-

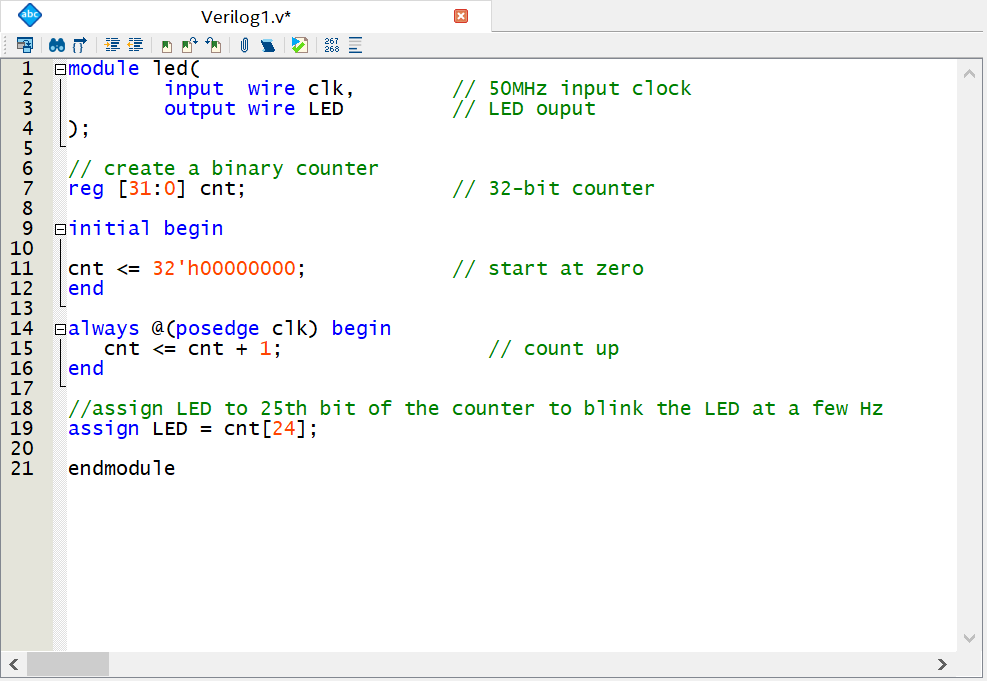

将点亮LED 的verilog代码复制到.v文件当中:

module led(

input wire clk, // 50MHz input clock

output wire LED // LED ouput

);// create a binary counter

reg [31:0] cnt; // 32-bit counterinitial begin

cnt <= 32'h00000000; // start at zero

end

always @(posedge clk) begin

cnt <= cnt + 1; // count up

end

//assign LED to 25th bit of the counter to blink the LED at a few Hz

assign LED = cnt[24];

endmodule

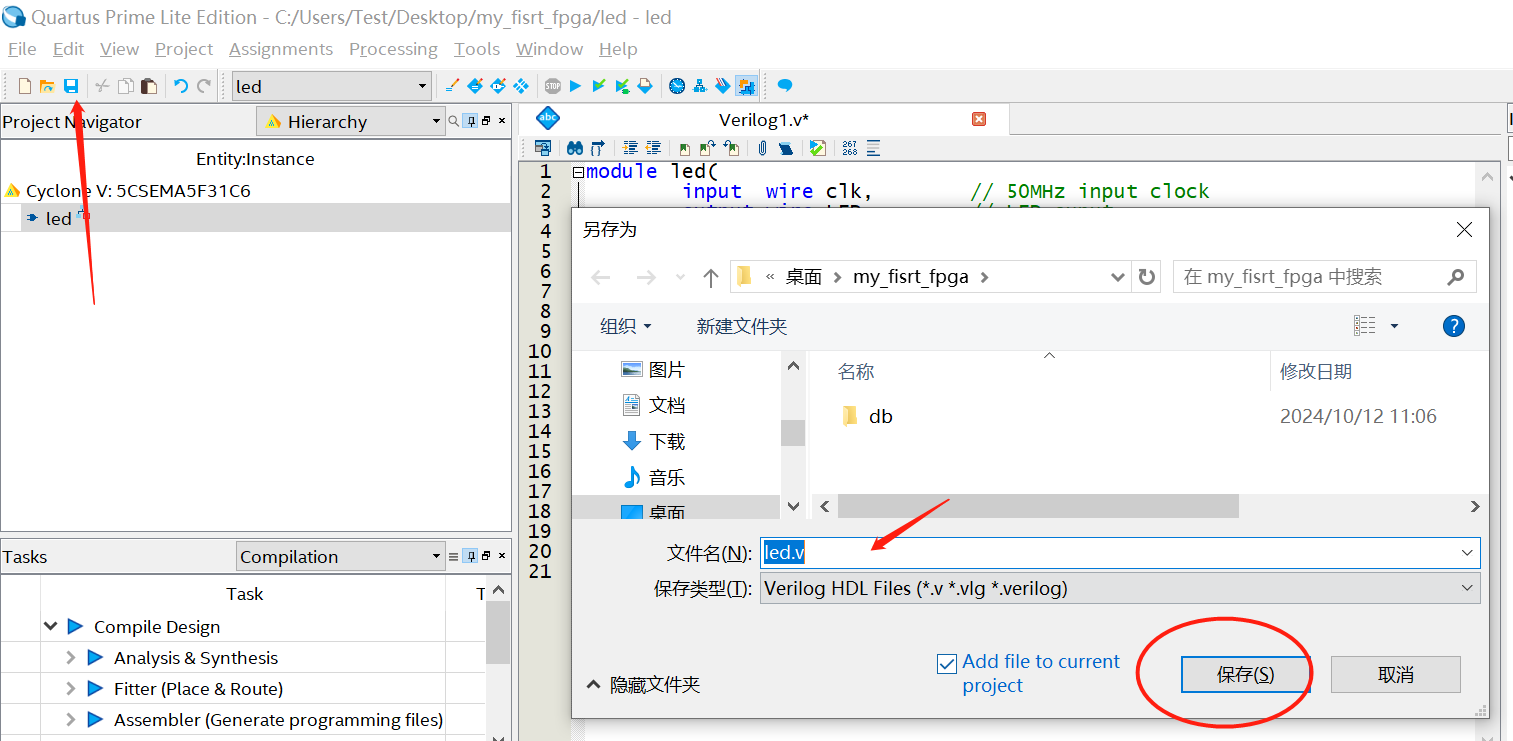

- 点击保存:

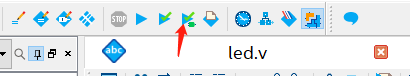

- 点击分析与综合:

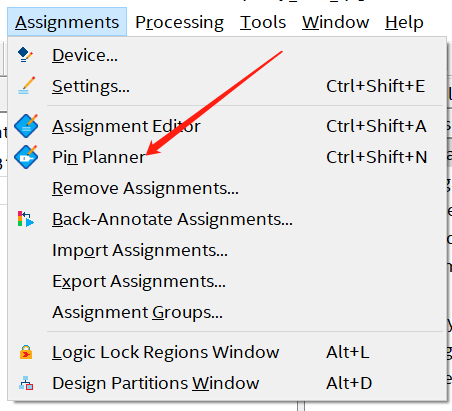

- 点击Pin Planner:

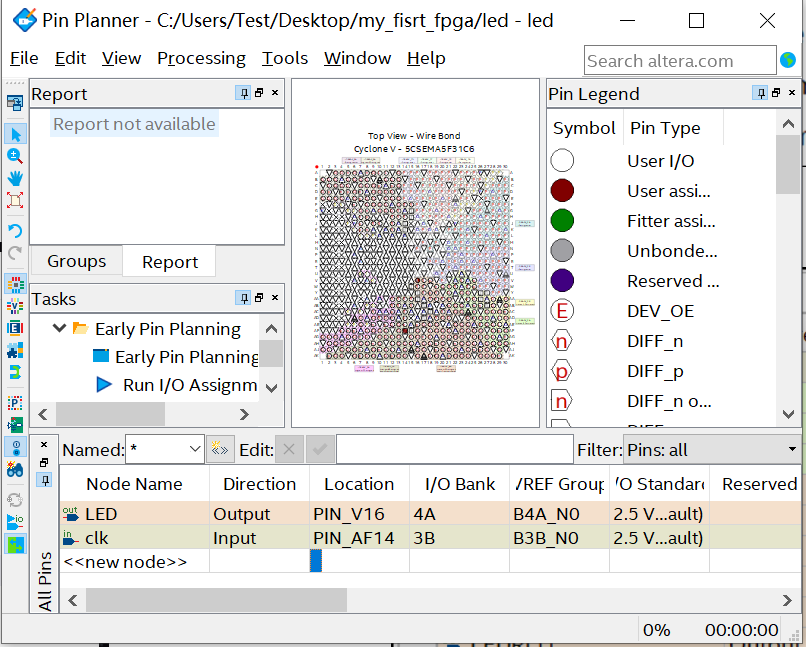

- 引脚分配如下:

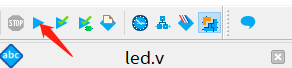

- 关闭Pin Planner窗口,进行全编译:

-

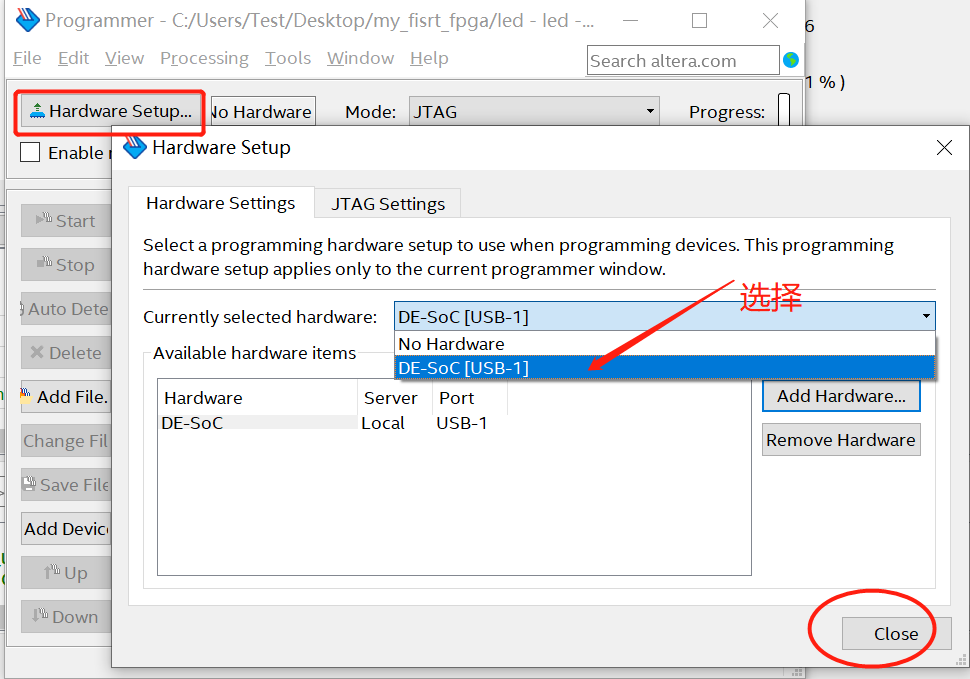

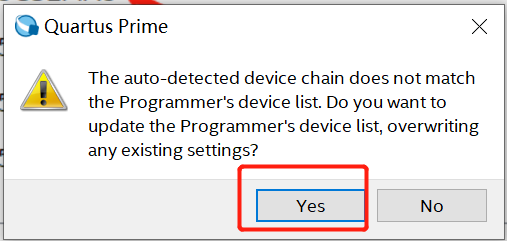

给DE1-SOC开发板上电,插上USB Blaster线缆并连接到PC机。

-

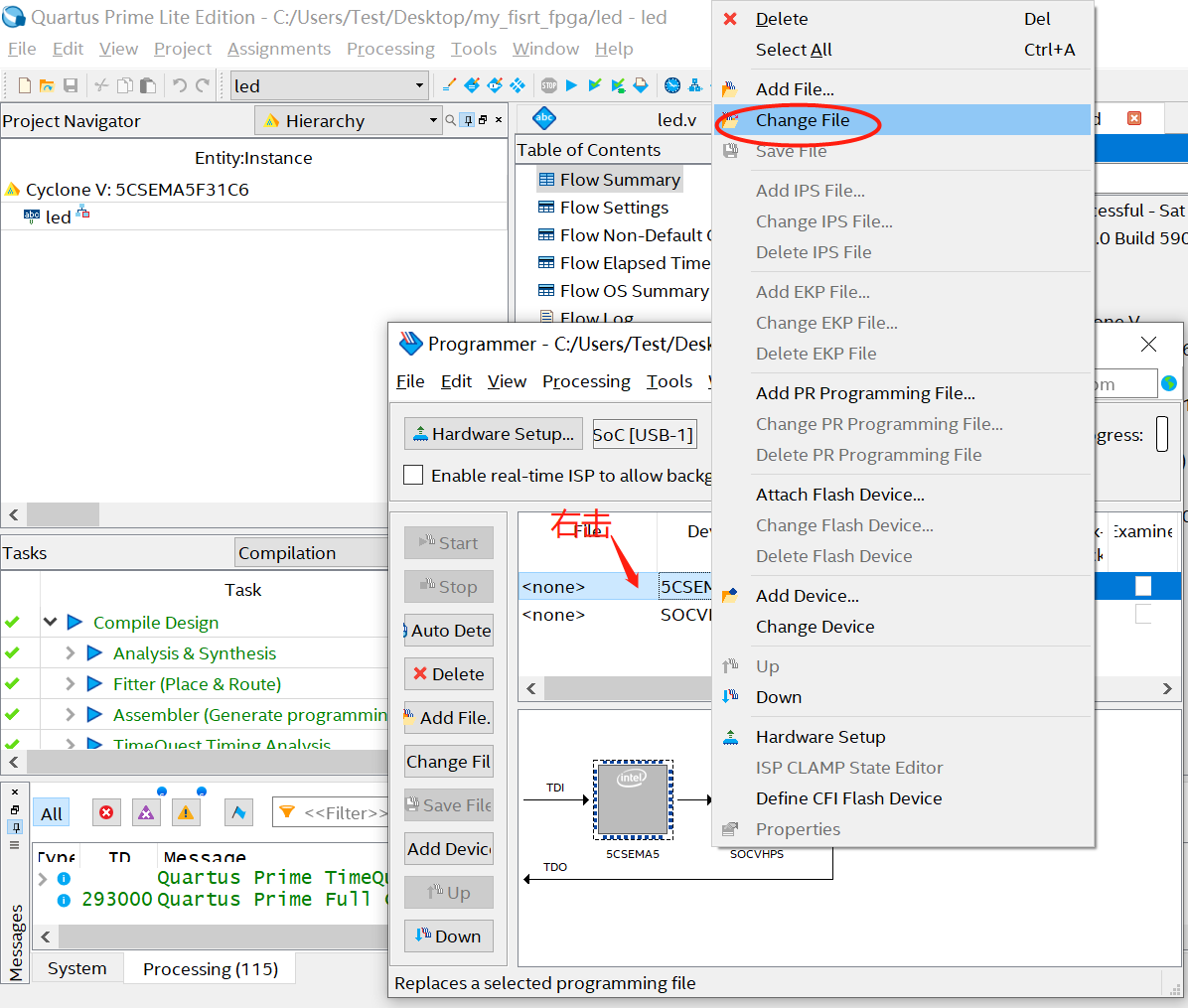

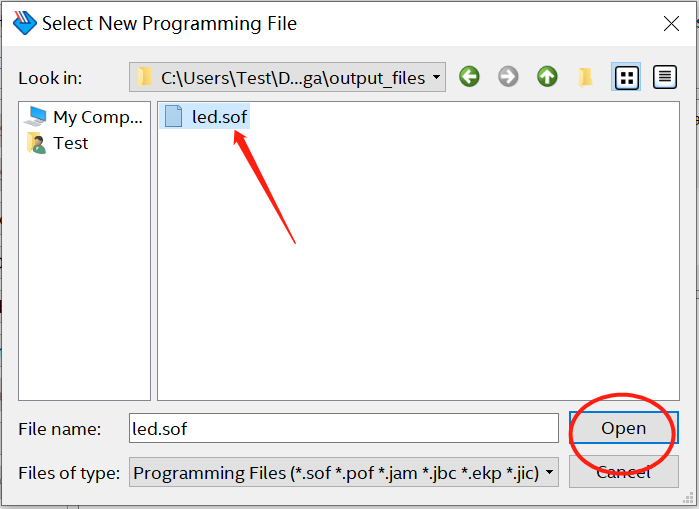

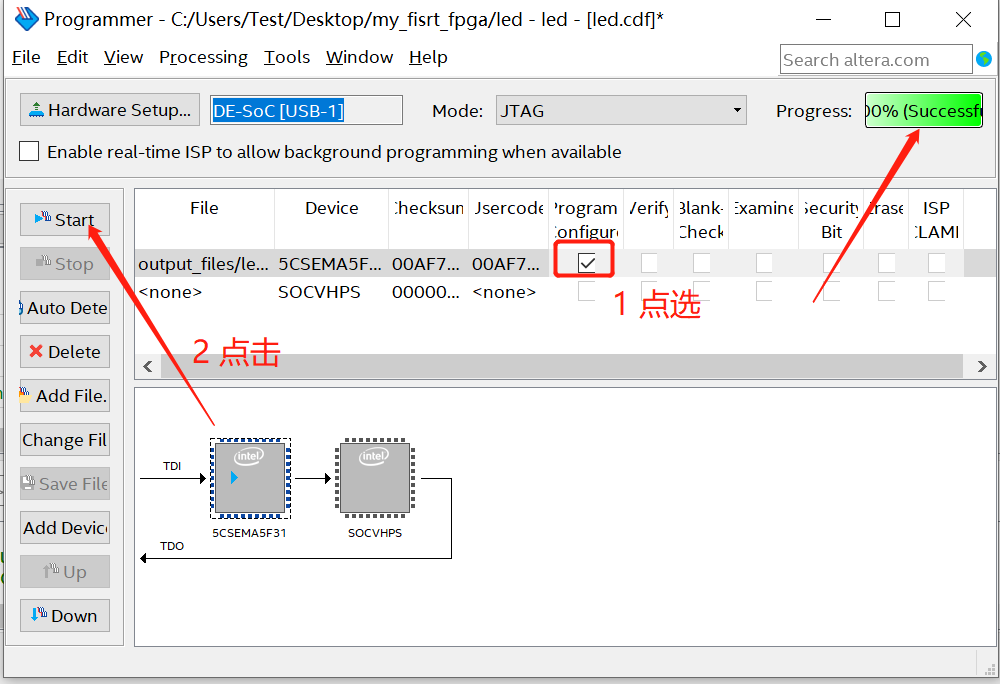

打开Programmer窗口进行sof文件的下载:

可以观察到DE1-SOC的LEDR0在闪烁: