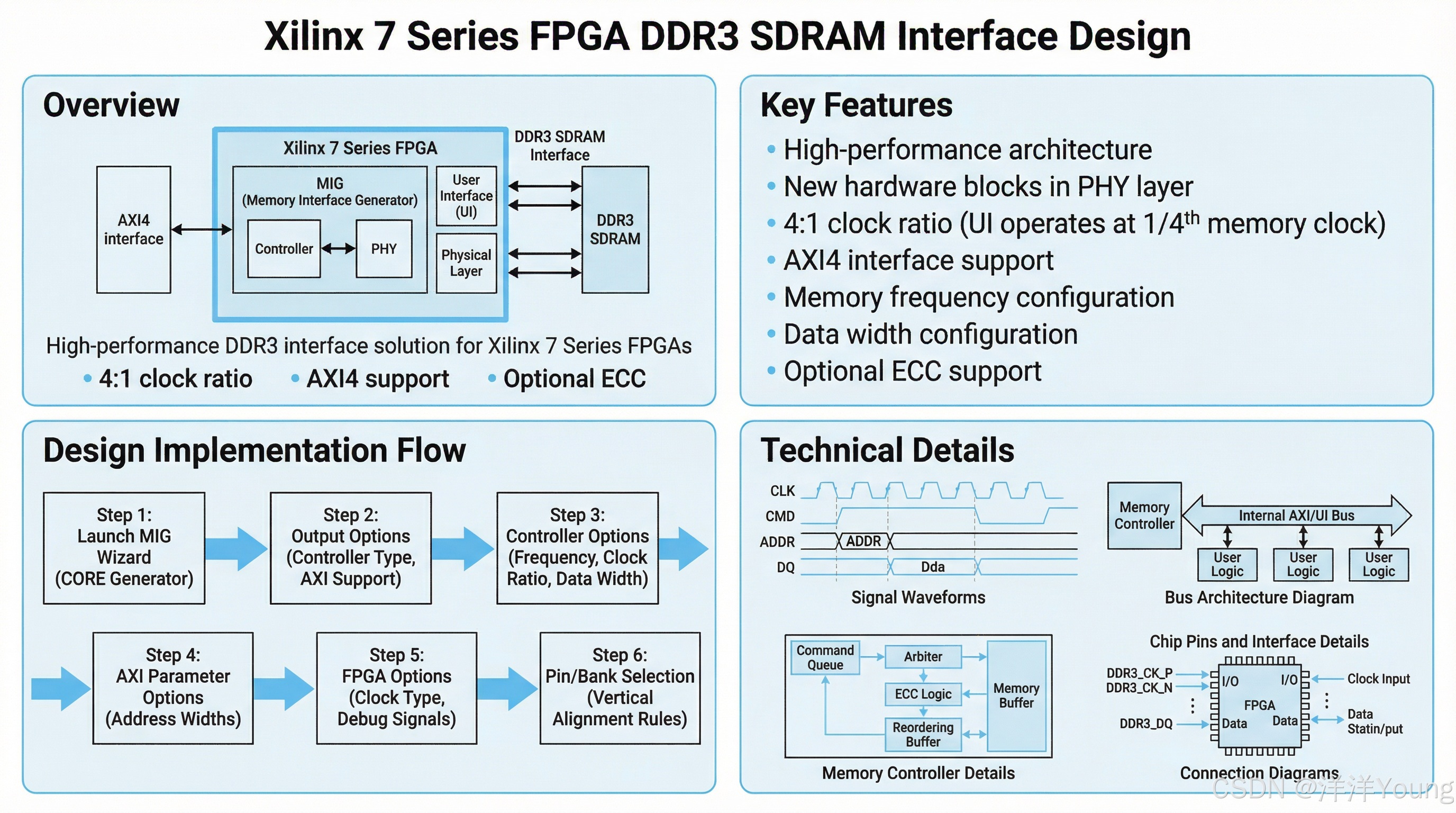

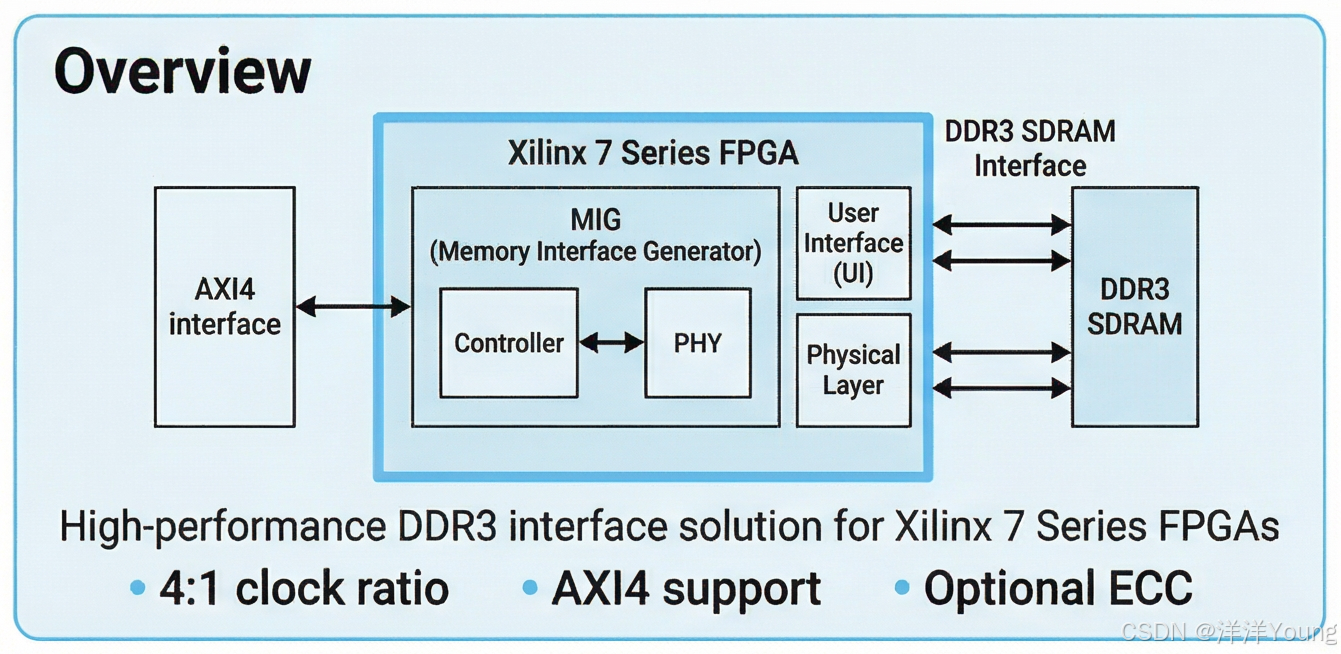

Xilinx 7 系列 FPGA 提供了一个高性能内存接口解决方案,其预设计的控制器和物理层组合,用于连接 7 系列 FPGA 和 DDR2/DDR3 SDRAM 颗粒。用户接口(User Interface, UI)部分支持 AXI4 接口,用于高性能数据传输,物理层(PHY)部分解释控制器如何实际与内存芯片通信,专门的硬件模块处理高速信号,还有校准序列来调整时序,确保数据可靠传输。本文主要参考 Xilinx UG586 用户指南,介绍 DDR3 控制器接口功能、核心架构与设计指南。

(图片由 Nano Banana Pro 生成)

目录

[1 功能概述](#1 功能概述)

[2 核心架构](#2 核心架构)

[2.1 用户接口 UI](#2.1 用户接口 UI)

[2.2 AXI4 接口](#2.2 AXI4 接口)

[2.3 内存控制器 MC](#2.3 内存控制器 MC)

[2.4 物理层 PHY](#2.4 物理层 PHY)

[3 配置与生成流程](#3 配置与生成流程)

[4 设计指南与约束](#4 设计指南与约束)

1 功能概述

Xilinx 7 系列 FPGA 提供了一个高性能内存接口解决方案,其预设计的控制器和物理层组合,用于连接 7 系列 FPGA 和 DDR2/DDR3 SDRAM 颗粒。

其中 DDR3 SDRAM 接口提供的功能如下:

- 提供预设计的控制器与物理层 PHY,可直接用于 7 系列 FPGA 设计

- 支持 AXI4 接口(可选),便于与 AMBA 总线系统集成

- 支持用户接口(UI) 用于非 AXI 设计

- 支持多控制器设计(最多4个控制器)

- 支持ECC(错误校正码)(仅适用于 72 位数据宽度)

- 支持读写命令重排序以提高效率

2 核心架构

2.1 用户接口 UI

用户接口(User Interface,UI)提供一个可选的内存映射接口,即数据与地址相对应,包含一组展平的地址空间与读写数据缓存。

- 提供 app_* 信号组,用于读写命令、地址、数据交互

- 支持高低优先级请求

- 提供校准完成信号(init_calib_complete)

2.2 AXI4 接口

AXI4 从机接口提供一个工业级标准总线协议的接口,用于 AXI4 传输与 UI 接口映射。

- AXI4 接口可选,支持 AXI4-Lite 控制/状态寄存器接口

- 支持窄突发传输、读写通道仲裁

2.3 内存控制器 MC

内存控制器(Memory Controller,MC)前端与 UI Block 相连,后端与物理层 PHY 相连,允许用户设计提交内存读写请求与数据。

- 支持命令重排序以提高吞吐量

- 支持自动刷新管理

- 支持多Rank/Bank管理

2.4 物理层 PHY

物理层(Physical Layer,PHY)实现内存控制器与外部 DDR3 颗粒的交互,同时 PHY 层还管理外部器件的时序。

- 包含 PHASER_IN/OUT、IODELAY、IO FIFO 等专用硬件模块

- 支持读写校准(Write Leveling、Read Leveling、OCLKDELAYED Calibration等)

- 支持初始化与校准序列,确保信号时序正确

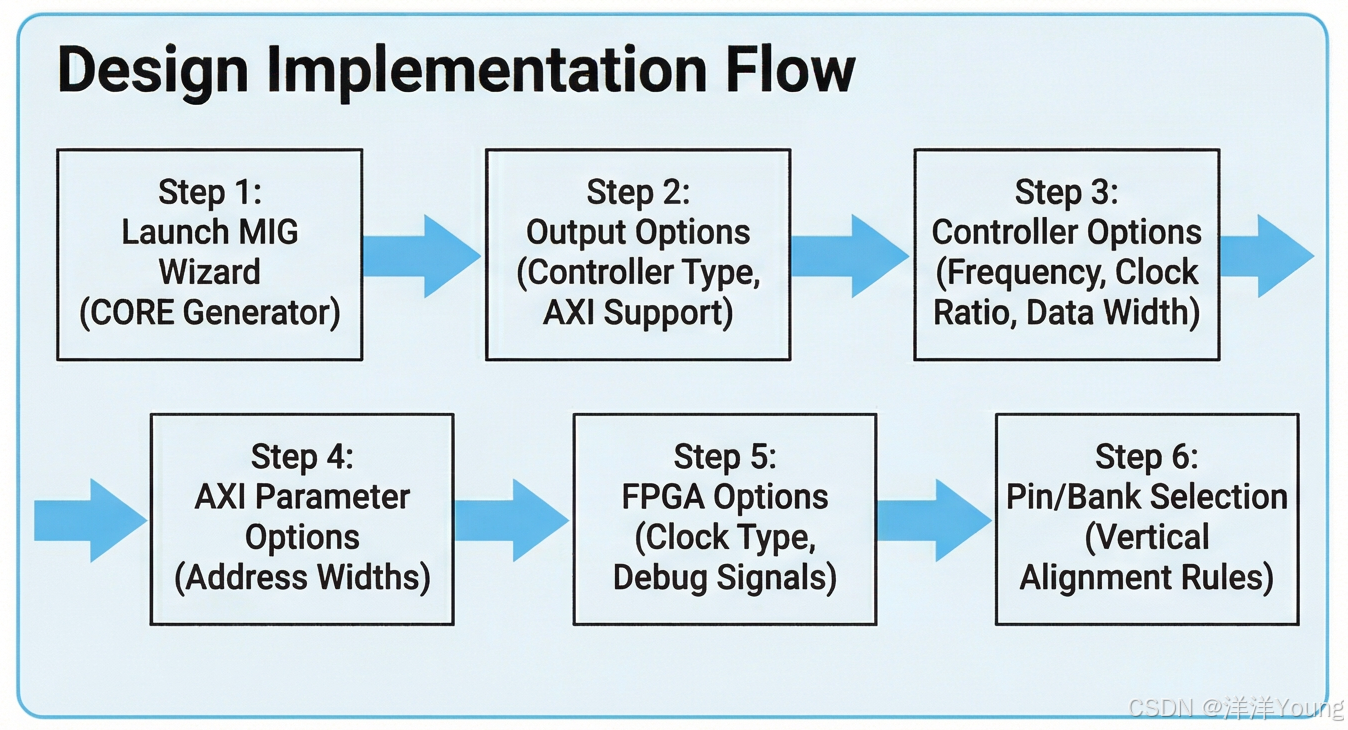

3 配置与生成流程

工具支持

- 支持 CORE Generator(ISE) 和 Vivado Design Suite

- 提供图形化配置向导(Memory Interface Generator,MIG)

主要配置选项

- 控制器类型:DDR3 SDRAM

- 时钟频率:根据 FPGA 型号和速度等级选择。

- 数据宽度:8 位至 72 位(支持 ECC 时 72 位)

- PHY与控制器时钟比例:4:1(高频)或 2:1(低延迟)

- 是否启用AXI4接口

- 是否启用数据掩码(Data Mask)

4 设计指南与约束

- 引脚分配需符合 Bank 与 Byte 分组规则。

- 时钟输入需使用专用时钟引脚。

- 需提供 200 MHz 参考时钟用于 IDELAYCTRL。

- 支持多控制器共享系统时钟。

- PCB 设计建议(如终端电阻、走线长度匹配等)。