目录

[3.1 扩频](#3.1 扩频)

[3.2 插入导频](#3.2 插入导频)

[3.3 2ASK调制](#3.3 2ASK调制)

[3.4 解调](#3.4 解调)

[3.5 帧同步](#3.5 帧同步)

[3.6 基于相关峰的定时点提取](#3.6 基于相关峰的定时点提取)

[3.7 采样判决](#3.7 采样判决)

[3.8 解扩](#3.8 解扩)

1.引言

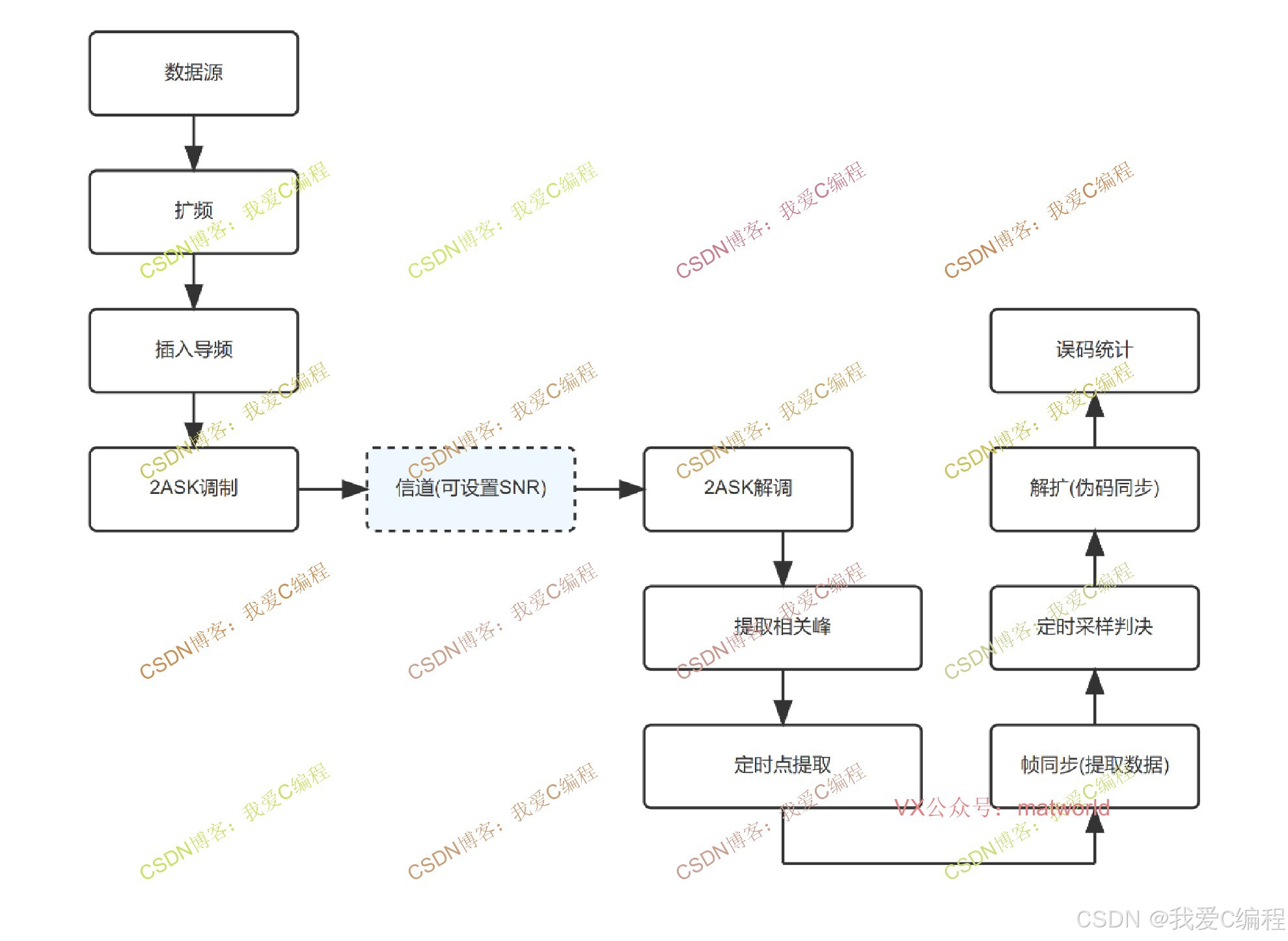

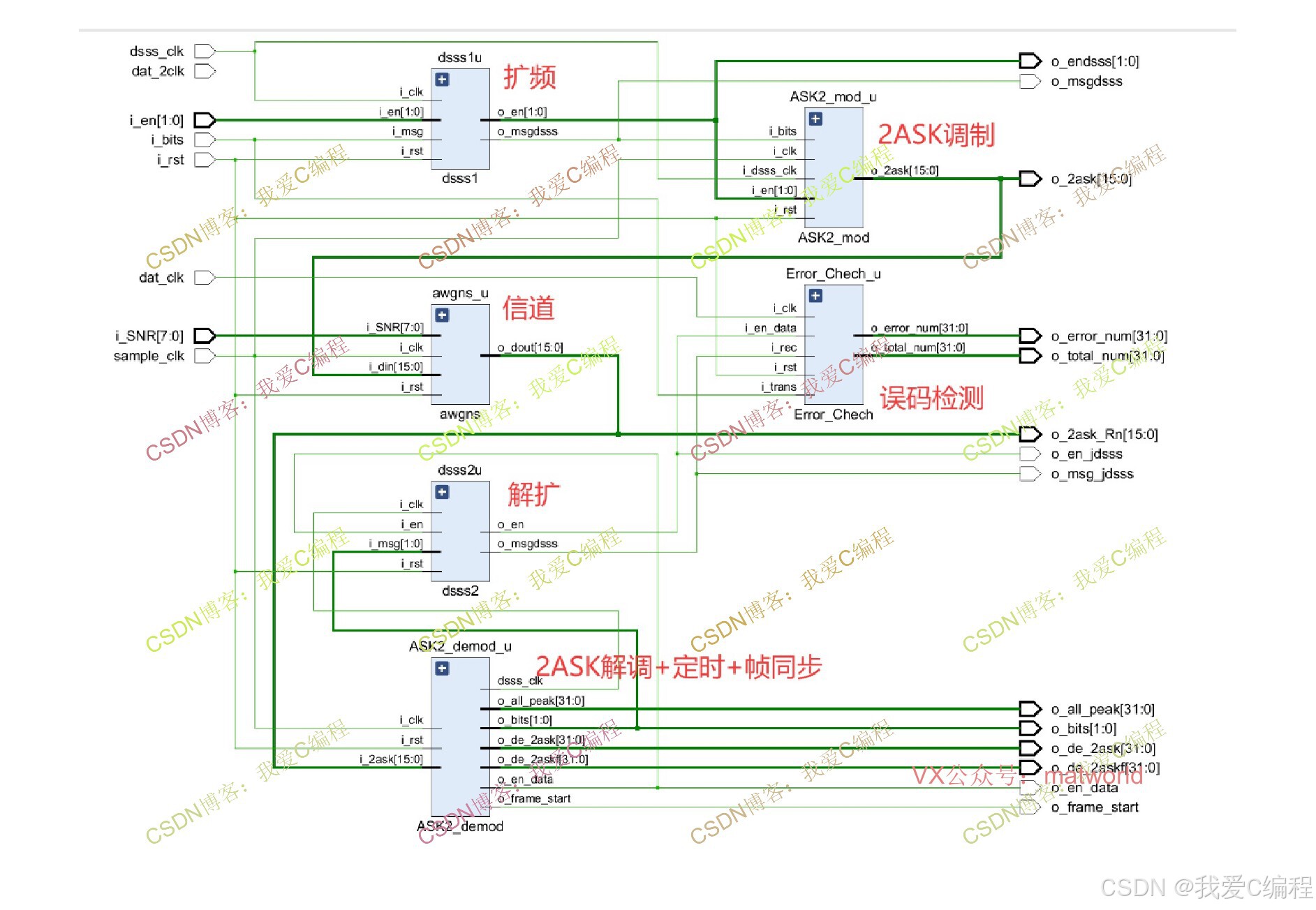

基于FPGA的2ASK通信链路实现,系统包括2ASK调制模块,2ASK相干解调模块,AWGN信道模块,误码统计模块,数据源模块,基于相关峰提取的帧同步和定时点提取模块,扩频解扩等。

2.算法仿真效果

vivado2022.2测试

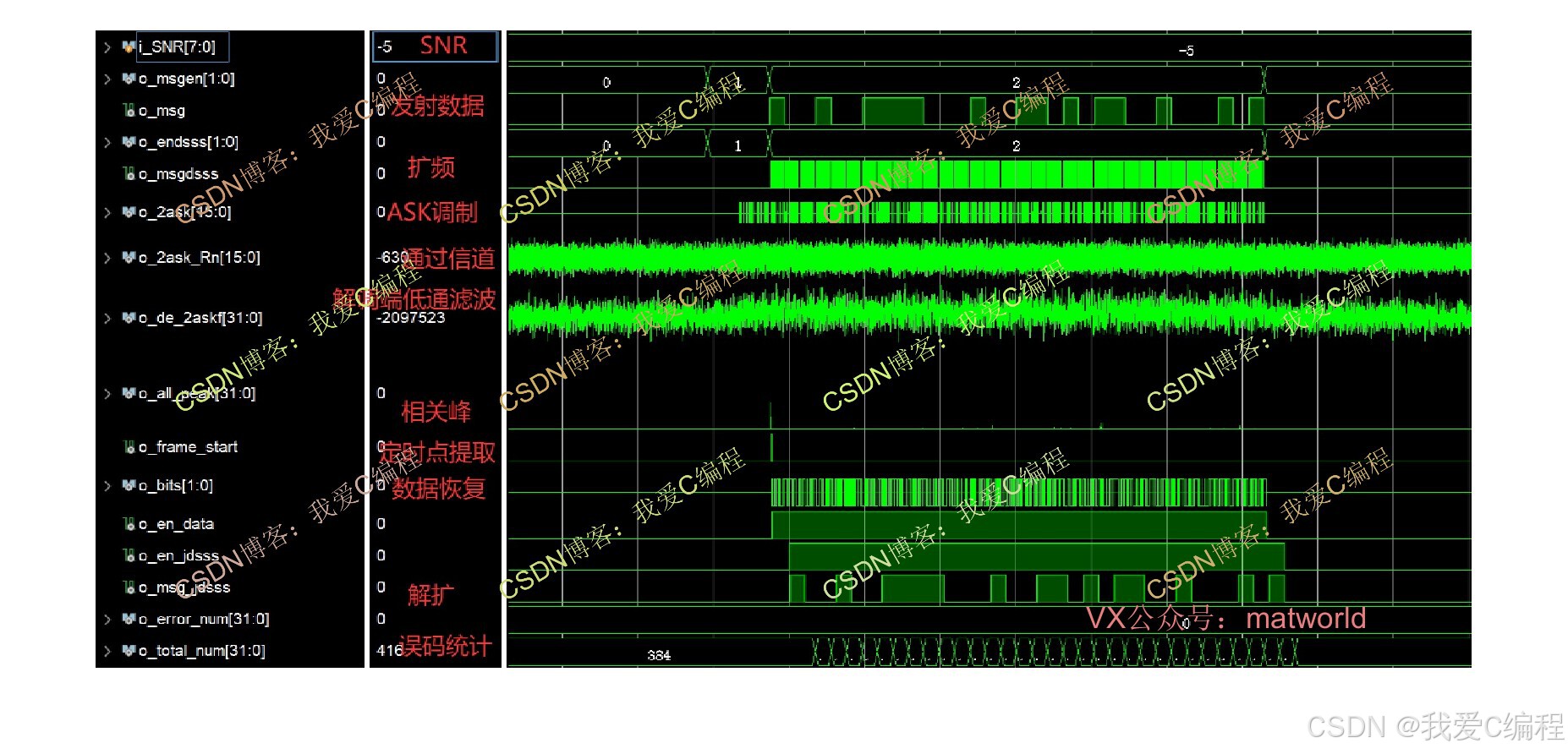

设置SNR=-5db

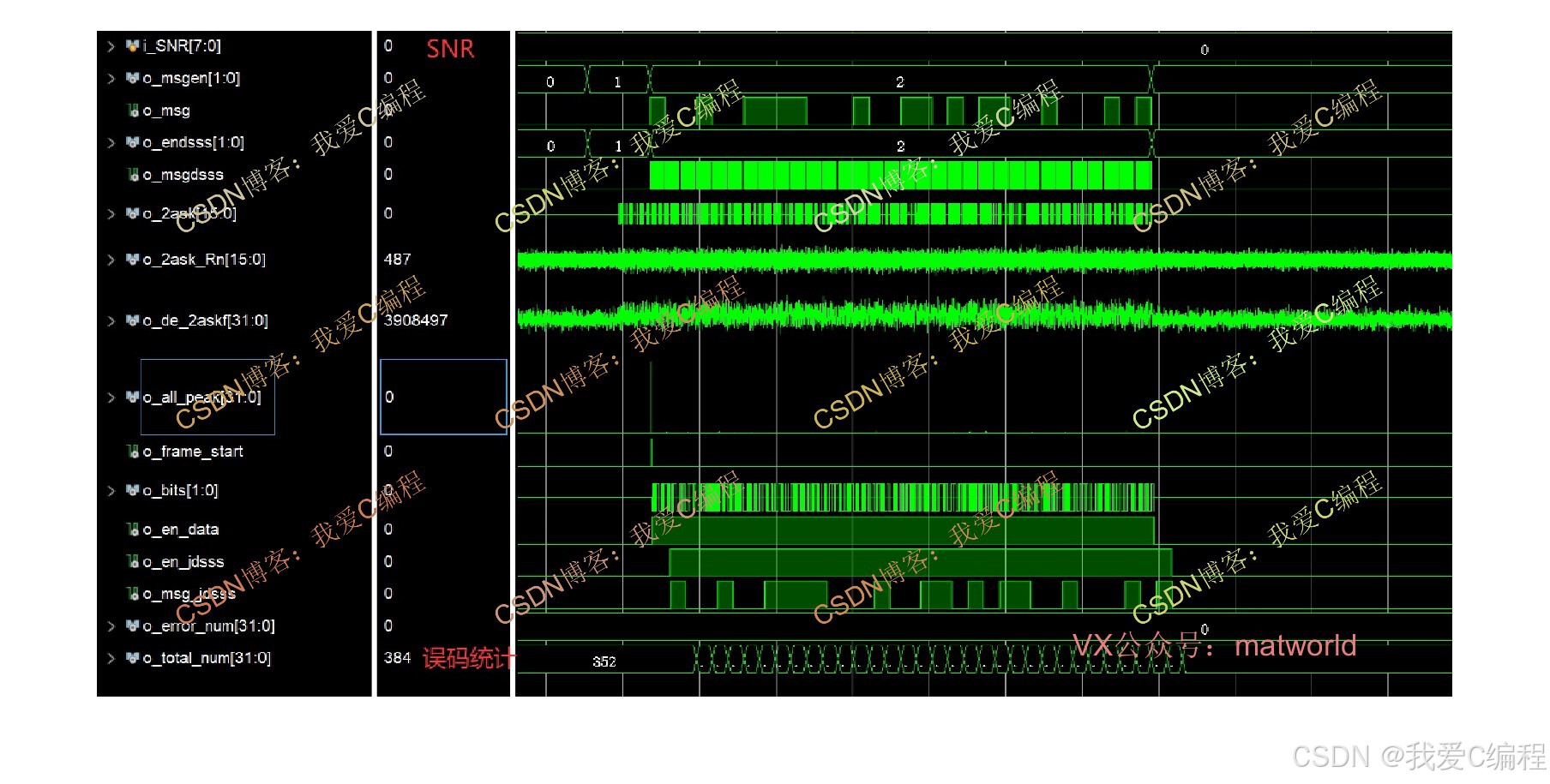

设置SNR=0db

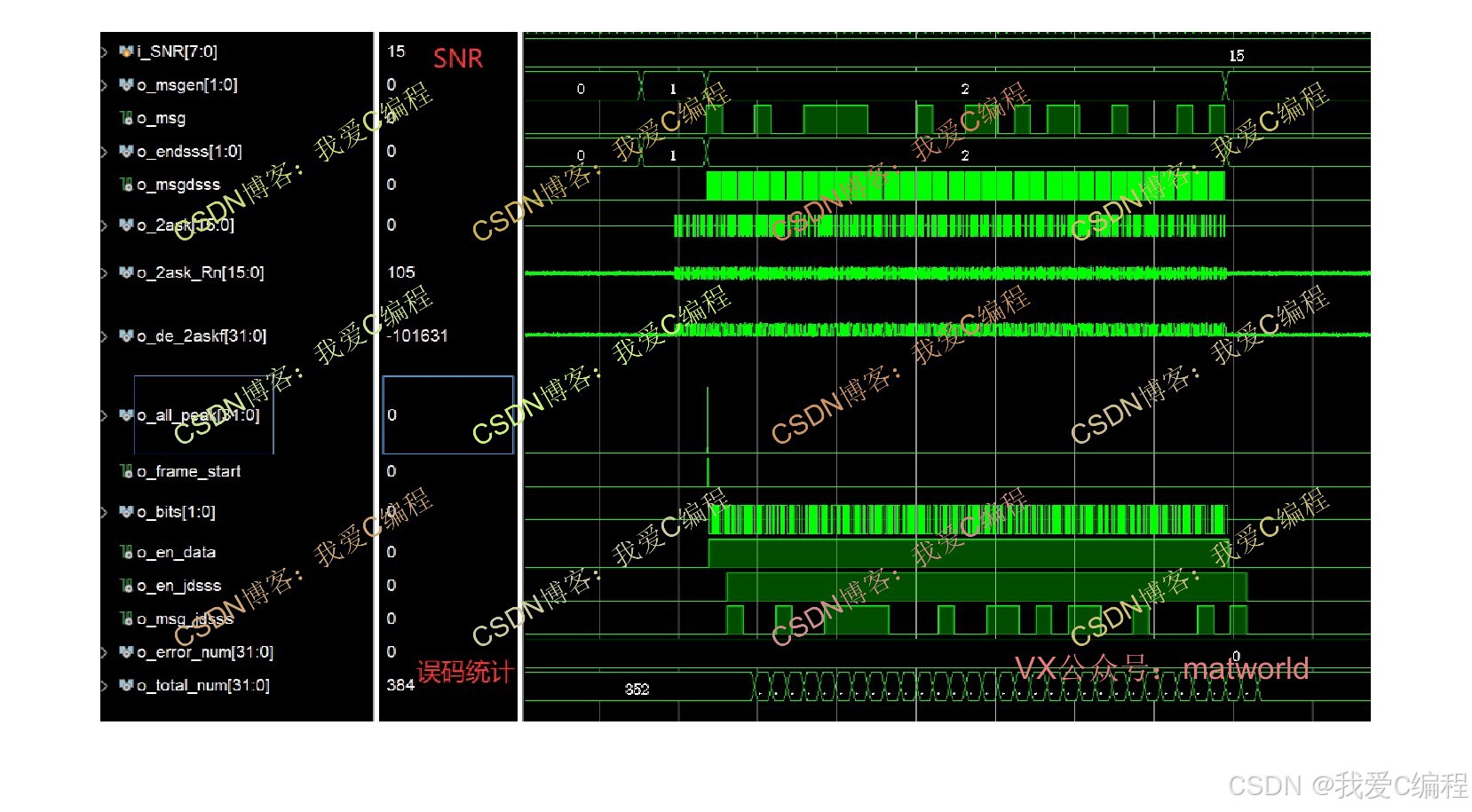

设置SNR=15db

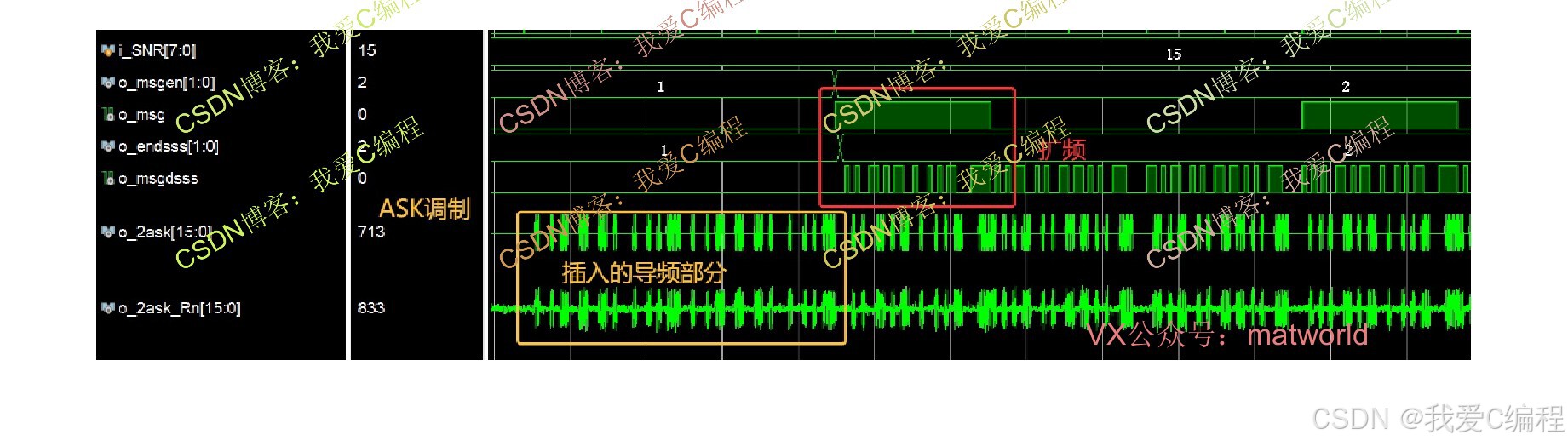

局部放大:

3.算法涉及理论知识概要

整体系统结构如下所示:

3.1 扩频

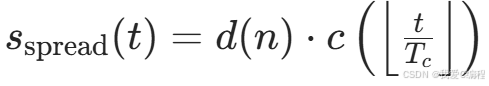

用伪随机码(伪码)c(k)(周期为N,c(k)∈{+1,−1} )扩展信号带宽,实现抗干扰。扩频后信号

3.2 插入导频

插入已知导频序列p(t) ,用于接收端帧同步。导频序列为PN序列,插在数据帧的前面。

3.3 2ASK调制

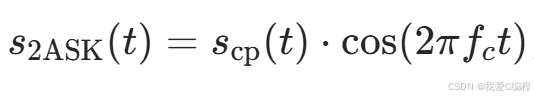

2ASK调制是一种数字调制解调技术,它是基于ASK调制的一种数字调制方式。ASK调制是一种模拟调制方式,它是通过改变载波的振幅来传输数字信号。 2ASK调制的原理是将数字信号转换为二进制码,然后将二进制码与载波信号相乘,得到调制信号。调制后信号:

用载波幅度表示二进制信息,1对应载波,0对应无载波。

3.4 解调

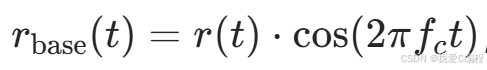

与载波做相干解调,恢复基带信号。解调输出:

经低通滤波后得基带数据的包络。

3.5 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.6 基于相关峰的定时点提取

在接收信号中,通过寻找与本地已知序列(如训练序列或导频序列)的相关峰来确定定时点。具体来说,将接收信号与本地序列进行相关运算,当两者的相位和时间对齐时,相关值会出现峰值,这个峰值点对应的位置就是最佳的定时点,用于确定信号的采样时刻,以保证后续信号处理的准确性。

3.7 采样判决

在确定了定时点后,对接收信号进行采样,将采样值与预设的判决门限进行比较,根据比较结果确定接收信号的电平值,从而恢复出原始的二进制比特流。

3.8 解扩

用与发射端同步的伪码压缩带宽,恢复原始数据。伪码同步后,解扩输出:

在本课题中,伪码同步采用的是伪码峰值判决的方法,当出现峰值时,说明此时伪码同步。

4.Verilog核心接口

整个程序构架如下:

系统RTL结构如下:

5.参考文献

1\]程晓畅,苏绍景,王跃科,等.伪随机码超声扩频测距系统设计与算法\[J\].测试技术学报, 2007, 21(1):5.DOI:10.3969/j.issn.1671-7449.2007.01.016. \[2\]杜勇.数字调制解调技术的MATLAB与FPGA实现\[M\].电子工业出版社,2014. ## 6.完整算法代码文件获得 **完整程序见博客首页左侧或者打开本文底部GZH名片** **(V关注后回复码:X113)** **(或者回复:ASK扩频)** **V**