条件语句

条件语句用于检查块中的语句是否被执行。条件语句创建语句块。如果给出的表达式是 true,执行块中的语句集,如果表达式为 false,则 else 块语句将最后执行。

| 序号 | 条件语句 |

|---|---|

| 1. | if |

| 2. | if-else |

| 3. | if-else ladder |

| 4. | unique if |

| 5. | unique0 if |

| 6. | priority if |

不同条件表达式之间的差异

| 条件 | if elseif | unique if | unique0 if | priority if |

|---|---|---|---|---|

| 只有一个条件表达式为真 | 执行 true 条件块内的语句集 | 执行 true 条件块内的语句集 | 执行 true 条件块内的语句集 | 执行 true 条件块内的语句集 |

| 多个条件表达式为真 | 执行第一个 true 条件块语句,不显示警告 | 执行第一个为真的条件块语句,显示警告 | 执行第一个为真的条件块语句,显示警告 | 执行第一个 true 条件块语句,不显示警告 |

| 没有 else,条件表达式都不为真 | 不执行 true 条件块内的语句, 不显示警告 | 不执行 true 条件块内的语句, 显示警告 | 不执行 true 条件块内的语句, 不显示警告 | 不执行 true 条件块内的语句, 显示警告 |

unique if、unique0 if 和priority if 是 SystemVerilog 中 if-else 条件语句的更新版本。这些条件语句显示警告,有助于检测死代码或未使用的条件语句。

死代码(Dead code)是对模拟或综合没有任何影响的代码。死代码的示例是从未使用的信号或从未触发的条件。

死代码不会打扰模拟器或综合工具。然而,它会消耗任何阅读代码的人的精神能量。人们会尝试找出给定语句的目的,可能需要一段时间才能意识到他们正在处理死代码。这使得审查代码和重用代码的成本更高。一般来说,死代码是一种应该避免的技术债务。

case 语句

case 语句允许我们执行特定 case 表达式的代码。这将为长代码提供正确的结构,并降低代码的复杂性。

case 语句计算给定的表达式,并根据计算值(匹配特定条件)执行与其关联的语句。基本上,它用于根据不同的条件执行不同的操作。

systemVerilog case 语句以 case 关键字开始,以 endcase 关键字结束。多个语句的块必须分组在开始和结束语句中。

在 case 语句中,使用 default 语句。 default语句是可选的,一个case语句中只能有一个default语句。

如果给定的 case 条件都不成立,则执行 default 语句中的语句。

如果没有任何项目与条件匹配并且未给出默认语句,则执行将退出 case 块而不执行任何操作。

如果我们想在 case 语句中给出范围值,这将在 inside 语句的帮助下完成。

语法: case(condition) inside

condition_1_[a:b]: Statements ;

condition_2:_[c:d] Statements ;

...........

conditon_N_[y:z]: Statements;

endcase

在 case 语句中使用 break 时,会发生错误。

使用 disable 关键字禁用任务内的嵌套循环

unique case

在 unique case 语句中,如果所有的 case 条件都为假,它将显示一个警告(没有找到匹配的 case 语句),但不会有错误。 如果所有的条件都为真或有多个条件为真,它将读取第一个正确或匹配的 case 条件,并显示输出,同时伴随一个警告,但不会有错误。

语法:

unique case(condition)

condition_1: Statements ;

condition_2: Statements ;

............

conditon_N: Statements;

endcase

unique case 语句带 default 语句

在这里,我们将在 unique case 语句中使用 default 语句。 如果 unique case 语句中的所有条件都不为真,那么将执行 default 语句。

语法:unique case(condition)

condition_1: Statements ;

condition_2: Statements ;

............

conditon_N: Statements;

default : Statements;

endcase

uniuqe0 case

在 uniuqe0 case 中,如果所有的 case 条件都为假,它将不会显示警告,也不会有错误。 如果所有的条件都为真或有多个条件为真,它将读取第一个正确或匹配的 case 条件,并显示输出,同时伴随一个警告,但不会有错误。

语法:unique0 case(condition)

condition_1: Statements ;

condition_2: Statements ;

...........

conditon_N: Statements;

endcase

priority case

在这种类型的 case 语句中,如果有多个 case 条件为真,它将在不提供任何错误或警告的情况下显示输出。

语法: priority case(condition)

condition_1: Statements ;

condition_2: Statements ;

...........

conditon_N: Statements;

endcase

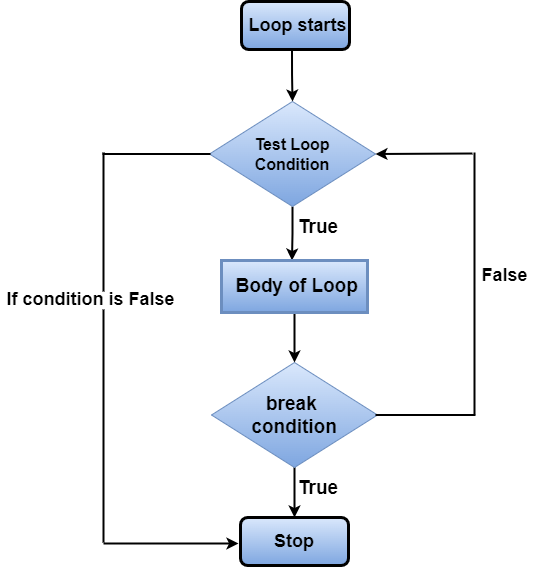

break

break 语句用于立即终止循环。当在循环内部遇到 break 语句时,循环迭代立即停止。通常情况下,我们在使用 if 语句在代码中给出条件后使用 break。

我们可以在任何循环(for、foreach、forever、do-while、while、do-while)中使用 break 语句来终止循环的执行。它总是在循环内部使用。当遇到 break 语句时,它立即结束循环。

流程图:

语法:

break;

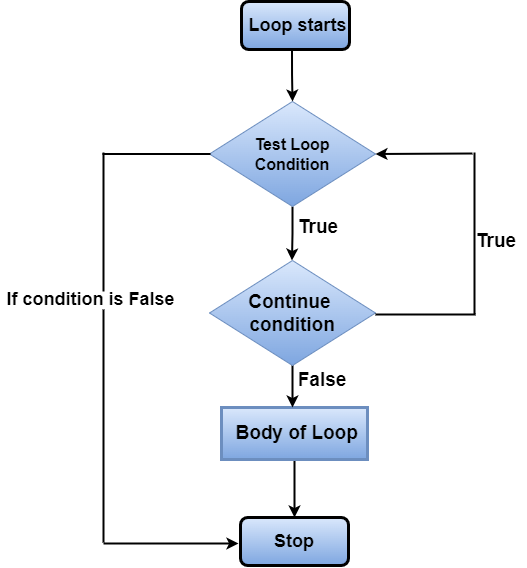

continue

continue 语句用于跳过循环的当前迭代。我们可以在任何类型的循环中使用 continue 语句,比如 for、while 和 do-while 循环。基本上,continue 语句用于在我们想要继续循环但不想执行循环中特定迭代的情况下使用。

使用 continue,我们可以跳过循环的当前迭代,并立即跳转到循环的下一迭代。

流程图:

语法:

continue;