在面试的时候,要在短时间检查一个人的水平,需要面试官有针对性的问些问题,这里举例说一个很能体现FPGA硬件思维的一道面试题。

- if-else及case语句条件判断的优先级

这里先列出几个例子,大家可以先自行判断以下:

example1

go

module test_ex1(

input a,b,c,d,sel0,sel1,sel2,sel3,

output reg z

);

always @(a or b or c or d or sel0 or sel1 or sel2 or sel3)

begin

z=0;

if (sel0) z=a;

if (sel1) z=b;

if (sel2) z=c;

if (sel3) z=d;

end

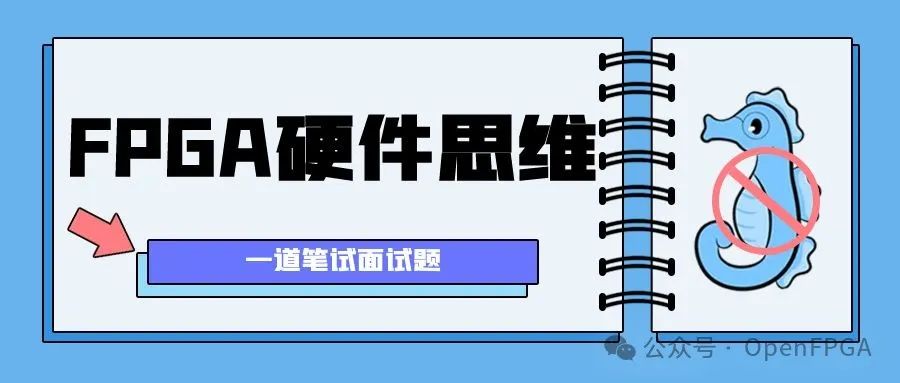

endmodule 图1:example1

图1:example1

example2

go

module test_ex2(

input a,b,c,d,sel0,sel1,sel2,sel3,

output reg z

);

always@(a or b or c or d or sel0 or sel1 or sel2 or sel3)

begin

if(sel0)

z = d;

else if(sel1)

z = c;

else if(sel2)

z = b;

else if(sel3)

z = a;

else

z = 0;

end

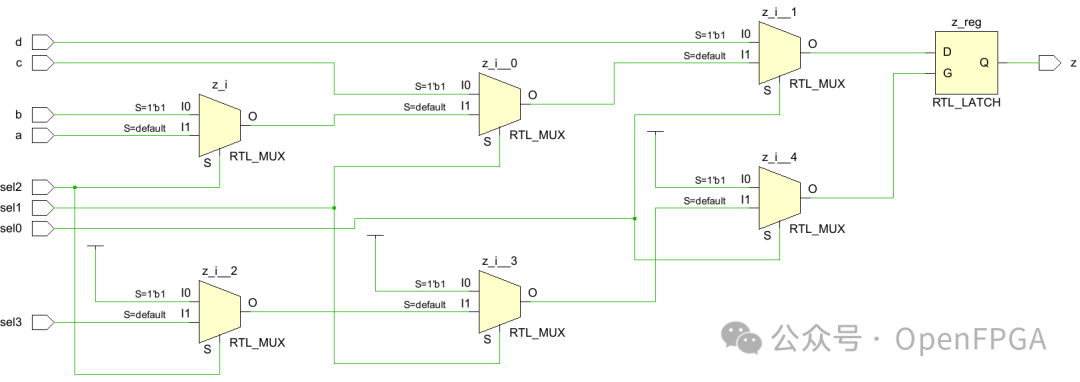

endmodule 图2:example2

图2:example2

example3

go

module test_ex3(

input a,b,c,d,sel0,sel1,sel2,sel3,

output reg z

);

always@(a or b or c or d or sel0 or sel1 or sel2 or sel3)

begin

if(sel0)

z = d;

else if(sel1)

z = c;

else if(sel2)

z = b;

else if(sel3)

z = a;

end

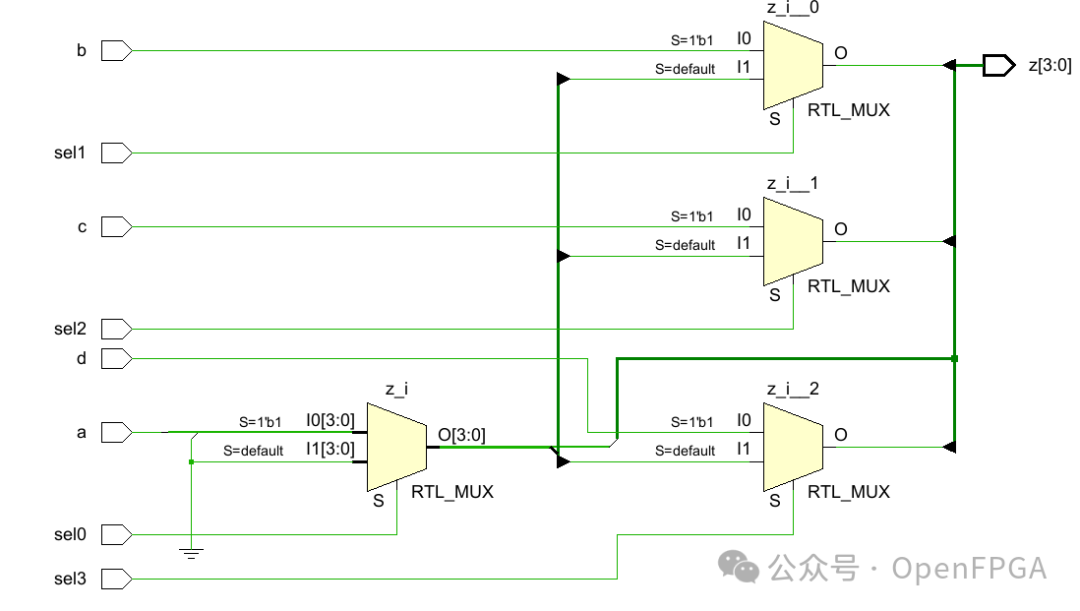

endmodule 图3:example3

图3:example3

example4

go

module test_ex4(

input a,b,c,d,sel0,sel1,sel2,sel3,

output reg [3:0] z

);

always @(a or b or c or d or sel0 or sel1 or sel2 or sel3)

begin

z=0;

if (sel0) z[0]=a;

if (sel1) z[1]=b;

if (sel2) z[2]=c;

if (sel3) z[3]=d;

end

endmodule 图4:example4

图4:example4

example5

go

module test_ex5

#(parameter N=8)

(

input logic [N-1:0] a, b, c, d,

input logic [ 1:0] select,

output logic [N-1:0] y

);

always_comb begin

case (select)

2'b00: y = a;

2'b01: y = b;

2'b10: y = c;

2'b11: y = d;

endcase

end

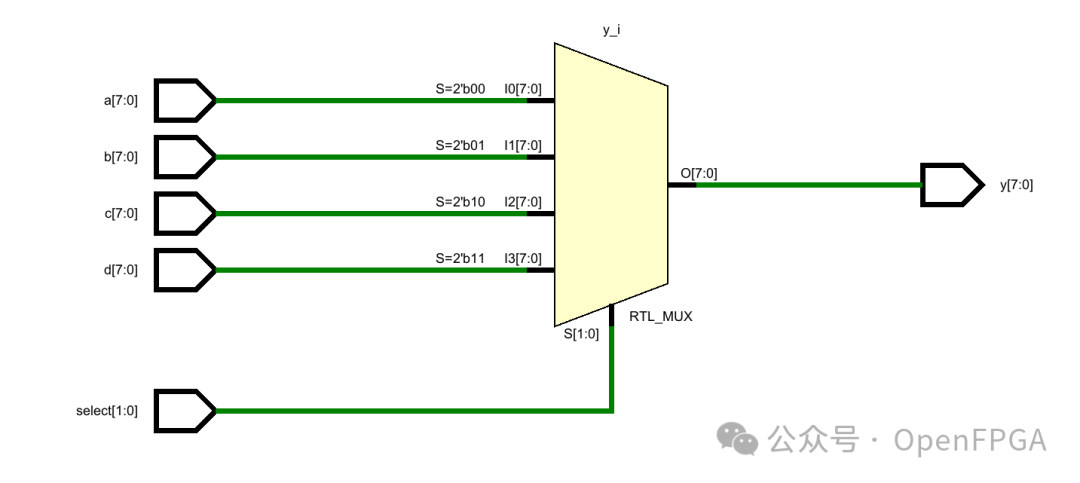

endmodule: test_ex5 图5:example5

图5:example5

example6

go

module test_ex6 (

input logic [3:0] d_in,

output logic [1:0] d_out,

output logic error

);

timeunit 1ns; timeprecision 1ns;

always_comb begin

error = '0;

case (d_in) inside

4'b1???: d_out = 2'h3; // bit 3 is set

4'b01??: d_out = 2'h2; // bit 2 is set

4'b001?: d_out = 2'h1; // bit 1 is set

4'b0001: d_out = 2'h0; // bit 0 is set

4'b0000: begin // no bits set

d_out = 2'b0;

error = '1;

end

endcase

end

endmodule: test_ex6

以上几个示例,大家可以先思考一下每个例子的判断条件优先级,然后再结合电路图对照一下自己的想法对不对。

总结

"if-else的逻辑判别是有优先级的,而case的逻辑判断条件是并列的。"

上面是某些工具书上常见的判断逻辑,也是误导很多新手的结论。

从结果来看判断的优先级不一定是第一个,和后续的书写语句有很大关系(if有没有else、else条件是否完备、case条件是否完备等)。

其中,case语句可以使用unique、unigue0和priority修饰符进行综合条件限制,但是一般不建议使用,要按照自己的思路去书写"电路"。

最后就是常说的串行或者并行应该指语法判断过程,并非指我们说的电路,实际的判断过程还是用硬件思维去思考。

大家在面试时候遇到或者问过什么问题?欢迎大家评论区留言