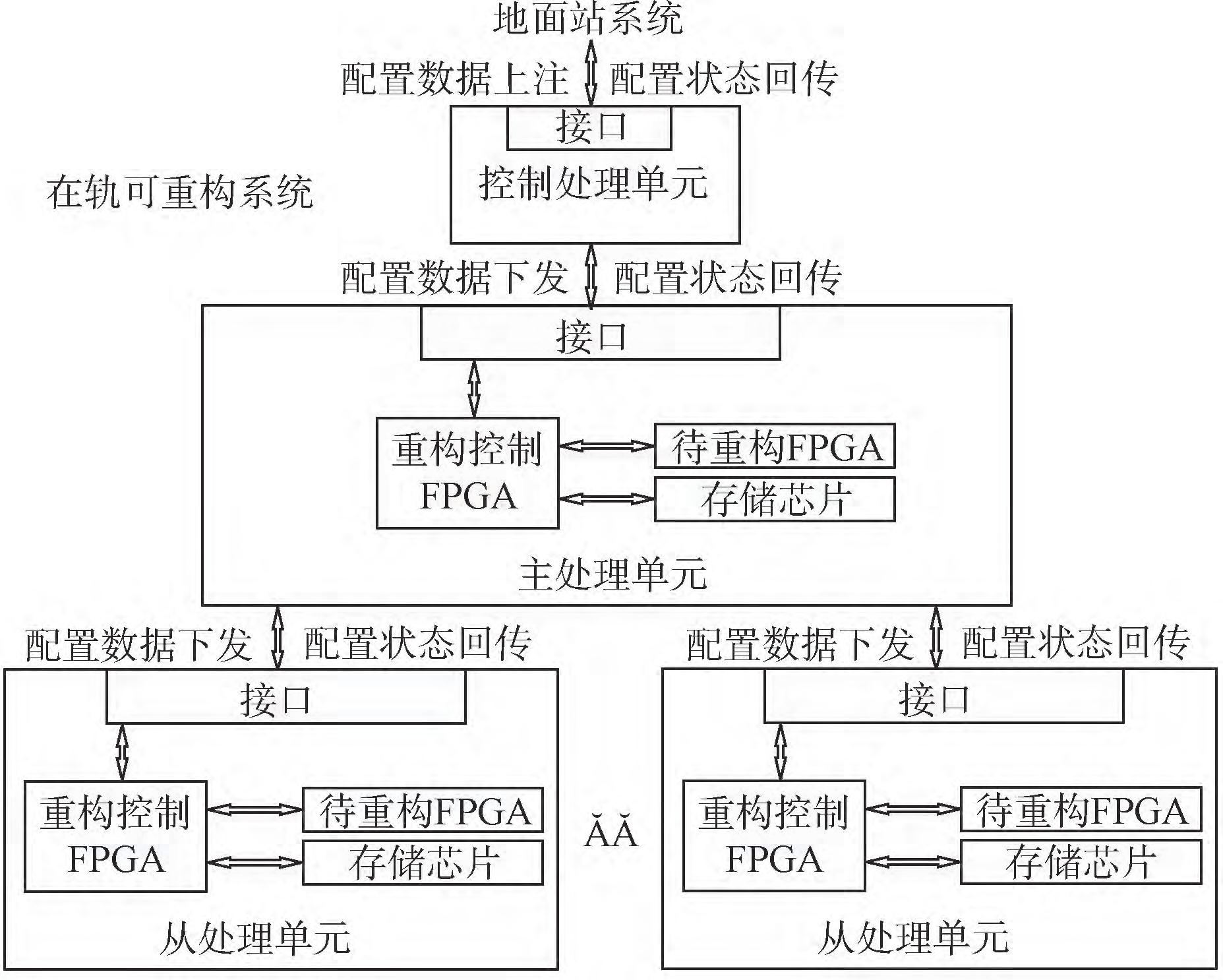

1 在轨可重构系统的构成

在轨可重构系统在不改变在轨设备硬件架构的基础上,首先由地面站系统通过测控上行链路发送配置数据,由航天器设备终端接收配置数据并回传配置状态信息,然后对配置数据进行存储,根据地面需求及配置指令加载配置程序,实现航天器的软件在轨重构功能。在轨可重构系统具备对地面重构数据的接收、解析、存储、分发、配置加载、处理等功能。

在轨可重构系统由三大功能模块构成,分别为控制处理单元、主处理单元和从处理单元。

如下图所示。在轨可重构系统具有模块功能明确、重构模块可扩展、通用性较强的优点。

1.控制处理单元

作为在轨可重构系统的控制中心,负责接收由地面站系统发送的上行配置数据及配置指令,按照通信协议对配置数据及配置指令进行解析校验,校验通过后向下发送给主处理单元,对系统中的各模块进行管理和监控,接收各模块反馈的配置状态信息并向地面站系统回传。

2.主处理单元

主处理单元主要由FPGA、存储芯片等器件构成。作为在轨可重构系统的接口模块,负责接收由控制处理单元发送的配置数据或配置指令,按照模块间通信协议对接收到的数据进行校验。主处理单元本身具备重构功能,接收配置数据后根据协议确定配置数据向下分发至相应的从处理单元或存储在本模块的存储芯片中。接收到本模块配置指令后,执行配置加载,重构主处理单元的功能。主处理单元完成配置加载后,向控制管理单元回传相应的配置成功状态。主处理单元接收到从处理单元的配置加载信息后,向控制处理单元回传。

3.从处理单元

从处理单元主要由FPGA、存储芯片等器件构成。作为在轨可重构系统的终端,负责接收主处理单元下发的配置数据,按照模块间通信协议对接收到的数据进行校验,校验通过后存储至本模块的存储芯片中。接收到配置指令后对从处理单元的待重构FPGA进行配置加载,对从处理单元实现的功能进行重构。从处理单元完成配置加载后,向主处理单元回传相应的配置成功状态信息。

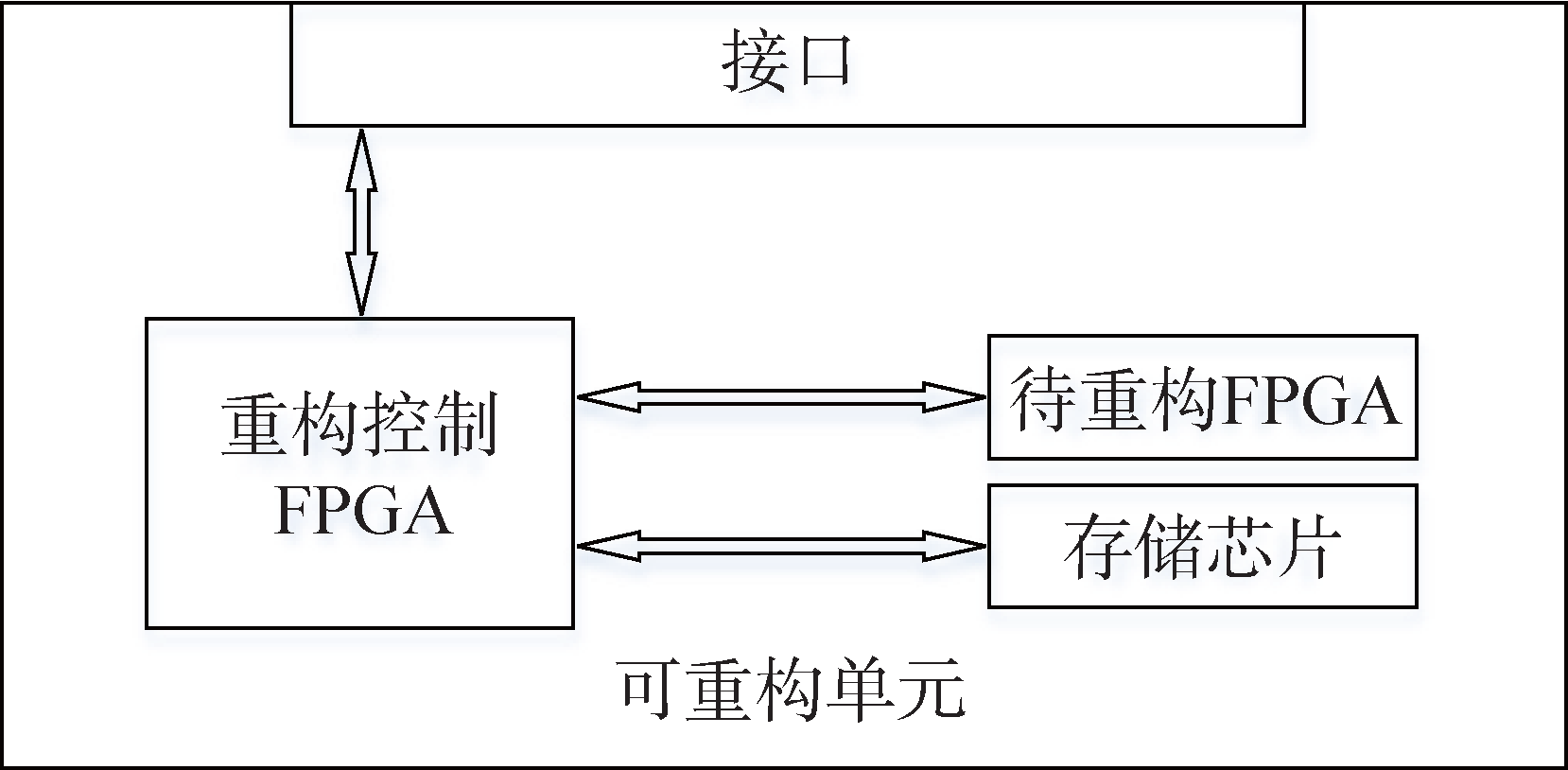

可重构单元的基本结构如下图所示,由两片FPGA和存储配置数据的存储芯片组成。

待重构FPGA一般采用SRAM型FPGA,用于航天器的各种功能实现,是实施在轨重构的对象。重构控制FPGA采用反熔丝FPGA实现,用于为SRAM型FPGA提供配置加载服务。

重构控制FPGA 通过模块间接口接收配置数据,校验通过后将接收到的配置数据存储在存储芯片中。重构控制FPGA通过模块间接口接收到重构指令后,读取存储芯片中相应的配置数据,对SRAM型FPGA进行功能重构,配置完成后,检测SRAM型FPGA的配置结果,并将配置状态返回给上级模块。配置成功后, 在轨功能更改需求实现。

2 在轨重构系统的可靠性

在航天器系统中,由于在轨维护难度大、空间环境恶劣、资源受限等原因,需考虑在轨重构的可靠性,包括重构控制的可靠性和重构数据存储的可靠性。

2.1重构控制的可靠性

目前,航天器上SRAM型FPGA的单粒子防护一般采用"三模冗余+动态刷新"的方式实现,其中动态刷新功能一般由反熔丝FPGA或专用的配置刷新芯片来实现。由反熔丝FPGA实现在轨重构功能可以充分复用现有的硬件结构, 并且反熔丝FPGA对空间辐射不敏感,可以保证在轨重构控制工作的可靠性。

2.2重构数据存储的可靠性

重构数据存储在非易失存储器中,如FLASH、MRAM等类型的存储芯片,需采用高等级且具备一定抗辐照等级的器件。

由于空间单粒子翻转效应,存储数据存在一定的翻转错误概率,因此需要采取数据容错措施。

常用的措施有纠错编译码和三模冗余等。纠错编译码设计可采用RS编译码或EDAC校验码。在存储重构数据时采用纠错编译码,虽然会牺牲存储空间达到存储数据检纠错的目的,但可以最大程度地保证重构数据存储的正确性不受空间单粒子效应的影响。

三模冗余设计是利用三处物理位置存储同一份重构数据,在进行配置时,读取三份重构数据,进行三取二表决, 将表决后的数据对FPGA 进行加载配置。三份重构数据可以并行存储于三片存储芯片中,也可以串行存储于同一芯片的三个不同物理位置处。

第一种存储方式的优势是并行存取效率较高,但需要在硬件设计时布局三个存储芯片;第二种存储方式存取效率低,但节省硬件空间及成本。