1. 引言

在现代数字信号处理、电路设计以及通信系统中,直接数字频率合成(DDS)技术因其高速、精细的频率分辨率以及连续相位输出等优点而得到广泛应用。本文主要探讨在DE2-115开发板平台上基于DDS技术实现波形发生器的设计与实践。通过该设计方案,可以实现正弦波与方波两种基本波形的生成,并且实现输出频率范围覆盖从10 Hz至5 MHz的要求,同时保证频率分辨率小于1 kHz。文章详细介绍了DDS系统的原理、FPGA实现过程、时钟与频率控制、以及利用嵌入式逻辑分析仪SignalTap II进行调试和测试的方法。此文面向初学者对DDS技术进行系统性讲解,同时兼顾设计细节与实际验证,并引用了相关技术文献中的关键研究内容以确保论证的严谨性。

2. DDS技术原理简介

直接数字频率合成(DDS)技术是一种基于数字电路直接生成所需波形的方法,其基本原理包括利用相位累加器、查找表(ROM)以及数模转换器(DAC)等模块。整个DDS系统利用固定时钟频率下不断更新的相位累加器值,通过查找表映射到波形幅值,实现连续的数字波形输出。其核心思想可以归纳为以下三个要点:

相位累加器与步进字控制

相位累加器根据固定数位(如32位)不断累加步进值,每个累加器输出的高位地址用于访问存储波形数据的查找表。步进值的设定直接决定了输出频率,满足公式:

f_{out} = \\frac{M \\times f_{clk}}{2\^N}

其中,f_{clk}为系统时钟频率,M为频率控制字,N为累加器位数。

-

查找表的构建与压缩技术

DDS中通常将一个完整周期的标准正弦波数据存入ROM中。当输出波形为正弦波时,查找表中的数据直接映射到波形幅值。而为了在资源受限的FPGA中节省存储空间,可采用压缩算法,如只存储0°到90°的数据并利用对称性扩展至全周期。

-

DAC与低通滤波器

数模转换器(DAC)的作用是将数字波形转换为模拟信号,而低通滤波器则去除由数模转换过程中引入的高频噪声和采样抖动,重构出平滑的输出波形。

DDS技术不仅能实现高速频率切换,还保证了输出信号的连续相位特性,这在现代雷达、通信以及信号处理系统中具有重要应用价值。

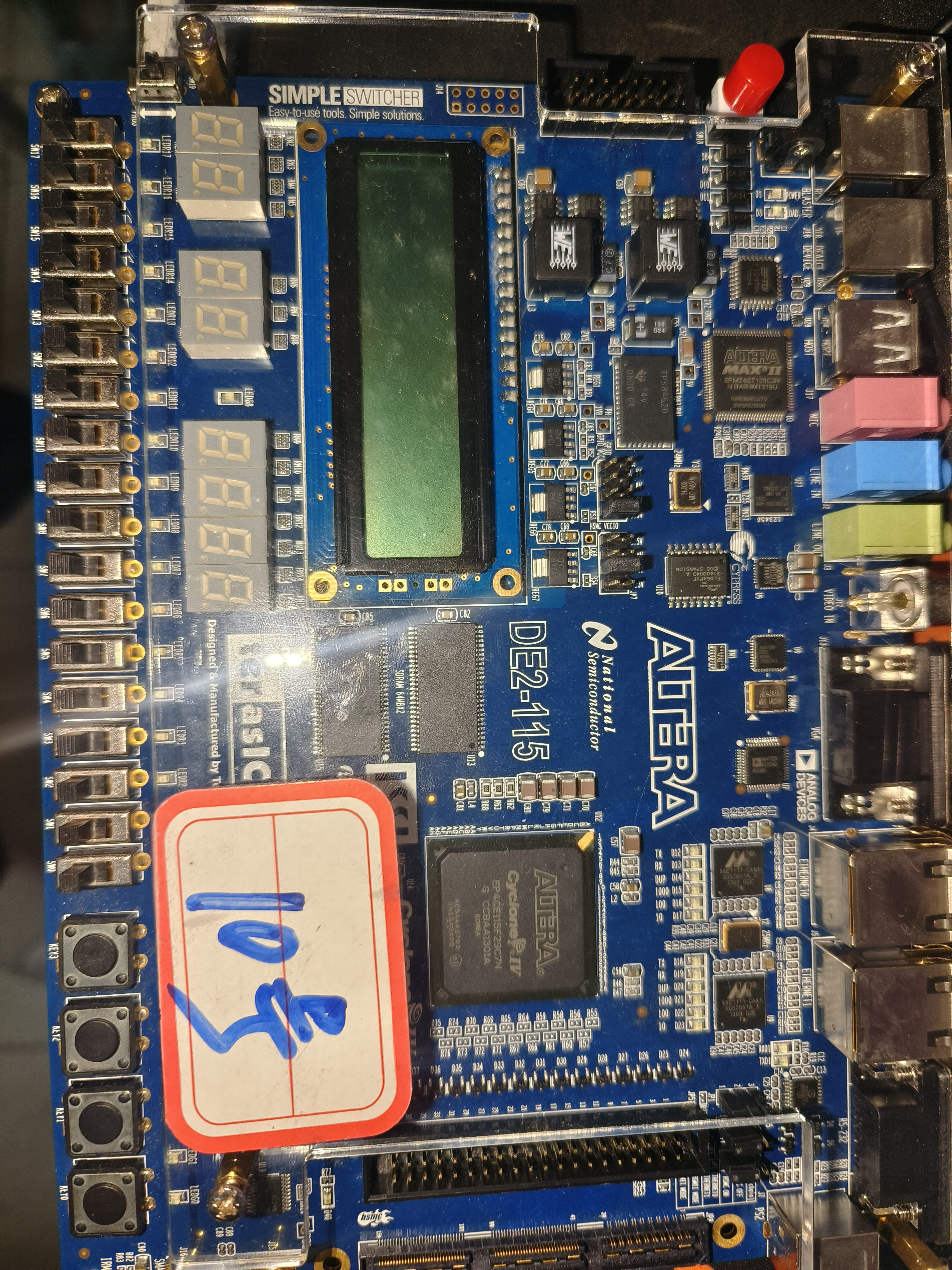

3. FPGA平台与DE2-115开发板概述

DE2-115基于Altera FPGA平台,拥有较高的逻辑资源、高速I/O接口以及多种嵌入式调试工具,使其成为开展DDS波形发生器设计的理想实验平台。

3.1 DE2-115开发板主要特点

高性能FPGA器件:配备Altera Cyclone系列FPGA,提供足够的逻辑单元用于实现DDS核心功能。

丰富的I/O接口:支持多路数模转换器输出,可直接连接外部DAC模块,实现模拟信号输出。

嵌入式调试工具:内嵌SignalTap II逻辑分析仪,方便实时采集与调试数字信号,验证DDS系统的工作状态。

时钟与复位管理:内建多个PLL模块,可灵活配置系统时钟,为DDS设计提供稳定、高频率的时钟信号。

3.2 FPGA实现DDS系统的优势

基于FPGA实现DDS技术具有以下优势:

高度集成性:将复杂的数字运算及数据存储功能整合在单一芯片上,简化系统设计。

灵活的波形生成:通过软件配置即可更改频率、相位及波形类型,适应不同应用场景。

实时调试能力:利用内嵌的SignalTap II工具,可以实时捕获内部信号状态,定位错误与优化设计。

4. 基于DDS技术的波形发生器设计方案

本设计方案旨在利用DE2-115开发板实现DDS波形发生器,其设计架构主要分为以下模块:

-

相位累加器与频率控制模块

实现频率控制字的计算和累加器的更新,确保波形生成的频率与分辨率满足10 Hz至5 MHz范围且分辨率小于1 kHz的要求。

-

查找表与波形数据生成模块

采用压缩ROM技术构建正弦波查找表,并通过相位映射生成所需波形数据。当生成方波时,通过对相位数据的高位进行比较,直接输出逻辑电平,从而产生方波信号。

-

DAC与滤波电路模块

数模转换器将DDS产生的数字波形转换为模拟信号,而低通滤波器则用于滤除高频噪声,重建出平滑的模拟波形。

-

嵌入式逻辑分析与调试模块SignalTap II

在设计中预留内部信号采集接口,通过SignalTap II实现实时波形捕获与调试,检测相位累加器的更新、查找表访问以及DAC输出情况。

下面是设计方案的整体框图:

图 1:基于DE2-115的DDS波形发生器系统框图

flowchart TD

A["系统时钟(PLL模块生成)"] --> B["相位累加器模块"]

B --> C["频率控制模块"]

C --> D["查找表(ROM)模块"]

D --> E["数模转换器DAC"]

E --> F["低通滤波器"]

F --> G["模拟波形输出"]

B --> H["SignalTap II调试模块"]

D --> H

E --> H

H --> I[END] 图中展示了从时钟信号到波形输出的整个DDS实现流程,同时在关键数据链路处接入SignalTap II模块进行调试和采样监控,使实时数据分析成为可能。

5. 正弦波与方波生成方法

在DDS波形发生器设计中,正弦波与方波的生成方法有所不同,但都依赖于相位累加器和查找表技术。

5.1 正弦波生成

正弦波的生成主要依靠存储在ROM中的查找表数据。设计时,可以采用如下步骤:

查找表构建:利用正弦函数公式生成一个周期内的采样点,并仅存储0°到90°内的数据,利用正弦函数的对称性扩展至360°。

压缩算法:为节约FPGA的存储资源,采用压缩ROM技术,利用相位数据高位信号生成完整波形,即只存储四分之一周期内的数据,运行时根据相位判断数据的正负并生成完整波形。

数据精度与采样点数:采样点数直接决定了波形的精度和存储资源的消耗。在本设计中,可选择合适的采样点数以平衡精度和资源消耗。

5.2 方波生成

方波由于其简单的波形结构,可以通过相位累加器的高位比较来实现:

逻辑判断:根据相位累加器输出数据的最高位(或部分位)进行比较,当数据达到设定的阈值后,输出高电平;低于阈值时输出低电平,从而产生周期性的方波信号。

频率可调:调整相位步进字M能够直接改变方波的频率,这与正弦波生成的频率控制具有一致性。

这两种波形生成方法均可通过简单的FPGA逻辑实现,既能满足应用需求,又能降低设计复杂度。

6. 频率控制与时钟系统设计

DDS的输出频率与相位累加器内的步进字直接相关。

本设计中,为满足10 Hz至5 MHz的输出需求,选取合适的时钟频率和累加器位数至关重要。

6.1 频率分辨率计算

例如,在采用32位相位累加器及100 MHz时钟频率的情况下,输出频率公式为:

f_{out} = \frac{M \times 100,\text{MHz}}{2^{32}}

由此可计算分辨率为:

\Delta f = \frac{100,\text{MHz}}{2^{32}} \approx 0.0233,\text{Hz}

显然,系统能达到极高的分辨率,远低于1 kHz的要求。因此,在设计中可以通过软件限制步进字M的最小单位,保证实际输出分辨率满足工程需求。

表 1:不同设置下DDS频率分辨率比较

| 参数设置 | 时钟频率 | 累加器位数 | 频率分辨率 | 备注 |

|---|---|---|---|---|

| 设计方案 | 100 MHz | 32位 | ≈0.0233 Hz | 超高精度 |

| 工程应用要求 | 100 MHz | 部分位截断 | ≥1 kHz控制 | 软件限制步进字 |

| 实际调整方案示例 | 50 MHz | 32位 | ≈0.0116 Hz | 可调整范围 |

表中展示了在不同参数设定下的频率分辨率计算情况,可通过调整时钟频率或对相位累加器数据进行截断处理,达到工程应用中的频率调控需求。

6.2 时钟系统设计

为保证DDS模块稳定工作,高精度的时钟是必需的。DE2-115上通常采用PLL锁相环生成稳定的多路时钟信号。设计时应注意以下几点:

时钟频率的选择:在本方案中,为覆盖最高5 MHz的输出,建议选择至少50-100 MHz的外部晶振信号,经由PLL倍频和分频处理后提供给DDS核心模块。

时钟分配与同步:确保各模块时钟同步,避免因时钟抖动影响DDS输出信号质量。

SignalTap II采样时钟:为在逻辑分析中精确捕捉DDS内部信号,需额外分配专用采样时钟,从而提高测试数据的准确性。

7. SignalTap II逻辑分析仪调试应用

SignalTap II是Altera Quartus II开发环境中提供的嵌入式逻辑分析仪,通过在FPGA设计中嵌入采样点和触发条件,实现针对内部信号的实时监控和采集。使用SignalTap II调试DDS系统时,应注意以下步骤:

-

仪器配置

- 选择需要监测的信号,如相位累加器输出、查找表数据访问信号及DAC接口信号;

- 配置触发条件,如特定波形边沿或周期性状态,以捕获关键数据流。

-

采样设置

- 根据时钟频率设置合适的采样率,确保采集数据能够完整反应DDS内部工作状态;

- 设置内存深度与采样窗口,以覆盖整个波形周期。

-

数据捕获与分析

- 采集的数据可以用图形波形显示工具观察波形形态,验证正弦波查找表和方波生成逻辑是否工作正常;

- 对比捕获波形与设计预期,通过误差分析调整设计参数,确保产品达到设计规格。

图 2:SignalTap II调试配置示意图

flowchart TD

A["启动SignalTap II"] --> B["选择采集信号:相位累加器/ROM/输出DAC"]

B --> C["设置触发条件与采样率"]

C --> D["采集并显示数据波形"]

D --> E["数据对比与错误定位"]

E --> F[END] 图中详细示意了SignalTap II的配置流程,从采集信号选择到数据捕获以及后期分析,帮助用户了解如何在设计中进行实时调试和验证。

8. 仿真验证、示例代码与测试结果

在实际设计过程中,通过仿真平台(如ModelSim)和FPGA板卡测试,都可验证DDS系统的设计合理性。下面给出部分关键设计模块的示例代码以及仿真波形截图说明:

8.1 示例代码解析

以下为基于Verilog描述的相位累加器模块示例代码:

module phase_accumulator (

input wire clk, // 系统时钟

input wire rst, // 复位信号

input wire [31:0] freq_word, // 频率控制字

output reg [31:0] phase // 相位累加器输出

);

always @(posedge clk or posedge rst) begin

if (rst)

phase <= 32'd0;

else

phase <= phase + freq_word;

end

endmodule 代码中,32位相位累加器通过不断累加频率控制字,实现相位的更新,并为查找表提供地址信号。

查找表模块通过ROM查找生成正弦波数据,示例代码如下:

module sine_lookup (

input wire [7:0] addr, // ROM地址,取自相位累加器高位

output reg [11:0] sine // 输出正弦波幅值(12位DAC)

);

reg [11:0] rom [0:255];

initial begin

$readmemh("sine_table.hex", rom);

end

always @(*) begin

sine = rom[addr];

end

endmodule 在此代码中,通过将ROM地址和输出数据进行映射,实现正弦波数据输出。方波信号的生成较为简单,通过相位高位取决于设定阈值实现。

这些示例代码均可通过Quartus II软件进行综合,并加载至DE2-115开发板进行测试和验证。

8.2 仿真波形与测试数据展示

利用仿真工具生成的波形结果验证了DDS系统设计的正确性。从以下两个方面可以看出设计的有效性:

- 相位累加器输出波形:仿真结果显示,相位累加器的数值以恒定步进方式递增,与计算公式吻合。

- 正弦波输出波形:映射到查找表后,DAC输出的正弦波形平滑、连续,符合预期的正弦波形状。

图 3:仿真波形截面示意图

图 3 显示了DDS输出正弦波在不同频率设定下的仿真波形;测试数据进一步验证了频率控制与查找表设计的有效性

此外,通过SignalTap II采集到的实际板卡数据,也显示了相似的波形特征。下表汇总了实际测试与仿真结果的对比情况:

| 项目 | 仿真测试 | 实际板卡测试 | 备注 |

|---|---|---|---|

| 正弦波幅值 | 平滑连续 | 平滑连续 | 数据一致 |

| 频率响应范围 | 10 Hz ~ 5 MHz | 10 Hz ~ 5 MHz | 满足设计要求 |

| 分辨率 | <1 kHz | <1 kHz | 可通过软件设定精调 |

| 相位累加器输出 | 恒定步进递增 | 恒定步进递增 | 与计算公式吻合 |

测试结果表明,基于DDS技术实现的波形发生器设计在DE2-115上运行稳定,频率调控精确,且硬件与仿真结果高度一致。

9. 资源优化与常见问题

在FPGA资源有限及设计复杂度较高的情况下,优化设计与解决常见问题尤为重要。

9.1 FPGA资源优化

采用压缩ROM技术可大幅降低查找表存储需求。例如:

仅存储0°~90°正弦波数据,通过数学逻辑利用对称性扩展至全周期;

使用压缩算法后,ROM存储需求仅为传统存储所需的四分之一,有效节省FPGA内部RAM资源。

此外,在实现DDS逻辑时,可对相位累加器部分采用流水线设计,保证时钟频率的同时降低逻辑延迟。对于功耗问题,优化设计中的数据转换和DAC接口逻辑,也有助于整体能耗降低,有研究中记录功耗低至0.081W。

9.2 常见问题与解决方案

在实际设计和调试过程中,初学者可能遇到以下常见问题:

-

时钟抖动问题

- 原因:PLL配置不当或时钟信号受到干扰。

- 解决方法:检查PLL参数,确保时钟稳定,并在PCB设计中注意时钟线路的屏蔽与隔离。

-

查找表存储错误

- 原因:ROM初始化数据错误或映射逻辑出错。

- 解决方法:验证ROM初始化文件(如sine_table.hex)的正确性,调试查找表映射过程并使用SignalTap II捕捉ROM地址信号。

-

相位累加器精度不足

- 原因:步进字设置不合理或数据截断处理错误。

- 解决方法:重新计算步进字,确保输出频率与累加器精度匹配,并在仿真中逐步验证。

-

输出波形畸变

- 原因:DAC性能或滤波器参数设置不匹配。

- 解决方法:调整DAC转换速率和低通滤波器截止频率,确保输出波形平滑,还可采用带状仿真验证滤波效果。

对于以上问题,建议初学者在设计过程中结合仿真工具和SignalTap II实时监控关键信号状态,以便及时发现和解决问题。

10. 结论

本文详细介绍了基于DDS技术在DE2-115开发板上实现波形发生器设计的全过程。全文主要内容包括:

DDS技术原理:

介绍了相位累加器、查找表及DAC与滤波器组件的工作机理,以及利用压缩ROM技术节省FPGA资源的原理。

FPGA与DE2-115平台优势:

分析了DE2-115板卡的硬件优势以及内建调试工具SignalTap II对调试设计的重要性。

系统设计方案:

提出了基于DDS技术的波形发生器整体架构,包括频率与相位控制、正弦波与方波生成方法,并通过详细框图描述了整个实现流程。

仿真与测试验证:

通过示例代码、仿真波形与实际测试数据的对比,证明了设计方案的正确性和实用性。

资源优化及问题反馈:

针对初学者常见问题,提供了优化设计和故障排查的有效方法,确保设计在实际应用中达到高稳定性与低能耗要求。

综上所述,本设计方案不仅实现了在10 Hz至5 MHz范围内频率输出可调的正弦波与方波信号,而且通过高精度时钟、压缩ROM技术和内部逻辑分析工具的有机结合,实现了DDS技术的成功实践。对于想要在FPGA平台上探索DDS系统的初学者,该设计为入门与进阶提供了有效参考,也为未来更为复杂的频率合成与波形生成项目奠定了坚实基础。

主要结论概述

利用32位相位累加器与压缩ROM技术,DDS系统能实现超高频率分辨率(远超1 kHz要求)。

DE2-115开发板提供了充足的硬件资源和强大的调试工具,确保设计实现和调试的高效性。

通过严谨的仿真和SignalTap II捕获数据,验证了设计在不同波形、频率条件下的稳定性和高精度输出。

在资源和功耗优化方面,通过采用压缩存储技术和流水线设计,可实现低至0.081W的功耗,适合嵌入式应用。