简介:使用DDS波形发生器可以在fpga上生成方波、正弦波等波形,其具体方法是计算相位的变化,然后根据数据表的数值进行数模转化改变波形。

DDS的第一步是生成一个相位加法器

相位加法器

在生成一个波,例如正弦波时,我们要设定波发生的频率,例如一个正弦波为1hz,也就是一秒钟发生一次。

在确定了波的发生频率后,由于fpga是数字电路,我们需要将数字转化为波形,这就需要借助数模转化将数值和一个数值表进行比较(这个数值表中每个数值都对应一个电压,如果表中的数值和需要转化为波形的数值相等,那么就输出这个电压),依靠这样的方法就可以实现数模转换。

由于这个表保存的数据是离散的再加上芯片处理数据时每次计算都有时间间隔,所以我们将一个波均分为很多小点,最后将这些小点连起来就相当于一个连续的波形了。

相位加法器即可判断在波的一个周期内需要分多少个小点以及波的频率。

我们用verilog代码实现,下面代码通过改变输入K的值即可改变每个点的频率,K取值应该小于myAdd寄存器最大值,当myAdd寄存器溢出时它的所有位都会变为0,利用这种特性我们就实现了波的重复生成。

为什么要用myRom取myAdd的前10位,这是因为myAdd的位数乘上每次时钟消耗时间为每次波一个周期时间,但是其中有17位数据,如果我们每个数据都拿来生成点所消耗的资源太多了,只取高位然后等低位不断进位会大大降低资源消耗,虽然这样每个点的间隔变大了,但是实际生成波形效果还是非常好(奈奎斯特准则)。

cpp

module ph_adder (

input clk,

input [12:0] K, //K取最大值时,波的频率大概5Mhz

output reg [9:0] myRom,

output reg [16:0] myAdd

);

always @(posedge clk) begin

myAdd <= myAdd + K;

myRom <= myAdd[16:7]; //myAdd的低位每次进位后,myRom加1

end

endmodule方波发生器

在生成波时,我们需要知道每个点对应的值,我们可以将该值放在寄存器中或者使用脚本将该值导入寄存器中。为了简单体现效果,我这里使用了方波发生器,因为方波的点对应的数值只有两种即0、1。

cpp

module sq_wave (

input clk,

input Rst,

input [16:0] myAdd,

output reg [11:0] sq

);

always@(posedge clk)begin

if(!Rst)

sq=0;

else begin

if(myAdd<=17'h0FFFF)//第一位为0,相当于把地址平分为2半

sq=12'hFFF;

else

sq=0;

end

end

endmodule100Mhz锁相环

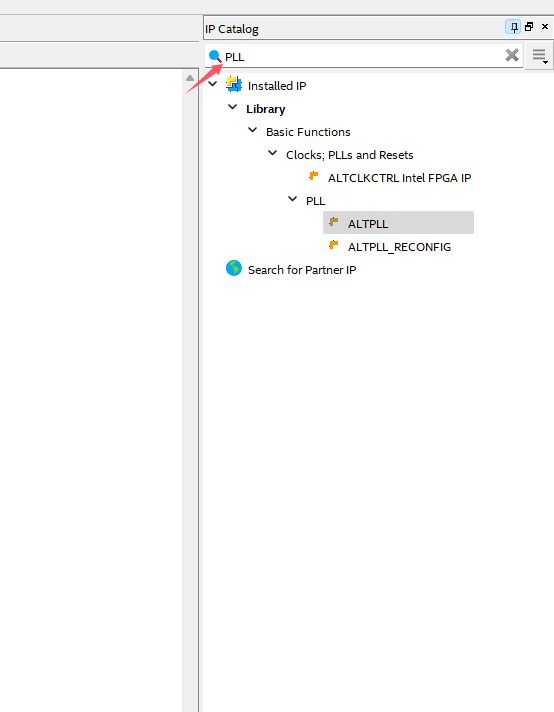

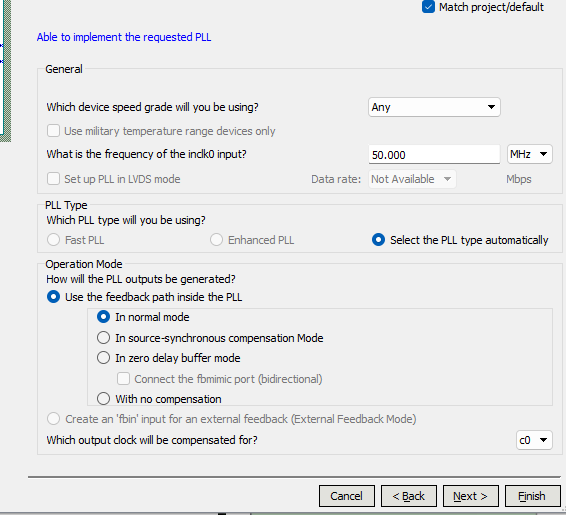

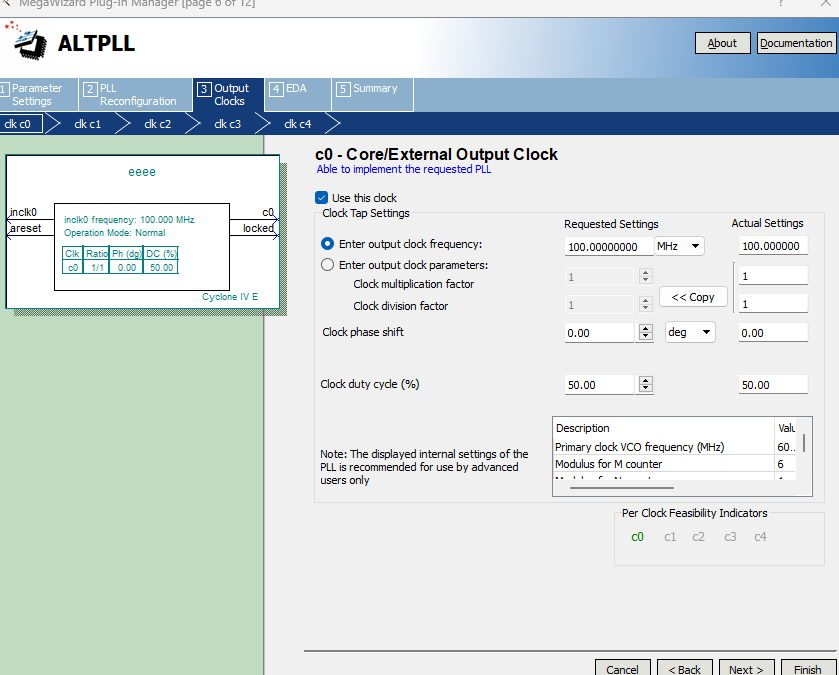

由于我的时钟频率是50mhz,我想得到100Mhz的波形,通过在quartus上调用IP核即可实现。

按照上述图片所示配置即可。

顶层模块设计

依次调用模块即可。

cpp

module DDS_top (

input clk_50,

input Rst,

input [12:0] K,

output [11:0] sq, //方波输出值

output LED

);

wire clk_100;

PLL PLL_inst(

.inclk0 (clk_50),

.c0 (clk_100),

.locked (LEDG)

);

wire [16:0] myAdd;

wire [9:0] myRom;

ph_adder ph_adder_inst(clk_100,K,myRom,myAdd);

sq_wave sq_wave_inst(clk_100,Rst,myAdd,sq);

endmodule仿真模拟实验

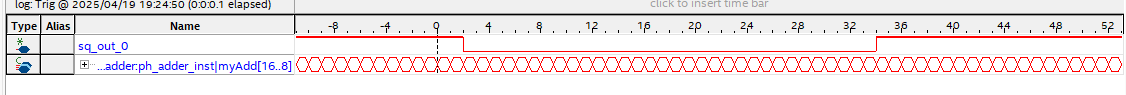

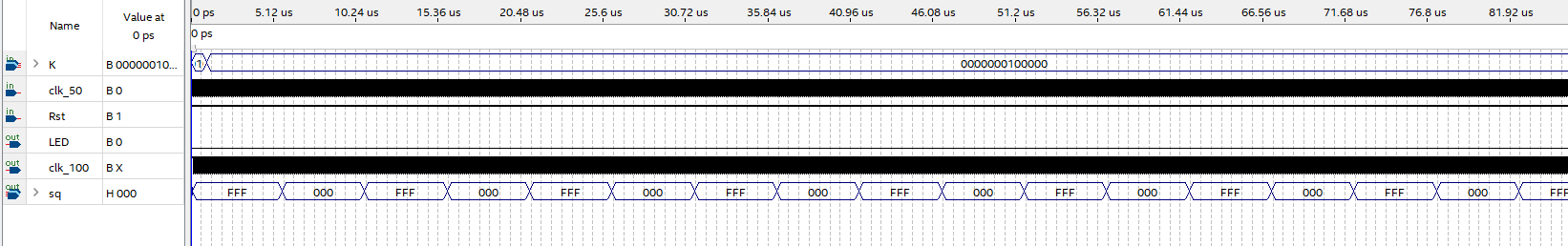

1.在quartusII中新建vmf文件,调节波的取值,实验效果如下

2.使用quartusII中的逻辑分析仪,配置好引脚选择观察的寄存器,实验效果如下