文章目录

- [1 概述](#1 概述)

- [2 结构图](#2 结构图)

1 概述

Video In to AXI4-Stream IP核的核心作用是将符合传统时序标准(如BT.656/BT.1120)的并行视频输入信号,高效转换为AXI4-Stream视频流。作为FPGA视频处理流水线的"入口网关",它剥离消隐数据、转换同步信号,输出标准化的流数据,供后续图像处理或DMA模块使用。

Video In to AXI4-Stream IP核具有以下特性:

- 视频输入 (Video input): 支持带时钟的并行视频数据及同步信号 - 有效视频数据可伴随同步信号 (syncs)、消隐信号 (blanks) 或两者兼有 (both);

- AXI4-Stream 主接口 (AXI4-Stream master interface): 提供符合 AXI4-Stream 标准的输出主接口;

- 与 Xilinx 视频时序控制器接口 (Interface to Xilinx Video Timing Controller): 可与 Xilinx 视频时序控制器 (VTC) 核连接,用于检测视频时序;

- 支持共同时钟或独立时钟模式 (Support for common or independent clock modes): AXI4-Stream 时钟域和视频输入时钟域可工作在共同时钟或独立时钟模式下;

- 可选 FIFO 深度 (Selectable FIFO depth): FIFO 深度可在 32 至 8192 个存储单元 (locations) 之间选择;

- 可选输入数据宽度 (Selectable input data width): 输入数据总线宽度可在 8 至 256 位之间选择;

- 支持隔行扫描操作 (Support for interlaced operation): 能够处理隔行扫描视频信号;

- 分量位宽转换 (Component width conversion): 支持 8、10、12 和 16 位视频分量 (如 Y, Cb, Cr) 的位宽转换。

2 结构图

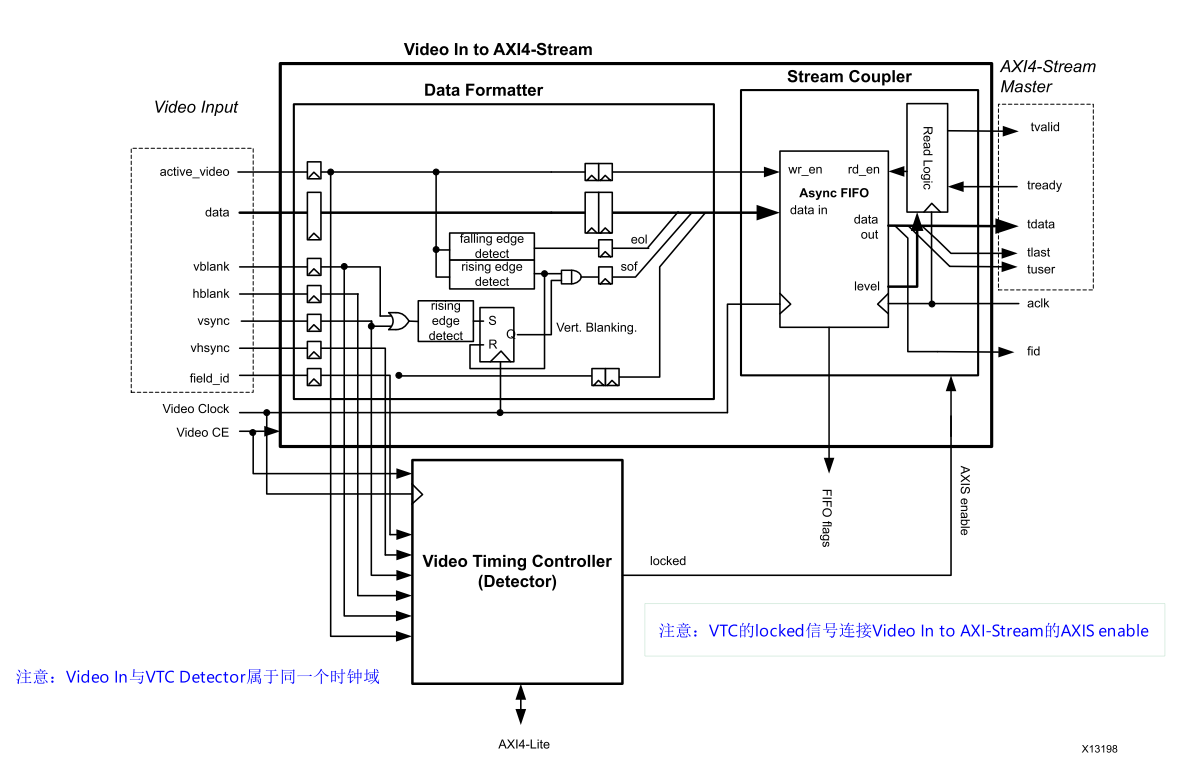

Video In to AXI4-Stream IP核原理框图如下图所示:

- 并行视频输入接口:包括

- 并行视频数据

- 像素时钟

- 时序信号:Xilinx支持以下三种时序信号组合

- Vsync + HSync + Data Valid

- Vblank + Hblank + Data Valid

- Vsync + HSync + Vblank + Hblank + Data Valid

- AXI4-Stream视频流接口:包括

- 握手信号:tvalid和tready

- 像素数据:tdata

- 行结束(EOL):tlast

- 帧起始(SOF):tuser

- 异步FIFO:

- 处理视频输入时钟域与 AXI4-Stream 时钟域之间的异步数据传输

- 深度和位宽可配置

- 与VTC(Video Timing Controller IP核)协同工作:

- Video In to AXI4-Stream IP核将输入视频的时序信号透传(pass-through)给VTC

- VTC对输入的时序信号进行检测,并产生"locked"状态信号

- VTC输出的"locked"状态信号与Video In to AXI4-Stream IP核的AXIS enable输入连接,控制Stream Coupler模块是否工作

- 目的:确保在输入视频的时序稳定后,AXI4-Stream才开始输出。