随着器件等级的升高,高速serdes的线速率也随之提高,RFSOC 4x最大可支持100G,主流方案为RDMA方案,该方案相对比较复杂,除了需要负责逻辑端的开发,还需操作系统中开发RDMA的驱动,对于对丢包不那么敏感的场景可考虑UDP方案;

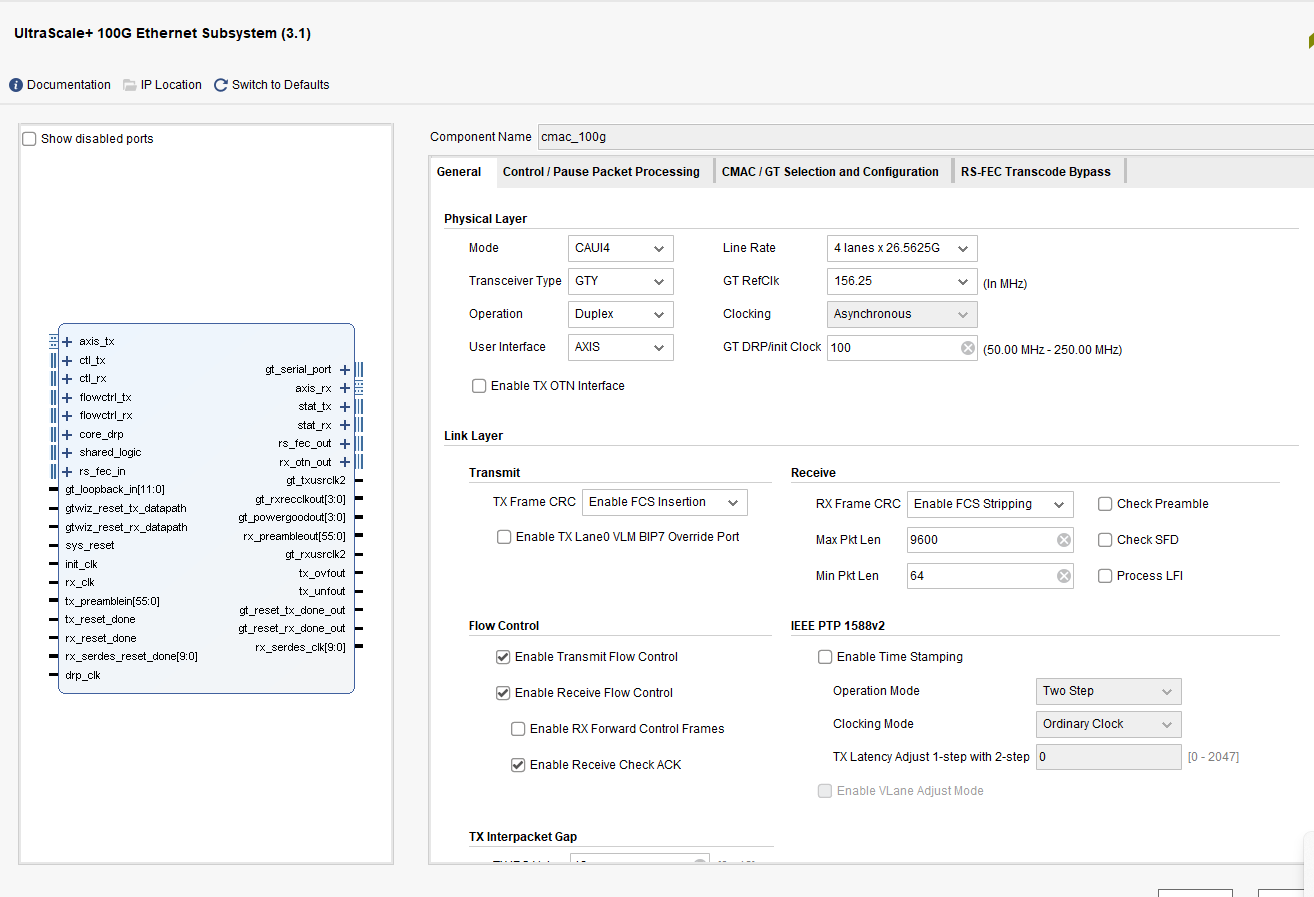

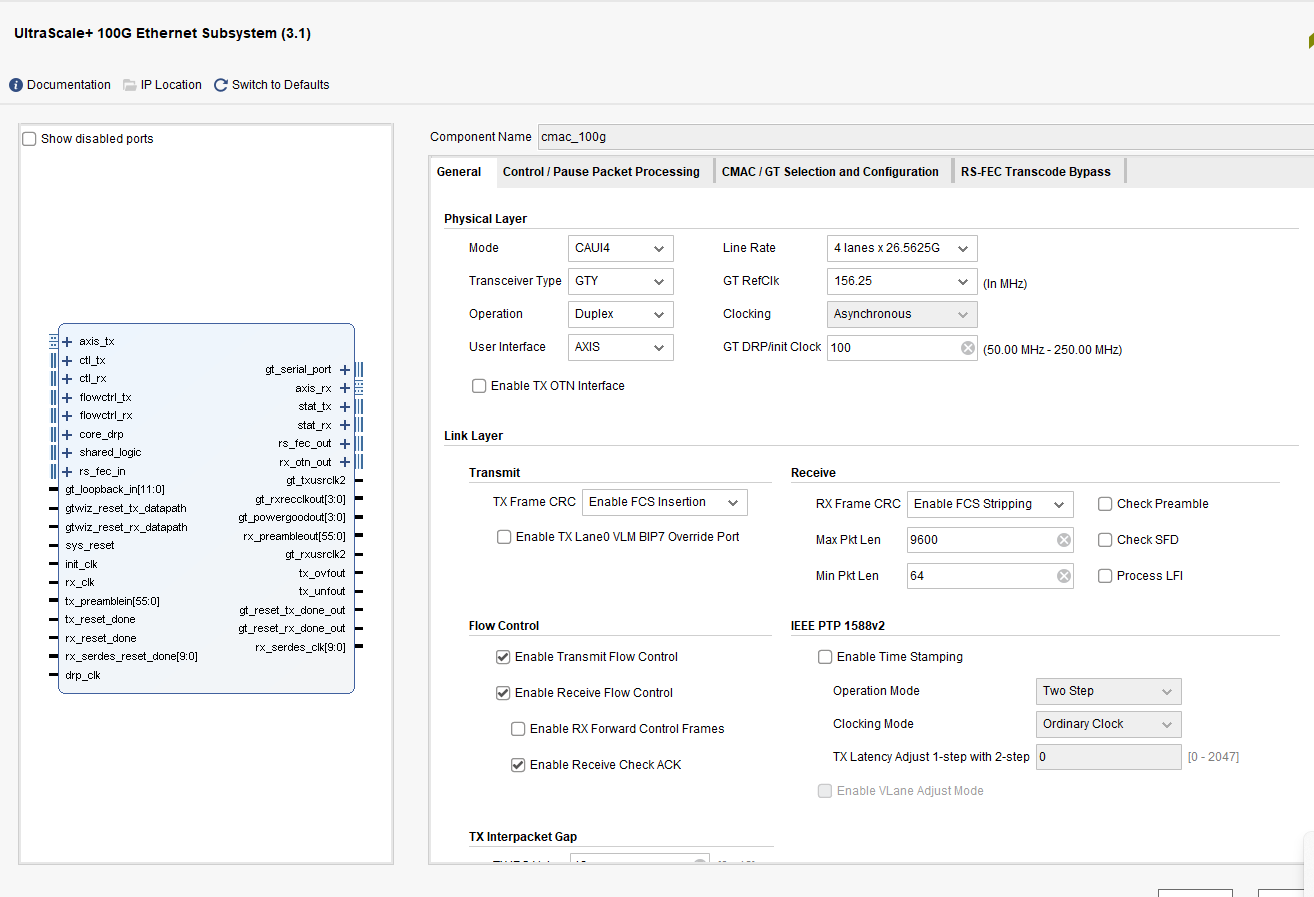

系统搭载xilinx公司的CMAC具体配置如下

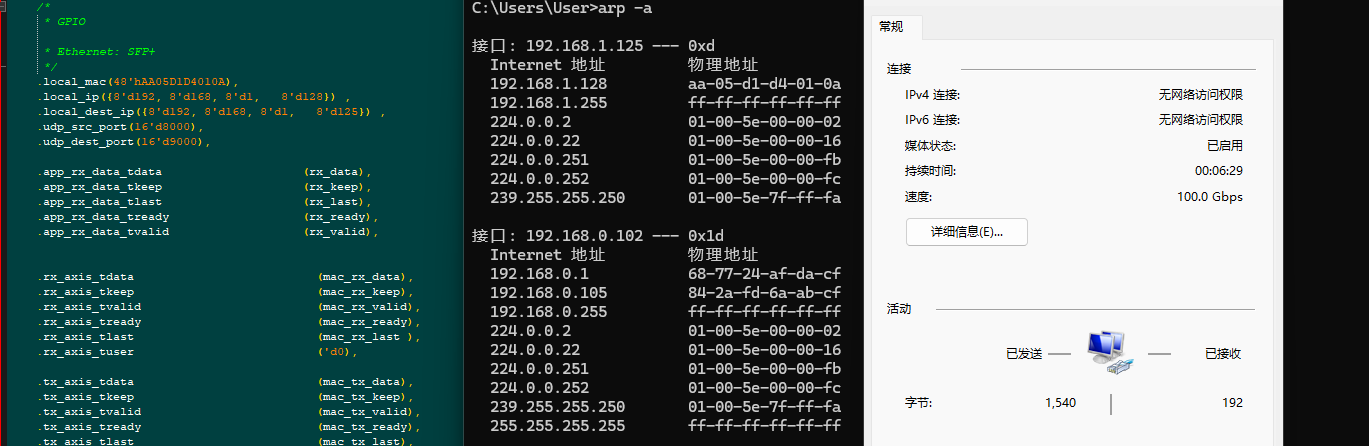

协议栈方面相比10G,主要就是通讯位宽从64BIT升级到512BIT,封包需要重新修改

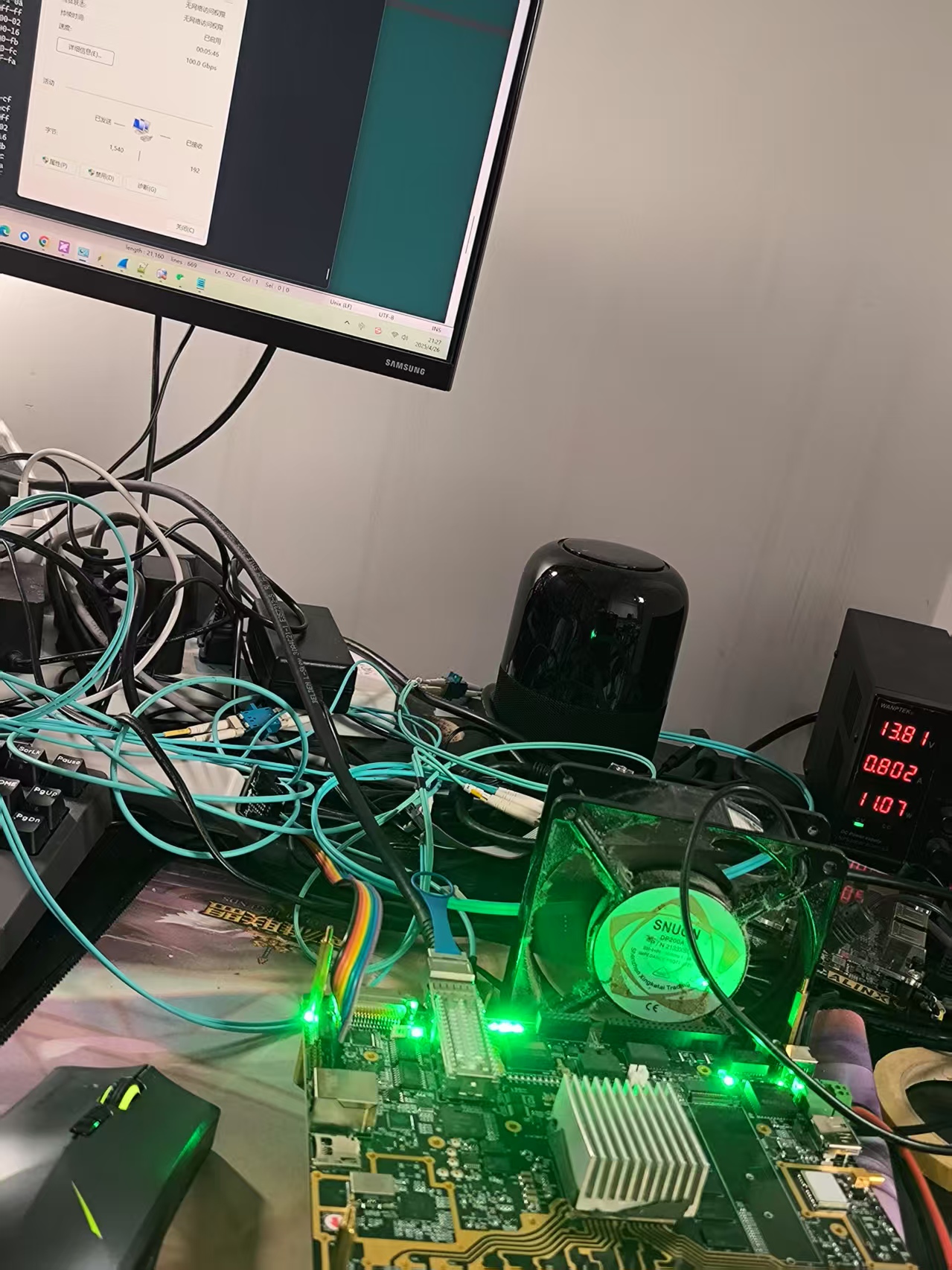

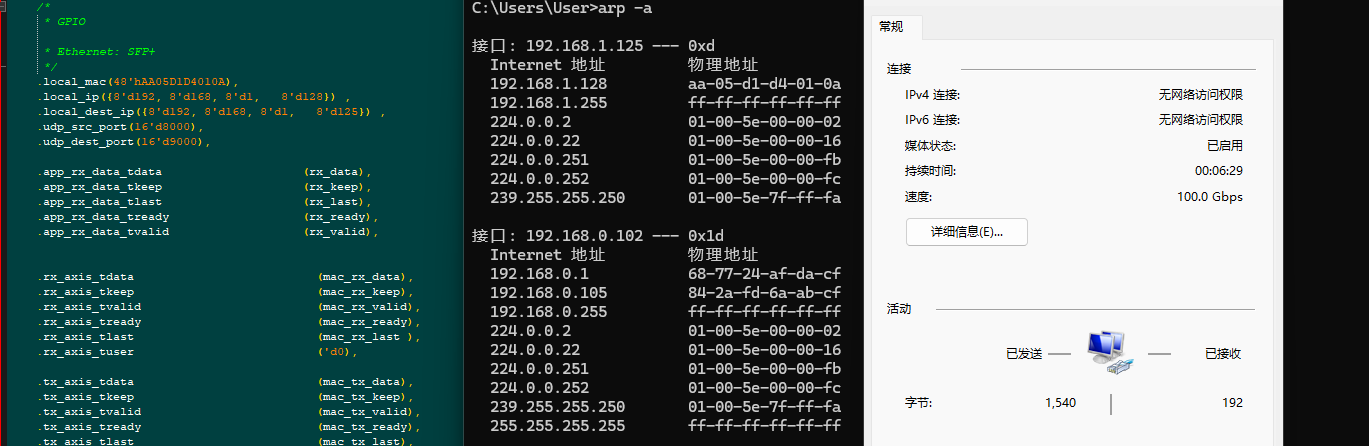

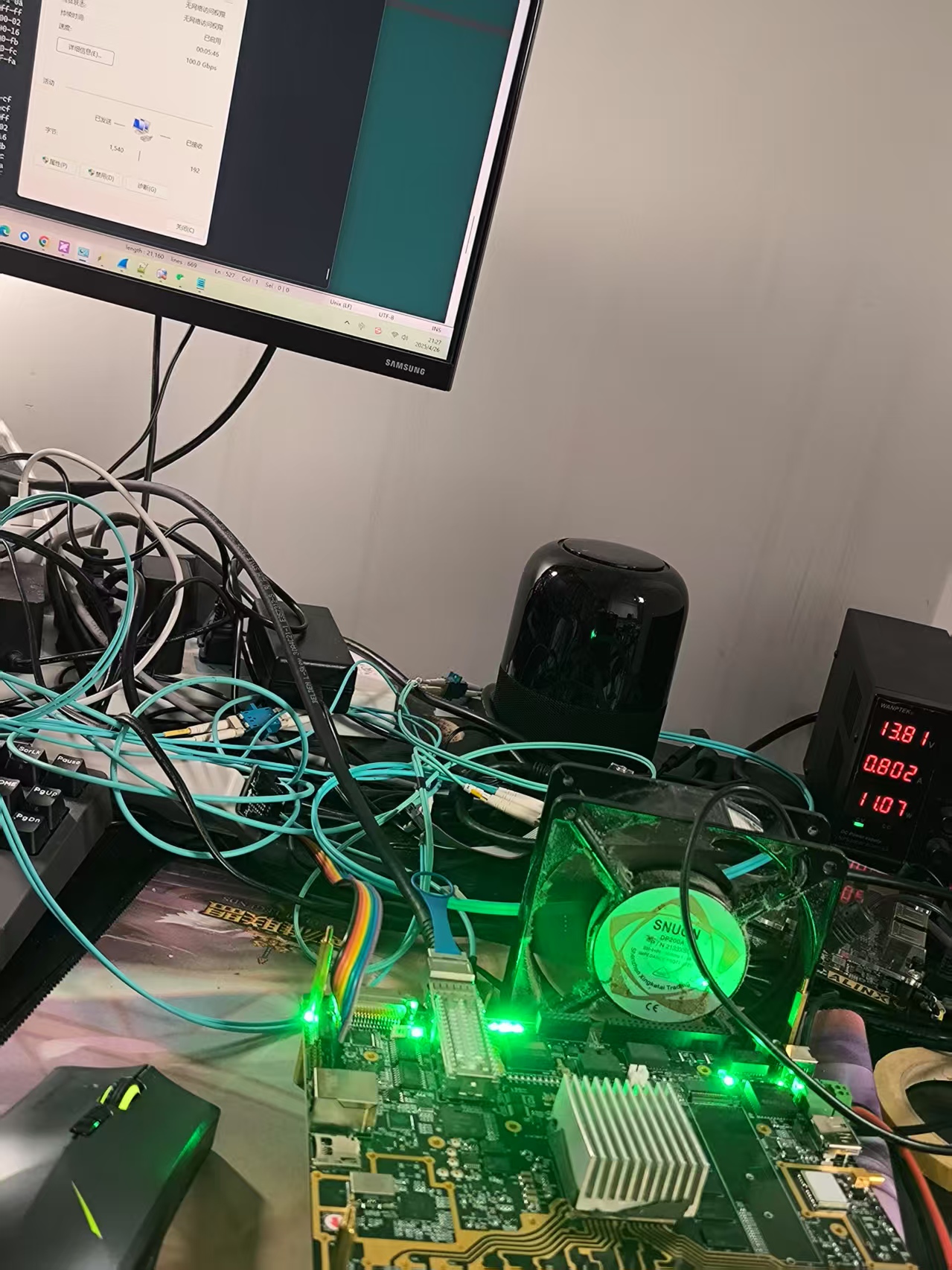

最终实现:

随着器件等级的升高,高速serdes的线速率也随之提高,RFSOC 4x最大可支持100G,主流方案为RDMA方案,该方案相对比较复杂,除了需要负责逻辑端的开发,还需操作系统中开发RDMA的驱动,对于对丢包不那么敏感的场景可考虑UDP方案;

系统搭载xilinx公司的CMAC具体配置如下

协议栈方面相比10G,主要就是通讯位宽从64BIT升级到512BIT,封包需要重新修改

最终实现: