使用Xilinx的IDE创建新代码文件的时候,IDE会自动添加上一个`timescale 1ns/1ps。

1、`timescale 1ns/1ps只作用于软件仿真,不参与实际的编译。

2、`timescale 1ns/1ps的功能和定义

`timescale 仿真延时/仿真精度

以下面的一段代码为例

module sim_prbs_test;

reg clk;

reg reset;

wire [7:0] prbs_out;

wire error;

prbs_test uut (

.clk(clk),

.reset(reset),

.prbs_out(prbs_out),

.error(error)

);

initial begin

clk = 0;

reset = 1;

#10 reset = 0;

#1000 $stop;

end

always #5 clk = ~clk;

initial begin

$monitor("Time: %0d, PRBS Out: %b, Error: %b", $time, prbs_out, error);

end

endmodule`timescale 1ns/1ps的含义:

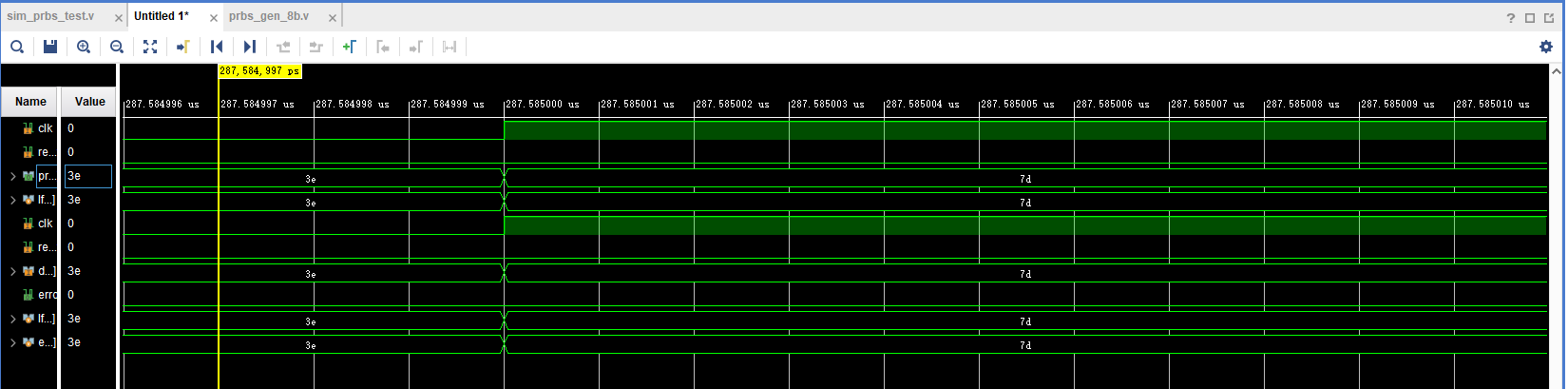

1\]1ns表示仿真延时, #1 = 1ns,比如代码中的#10 reset = 0; 就是等待10ns后,reset置0. \[2\]1ps是仿真的计算精度,也就是仿真后的结果图上能呈现的最小颗粒度是1ps,颗粒度越小,仿真计算的过程越漫长,所以大型仿真计算最好根据实际情况调整这个值,以提高仿真速度。1ps其实是非常小的结果,1ps对应的频率是1THz,如下图的时间轴。  而FPGA内部的逻辑通常也就是在500MHz(局部)以内的,大多数仿真不需要这么高的精度,尤其是做功能仿真的时候。