需要使用DDS IP核生成正弦波进行仿真验证,简单记录一下使用方法。

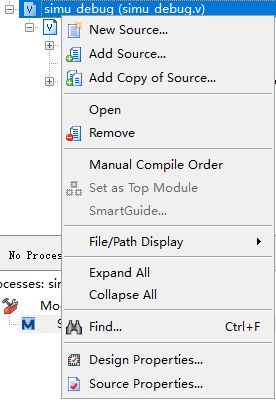

右键项目选择New Source。

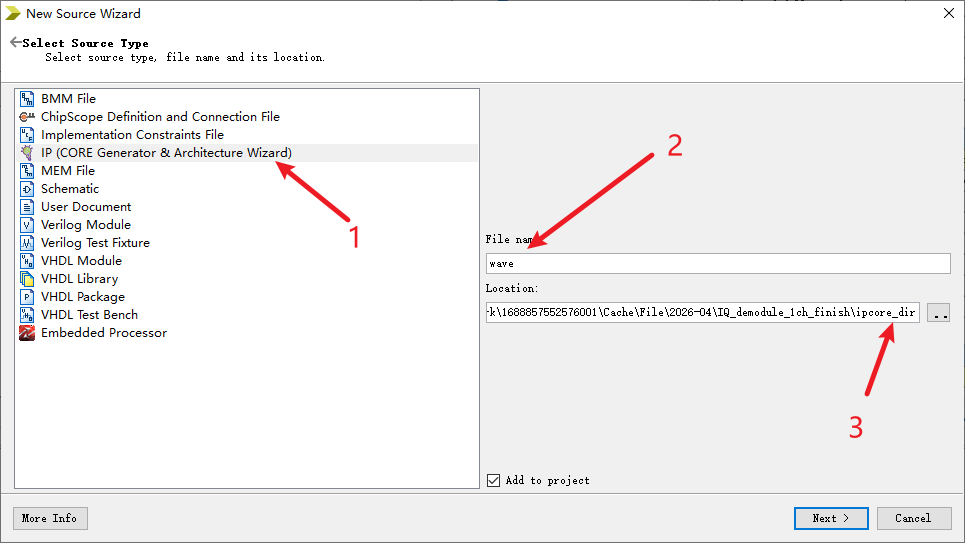

先选择添加IP核,然后命令文件名,最后选择存放路径。

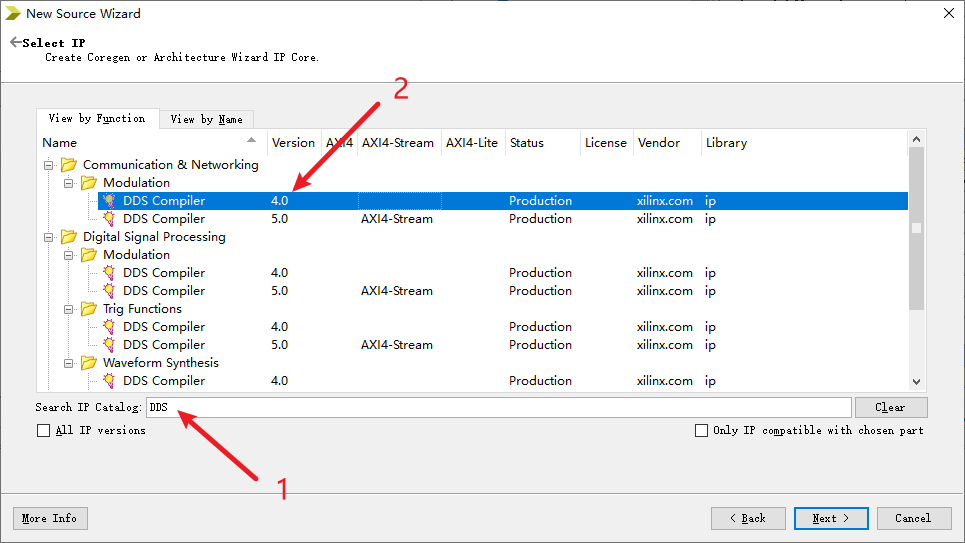

搜索框中搜索DDS会出来很多DDS Compiler,但其实只有两个一个是DDS Compiler 4.0(老版本,适合没有AXI总线的),另一个是DDS Compiler 5.0(新版本,适合给Zynq带AXI总线的系统用的)。选择4.0即可。

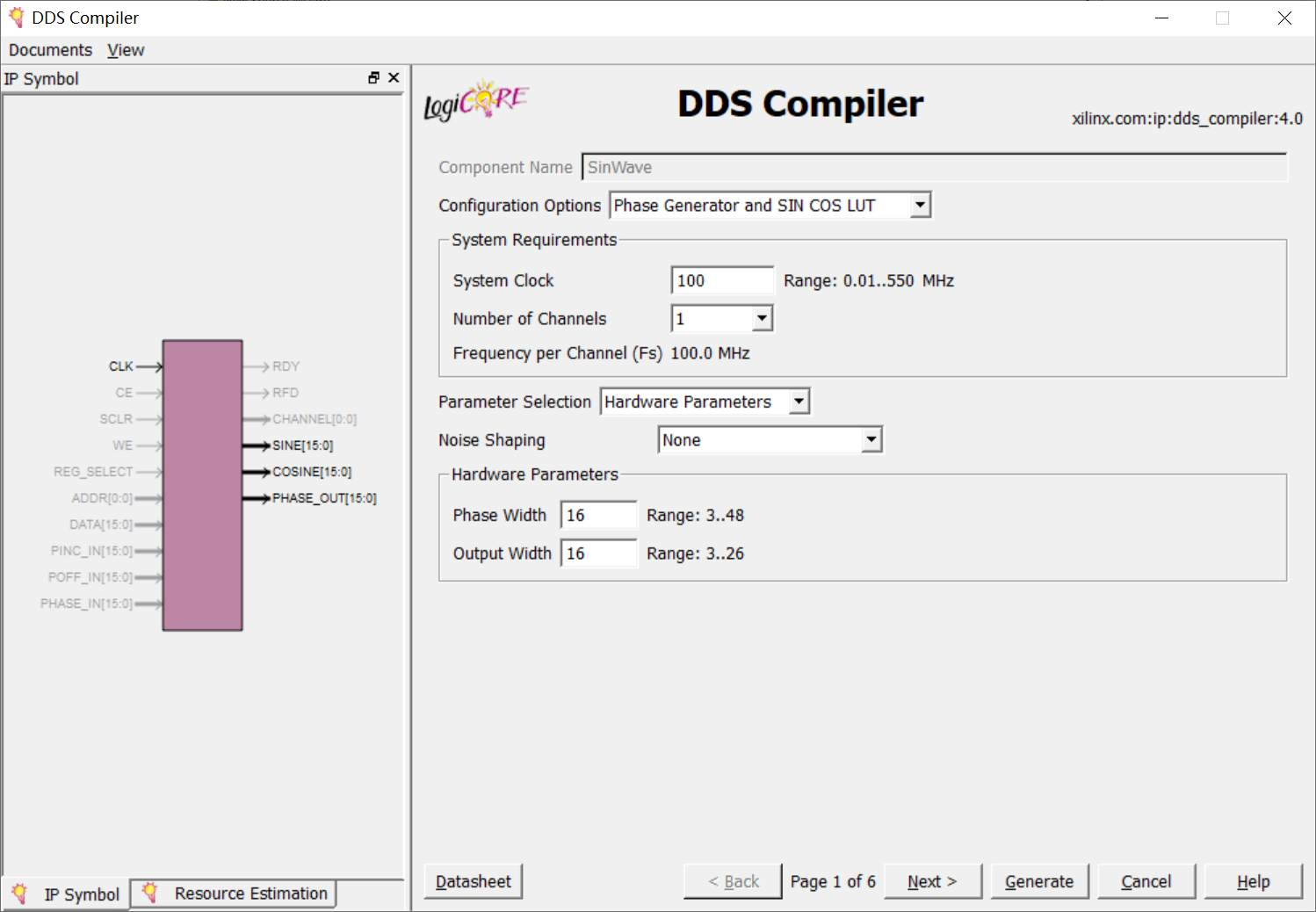

Configuration Options:

- DDS 的工作模式,决定 IP 核内部有哪些模块、输出哪些信号。

- Phase Generator and SIN COS LUT:包含相位累加器 + 正弦 / 余弦查找表,直接输出 SINE 和 COSINE 两路信号

- Phase Generator only:只输出相位地址,不包含正弦 / 余弦 LUT,需要自己外接 ROM

- SIN COS LUT only:只有正弦 / 余弦 LUT,需要自己给相位输入

System Clock:DDS IP 的工作时钟频率,单位 MHz

Number of Channels:同时生成的载波通道数

Frequency per Channel (Fs):采样率

Parameter Selection:我选择的是Hardware Parameters,需要设置相位累加器位宽Phase Width,输出位宽Output Width。

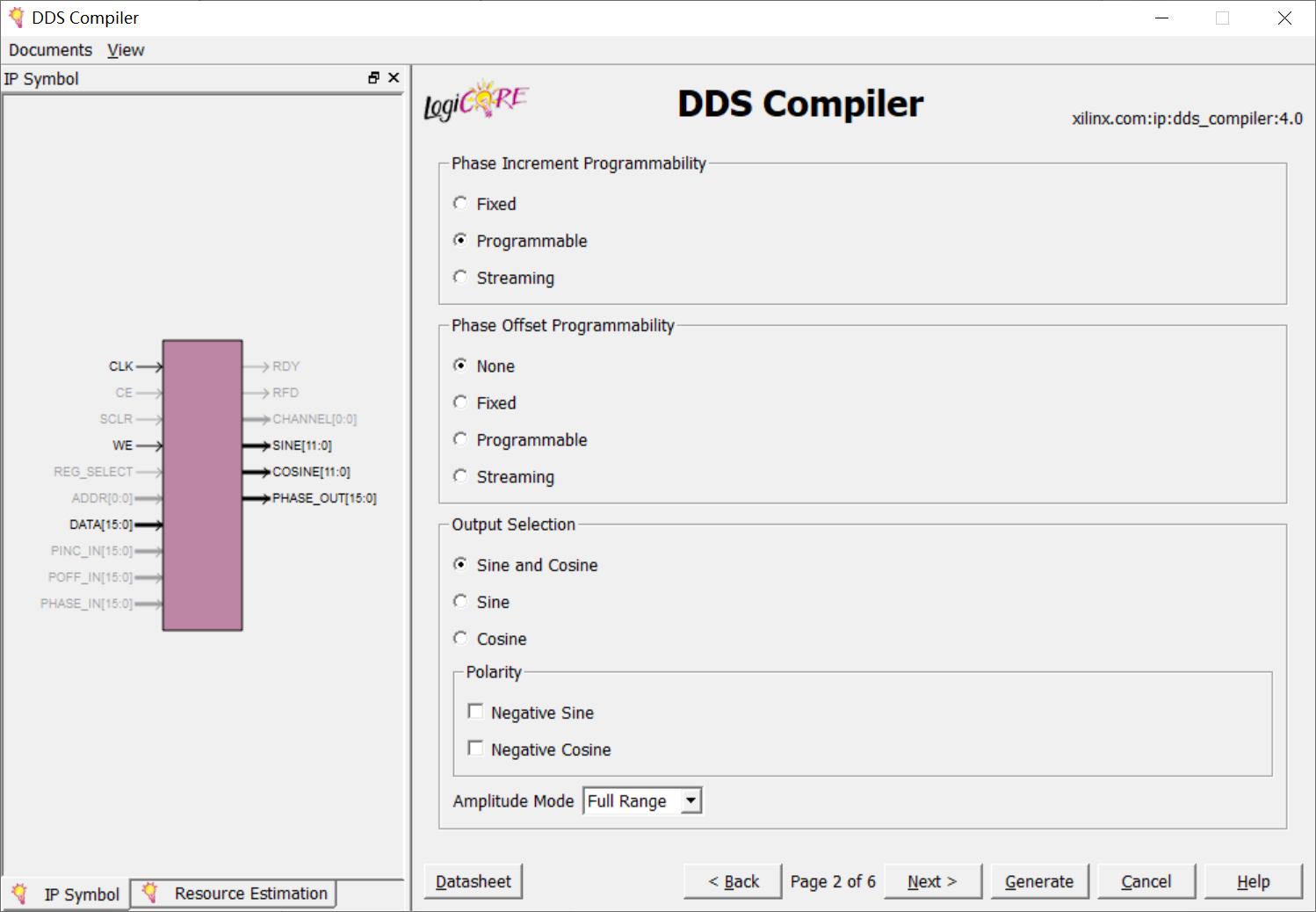

Phase Increment Programmability:能不能动态改频率的选项

- Fixed:频率固定,IP 在生成时就把频率控制字烧进去了,运行时不能改

- Programmable:运行时可以通过寄存器接口动态修改频率

- Streaming:通过数据流接口实时更新频率

Phase Offset Programmability:能不能动态调整载波相位

- None:不使用相位偏移,相位固定为 0。

- Fixed:固定相位偏移,IP 生成时配置好。

- Programmable:运行时可以动态修改相位。

Output Selection:IP 输出哪些波形信号

- Sine and Cosine:同时输出正弦和余弦信号。

- Sine:只输出正弦信号。

- Cosine:只输出余弦信号。

Polarity:极性

- Negative Sine :输出

-sin(θ) - Negative Cosine :输出

-cos(θ)

Amptitude Mode:幅度模式

- Full Range:输出使用完整的有符号数范围,如12位,范围就是-2048~+2047

- Unit Circle: 输出的数值是归一化的,范围大约是 -1 ~ +1

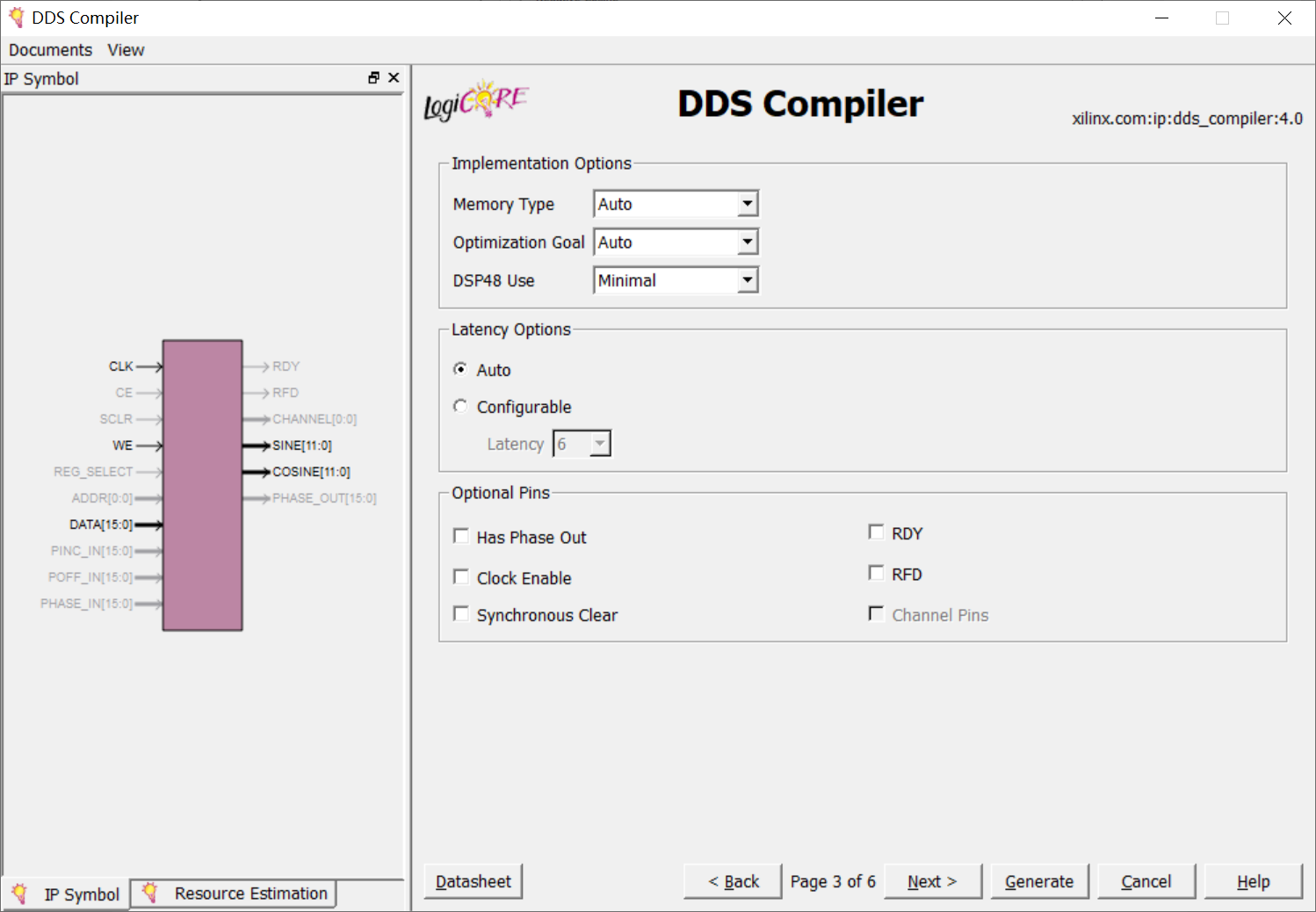

我不需要相位输出,将Has Phase Out取消。

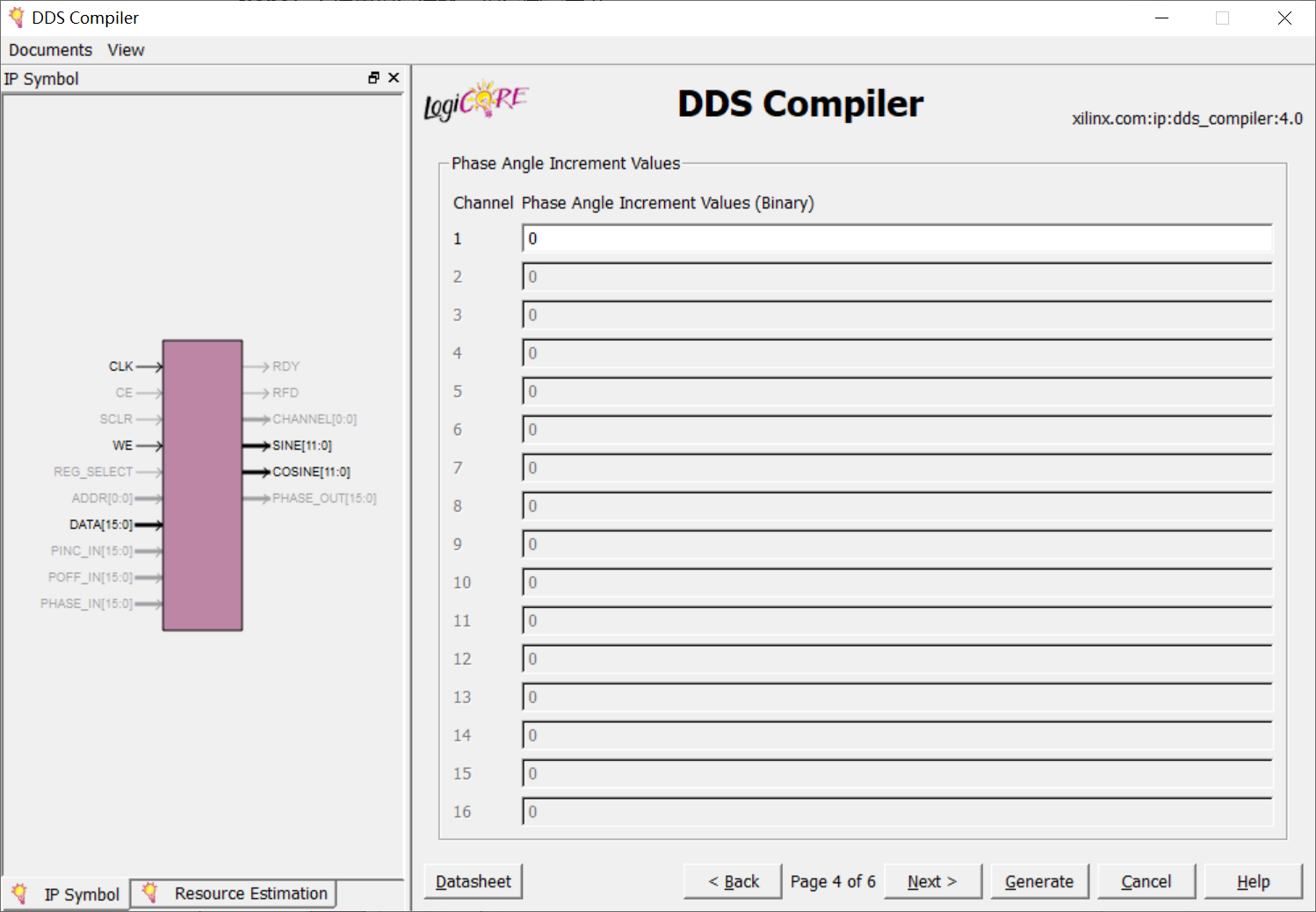

这里不需要设置,因为Phase Increment Programmability选的Programmable,可以例化的时候传参进去。

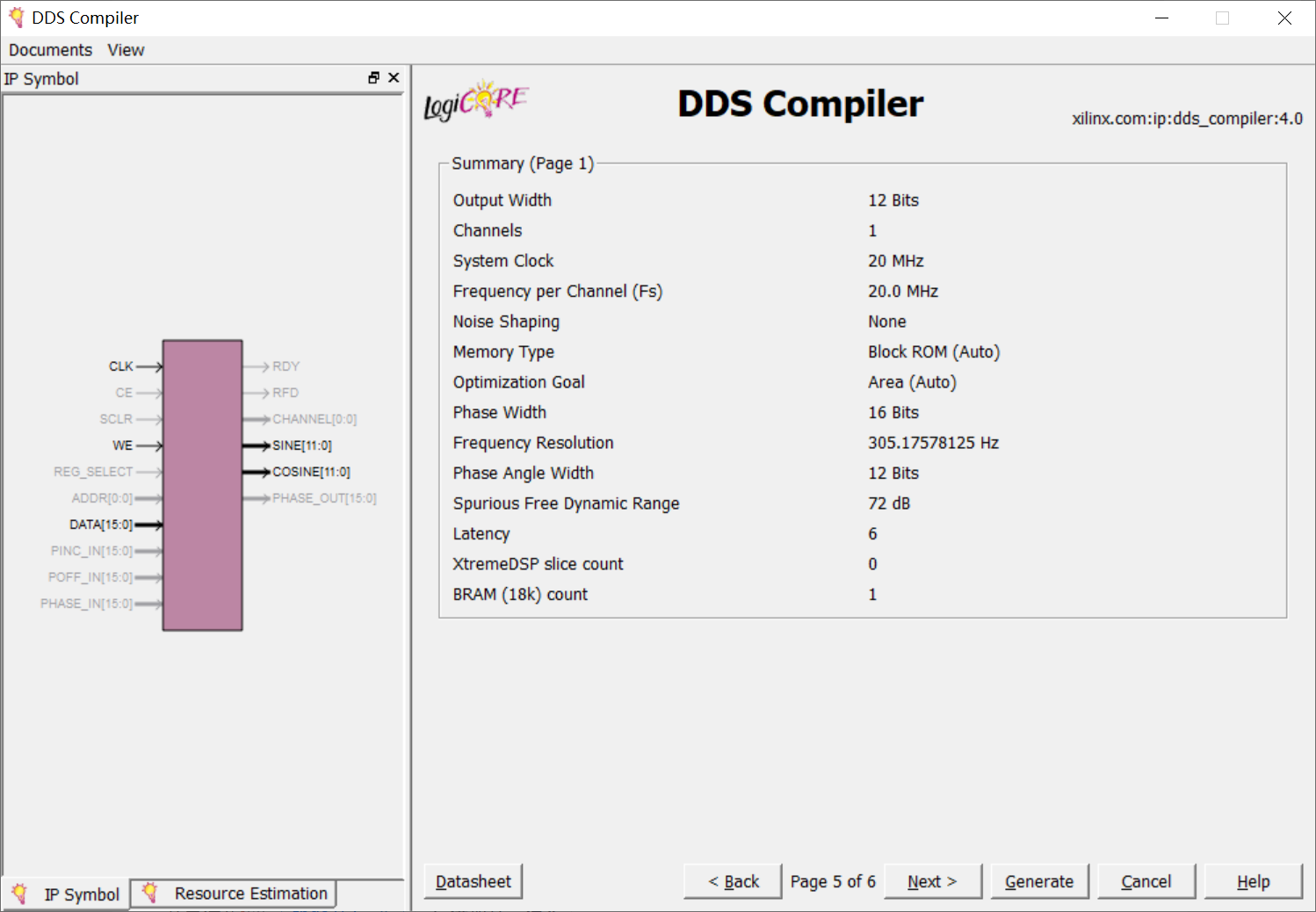

这里的Frequency Resolution要注意,这是频率分辨率,具体运算是20M/(2^16)

例化:

cpp

`timescale 1ns / 1ps

module data(

input clk,

output signed [11:0] d_out

);

wire signed [11:0] sine_0_5, sine_2;

wave(

.clk(clk), // input clk

.we(1'b1), // input we

.data(16'd3277), // 1MHz

.sine(sine_2) // output [11 : 0] sine

);

endmodule3277这么计算出来,要生成1M的波形,1M/频率分辨率 = 1M / (20M/(2^16));等于3277,实际生成的频率为3277 * (20M/(2^16) = 1000061.03515625,如果想要更准,那么就提升system clock和Phase Width