Placement Blockage: cell摆放阻挡层。它是用来引导工具做placement的一种物理约束或手段,目的是希望工具按照我们的要求来做标准单元的摆放。

它主要有三种类型,分别是hard placement blockage,soft placement blockage和partial placement blockage。

hard blockage所在的位置工具是无法摆放任何标准单元的,soft blockage所在位置只能摆放buffer和inverter,partial blockage所在位置可以摆放任何cell,但是工具工具可以根据我们设置的摆放比例,比如某个区域摆放太多标准单元可能会导致绕线问题,但近摆放buffer和inverter又浪费面积,那我们就可以设置一个可以摆放cell的比例来控制这区域的density密度来缓解潜在的绕线问题。

数字后端零基础入门系列 | Innovus零基础LAB学习Day1

数字后端零基础入门系列 | Innovus零基础LAB学习Day2

Halo:它和hard placement blockage功效是一致的。当我们给memory添加Halo时,随着memory的移动,这个Halo也会随着移动。而blockage则没有这个特性。

Routing Blockage: 绕线阻挡层。它是用来引导工作做routing绕线的一种物理约束或手段,目的是希望工具按照我们的要求来做routing。

所以placement blockage和Routing blockage相同的地方是它们都是作为阻挡层的约束条件,区别是前者是阻挡工具做摆放的阻挡层,后者是阻挡工具做绕线的阻挡层。

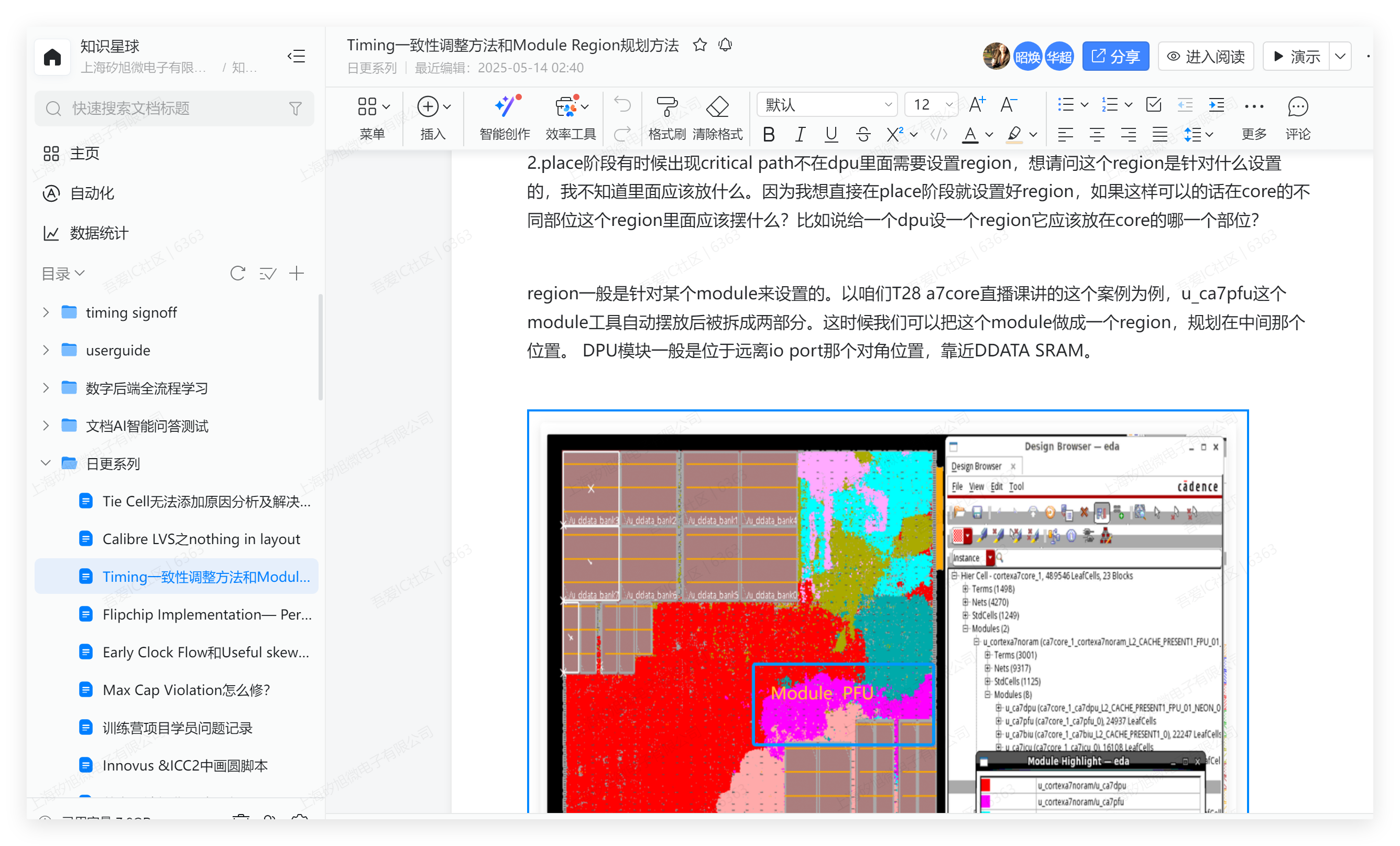

Innovus 支持四种类型的物理布局约束,即soft guide,guide,region和fence。它们都是用来guide引导工具做placement的一种物理约束条件。

Soft Guide: 除了没有固定位置外,soft guide约束类似于guide 约束。这为同一soft guide下的实例提供了更强的分组。soft guide约束不像fence 或region 约束那样严格,因此如果某些实例与其他模块有连接,则可能会将其放置得更远。

Guide: guide 约束是innovus中所有约束中最松散的约束。它大致定义了一个区域,您指示工具在该区域内放置给定模块的单元。

当模块移动或放置在core区域内时,guide约束会自动分配给该模块。如果未充分利用该区域,则不属于该guide的模块单元也可以放置在guide内部。同样地,如果所述区域利用率过高,来自guide的模块单元也可以被放置在该区域的外部。总而言之,guide是标准单元布局的软指标,可以认为该区域"可以进,可以出"

Region: region约束也是一个松散约束。然而,它比guide更强大。定义region 时,它要求将region中所包含的所有单元都放置在指定的region区域中。如果该区域中有额外的空间,则可能放进其他模块的单元。总而言之,一个region是标准单元布局的强约束,可以认为该区域"可以进,不可以出"

Fence:fence约束是Innovus 中最强的约束。即使未充分利用该区域,fence 约束也不允许将其他模块的单元放置在该区域内。此外,fence 区域中的单元格不能放置在定义的区域之外。

fence具有是排他性的,尽管不是完全的。总而言之,fence 是单元位置的最强约束,可以认为该区域"不可以进,不可以出"。

在标准的Innovus GUI中,fences是深棕色的。

在innous中创建soft guide,guide,region和fence的命令:

createInstGroup groupName

addInstToInstGroup groupName hInstName or instName or groupName

createSoftGuide <moduleName/groupName>

createGuide <moduleName/groupName> llx lly urx ury

createRegion <moduleName/groupName> llx lly urx ury

createFence <moduleName/groupName> llx lly urx ury

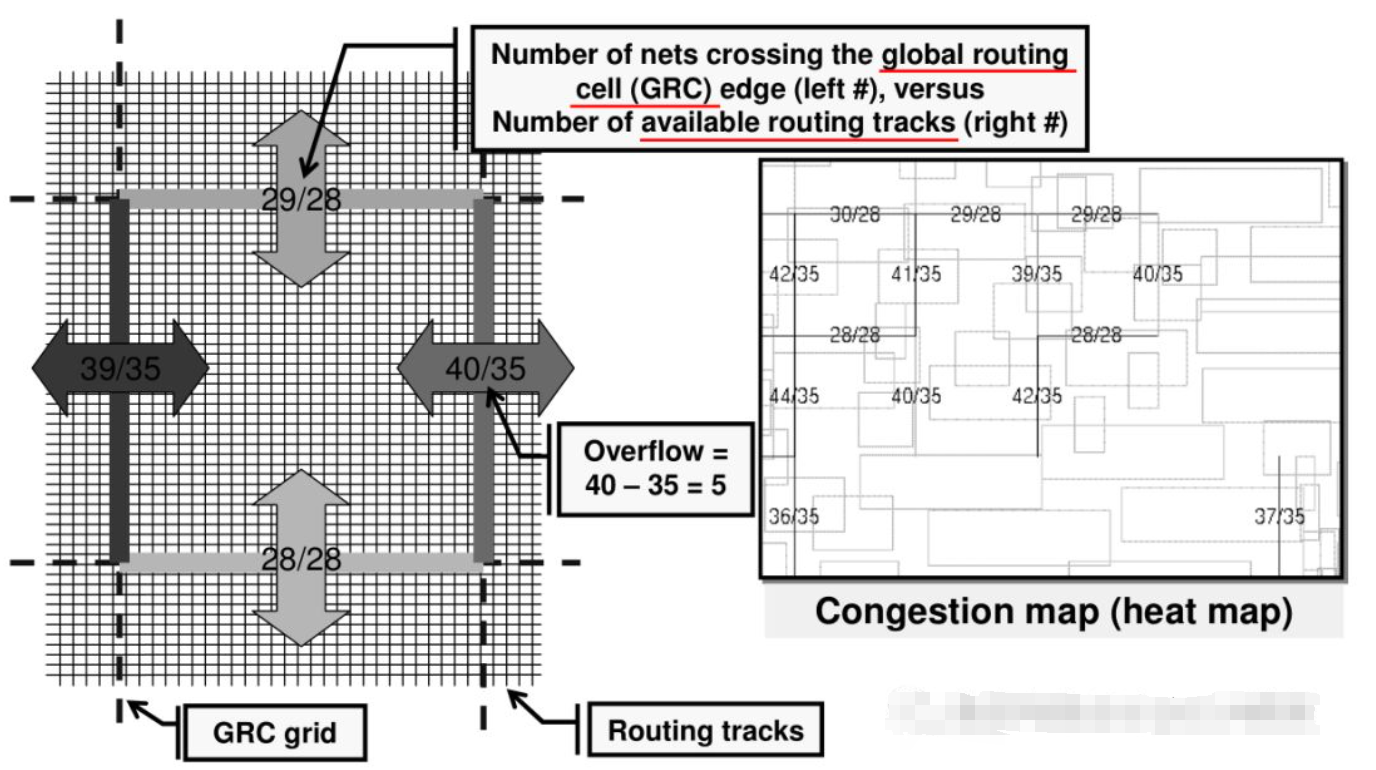

Gcell(GRC): 全称global routing cells。工具会把设计拆分成很多个Gcell,基于每个Gcell可以提供的绕线资源和实际需要占用的绕线资源来估算出每个Gcell的绕线是否可以绕通,所以它是工具用来估算Congestion用的。

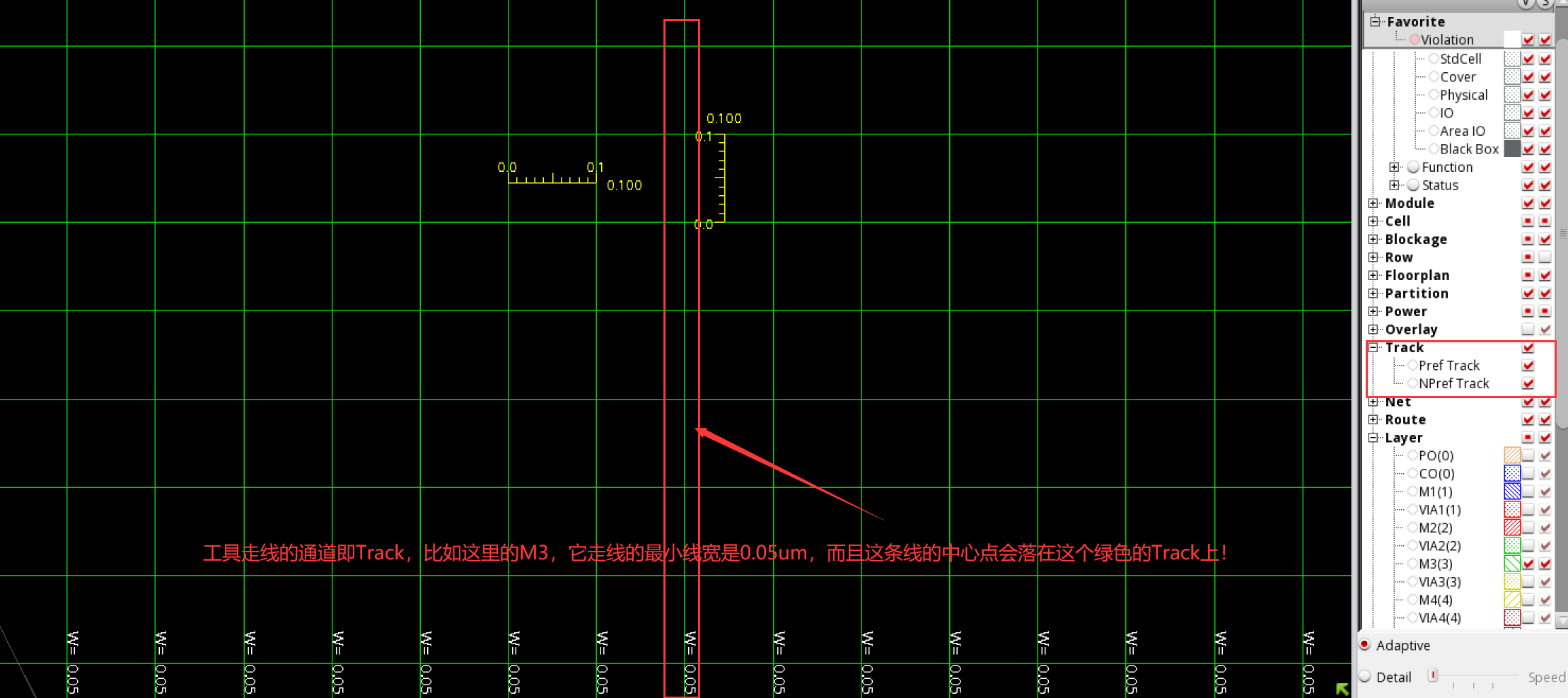

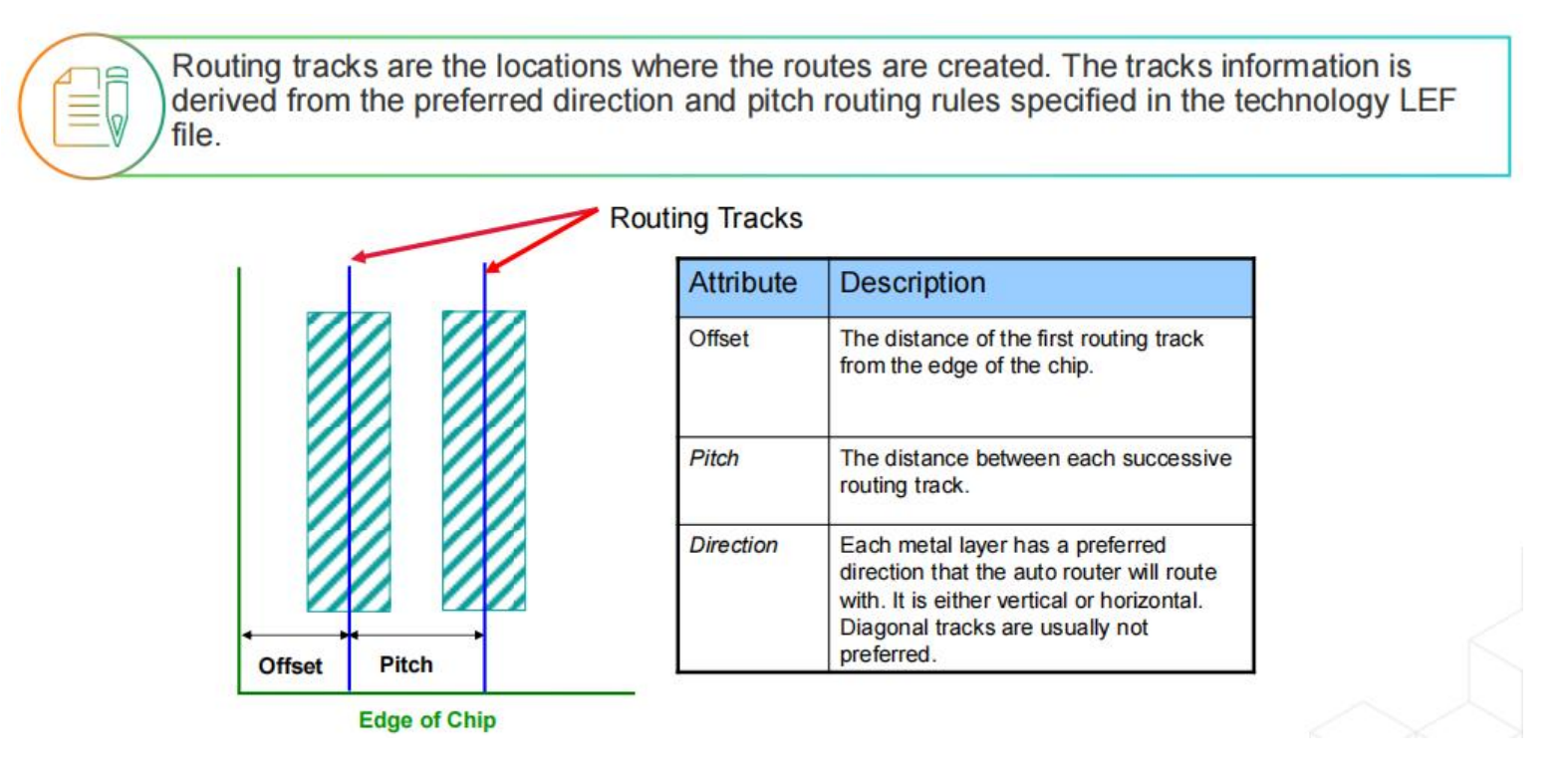

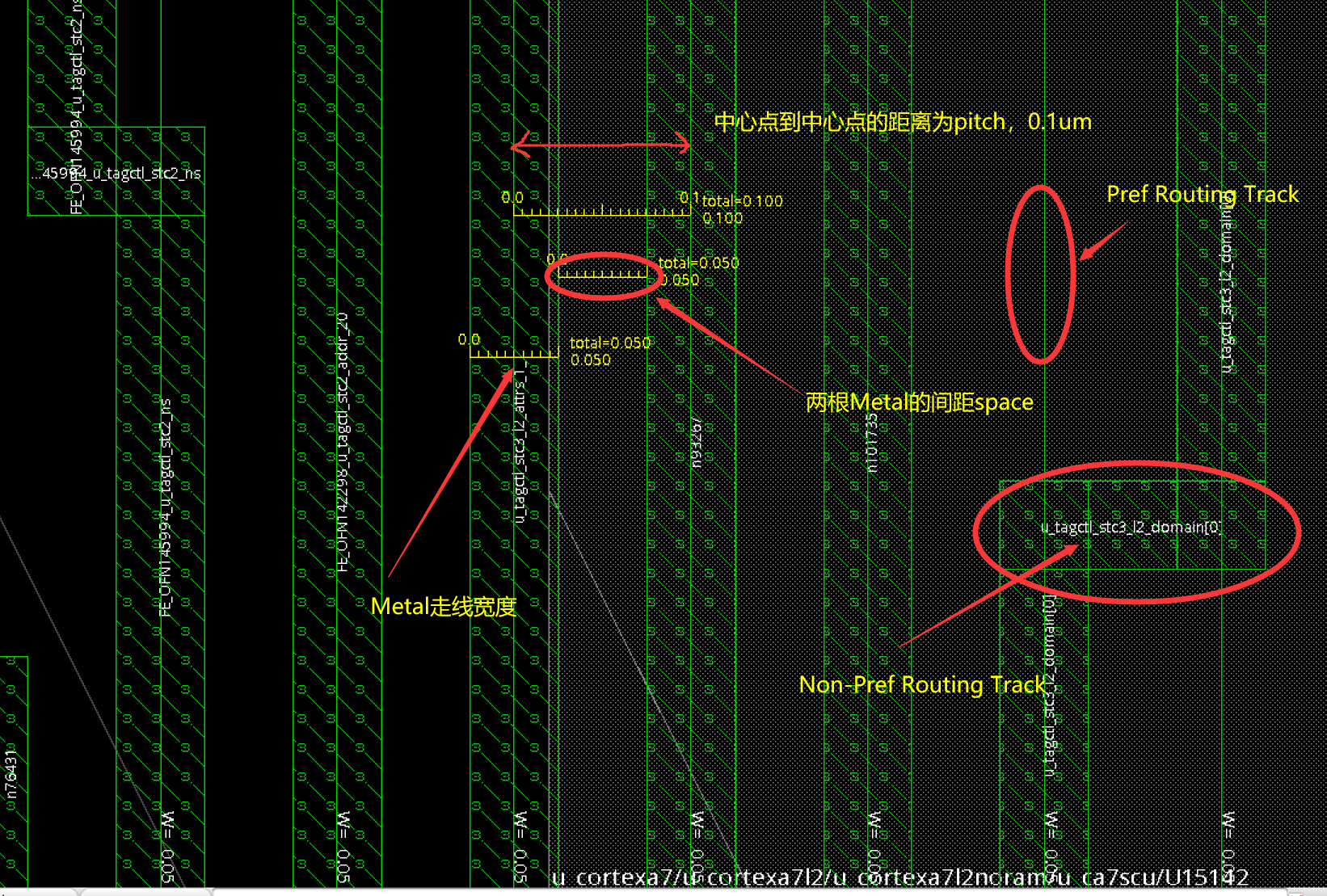

对于特定大小的芯片,它的routing resource就是每层金属的Pref Routing Track和Non-Pref Routing Track之和。而且工具在做绕线时会优先在Pref的routing track上走线。

Routing Track: 它是指金属走线的通道。工艺库中会指定好每层金属的track,它有默认方向的走线方向,比如M2的优先走线为水平方向,那么工具在走M2 routing的时候就会优先走水平方向。因此,对于一个给定大小的设计,绕线资源是固定的,即每层金属的绕线track都是定好的。

数字后端零基础入门系列 | Innovus零基础LAB学习Day6

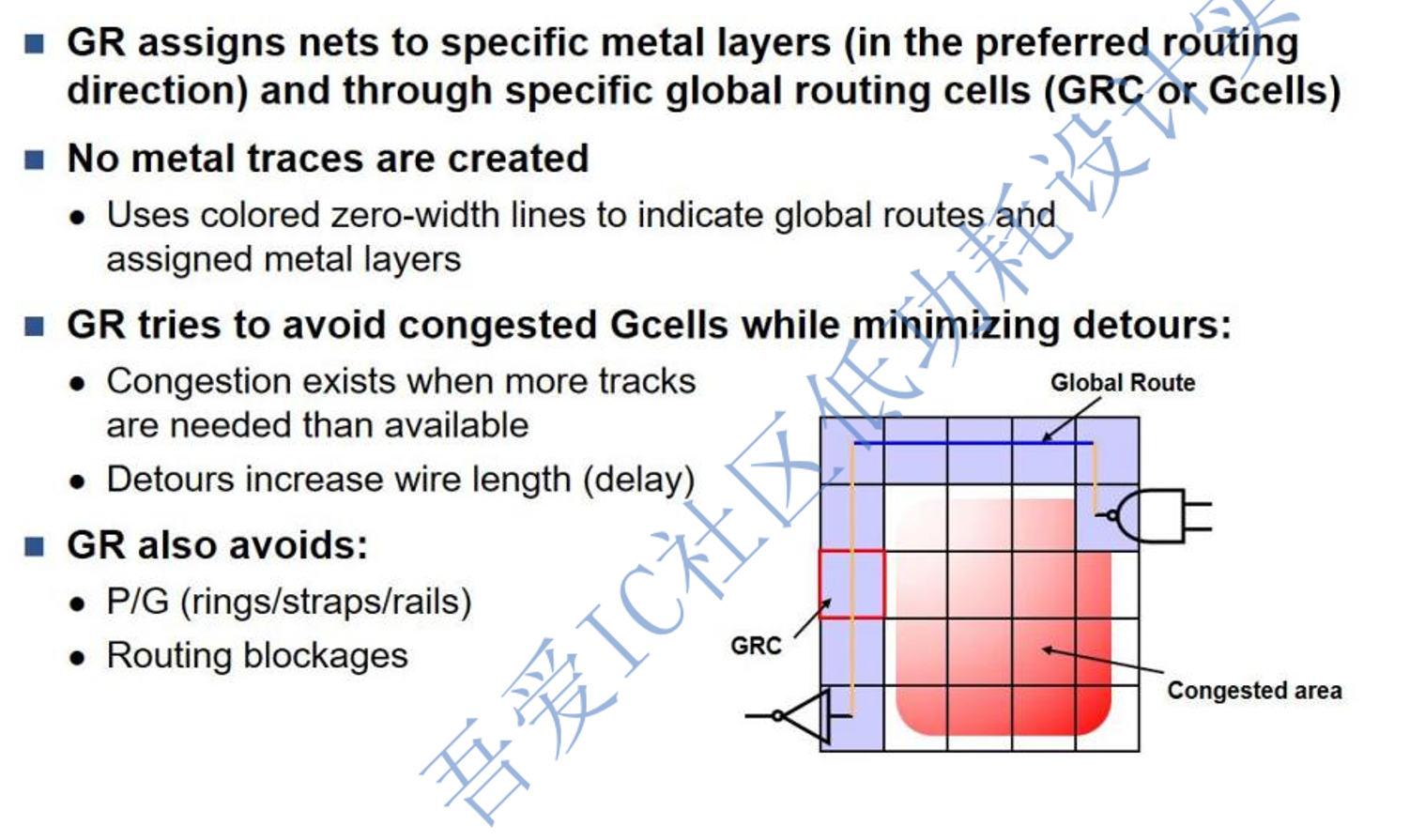

GR: Global Route。它又分为Early Global Route和Global Route。前者是指在placement,cts等阶段做的虚拟绕线。

我们知道绕线过程可分为global route(全局绕线)和detail route(详细绕线)。global route以gcell cell作为绕线参考网格,工具在绕线时会试图寻找gcell中的最短path, gcell是用来产生congestion map(拥堵图表),提前预估出当前设计是否存在绕线的风险。

Congestion: 从字面意思看就是拥塞,它是用来表征设计是否可以绕通。当我们说设计中存在较大congestion,往往就是指当前设计绕线大概率绕不通的情况。

Overflow:它是用来描述设计的congestion情况的。Overflow = Demand -Capacity。这个Overflow值工具会分成垂直方向和水平方向的Overflow,一般Overflow在1.5%内大概率是可以绕通。这个Overflow值一般可以在每个阶段的Log中报出。

GRC为正方形,每个边的尺寸通常为标准单元高度的两倍。它会计算出GRC每条边可用于布线的布线通道(track)的数目(Capacity),以及布线需要的布线通道的数目(Demand)。图中画出了一个GRC,边上的数值即为Demand/Capacity。Demand -- Capacity即为溢出(Overflow)的数目,如果存在Overflow,则Congestion Map中就会将GRC的那条边进行高亮,Overflow越大,则颜色越偏向于暖色调(即红色)。

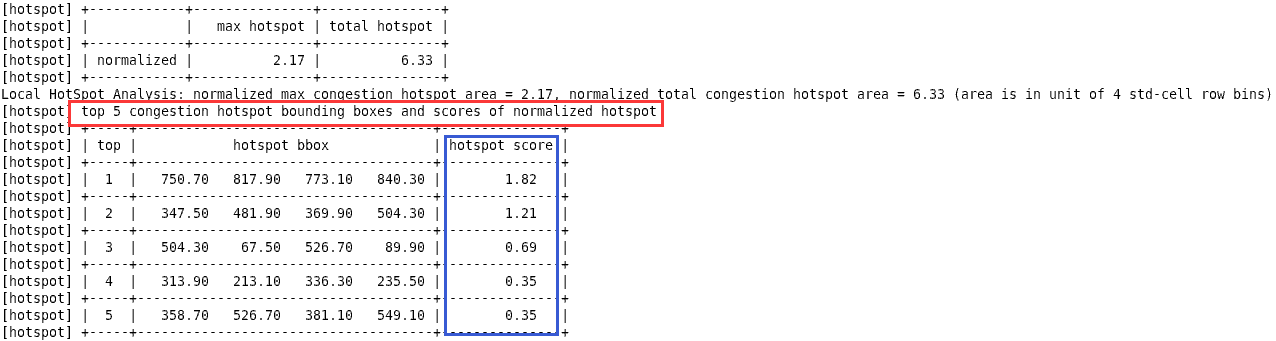

HotSpot: hotspot表征的是设计中congestion的热点,它是用面积来表示hotspot的分数。如果这个分数越高代表的是这个位置有congestion的点比较多。所以这个位置附近就有比较聚集的congestion问题。

工具跑完会报出设计中最差的五个hotspot点。这里如果报出来的五个点的hotspot值小于150,我们认为当前设计不存在非常聚集性的congestion。此时,如果overflow值大于2%,也是有机会能绕通的。

Macro/Block(宏单元):是一种由逻辑单元和物理单元组成的封装单元。它可以看作是一个可重复使用的功能单元,包括多个逻辑电路单元的封装,其功能一般比较复杂,比如存储器、算术运算单元等。Macro一般包含Memory,第三方IP和我们自己做的子模块。在Innovus中Macro和Block是同一个概念。

Std Cell: Standard Cell标准单元,它是foundary代工厂提供library中的基本功能cell,比如BUF,INVERTER都是标准单元cell。Std cell具有简单的功能、相对较小的面积和较短的设计周期,适用于芯片设计中一些基本电路的设计。现在大部分的芯片设计都是基于foundary提供的library的Std cell的设计。

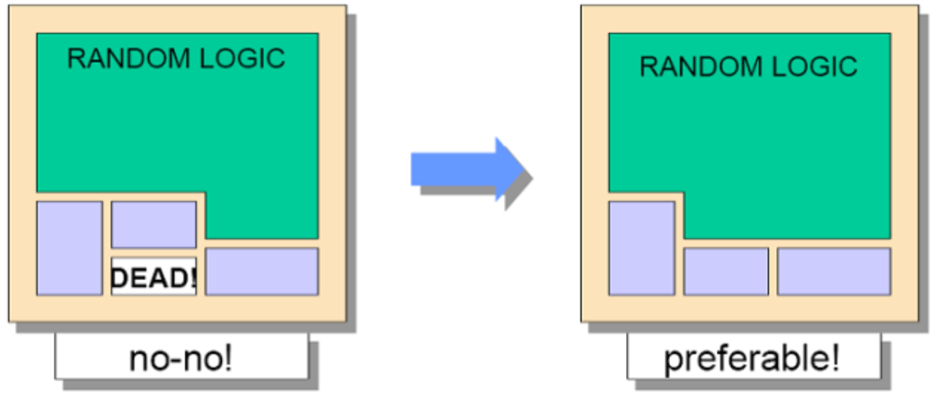

Macro摆放是需要工程师自己来摆放,不能用工具自己做placement。在摆放Macro时需要遵守以下几大原则。

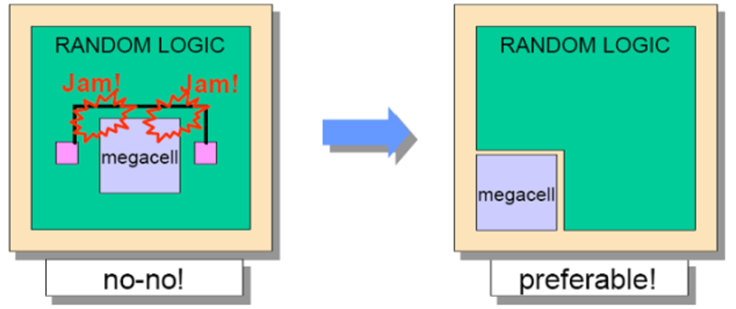

1.在core外围放置宏单元

由于会产生大量的detour布线,在core内部放置宏单元会在布线过程中造成严重后果。这是因为宏单元等于布线的一个大blockage。同样,将宏单元放置在core外围使向这些宏单元供电变得更加容易,并减少了消耗大量功率的宏单元出现IR drop问题的可能性。

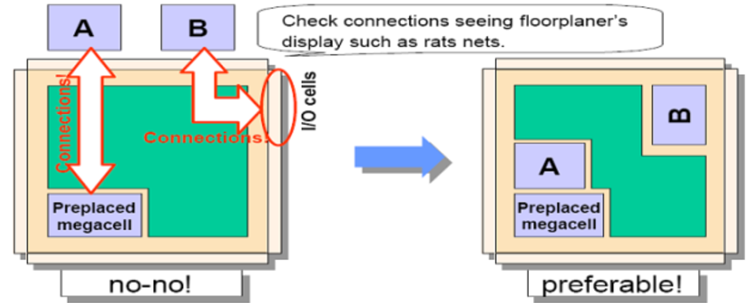

- 放置宏单元时考虑与已固定位置的单元之间的连接

当您决定宏单元位置时,您必须注意与已固定位置的单元 (如I/O和已布局的宏单元) 的连接。根据数据流,最好将宏单元放置在有关联的已固定位置的单元附近。可以通过在EDA工具中的图形用户界面中显示线路连接关系来检查连接。

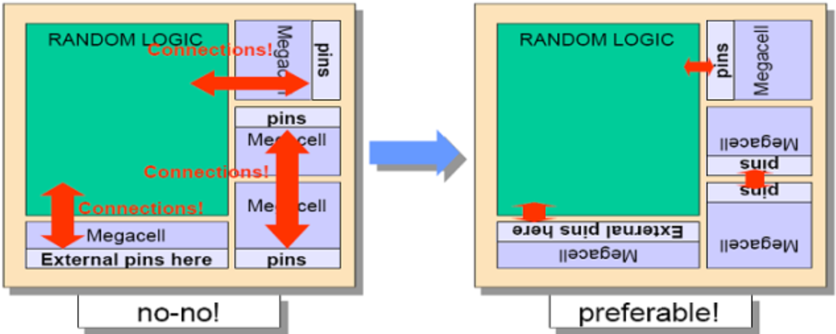

- 调整宏单元的方向实现最小化引脚之间的距离

在确定宏单元的方向时,还必须考虑引脚的位置和相应的连接。

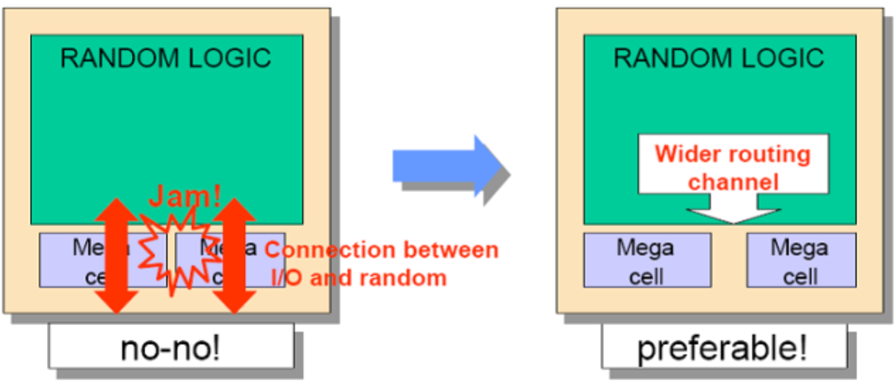

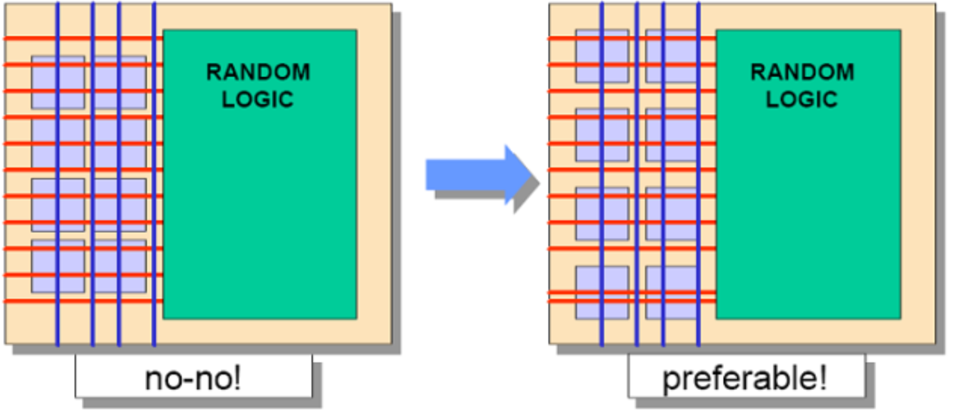

- 在宏单元周围预留足够的空间

对于常规的网络布线和电源布线,您必须在宏单元周围保留足够的布线空间。在这种情况下,精确估计布线资源非常重要。使用拥塞图来识别宏单元之间的hotspots ,并根据需要调整位置。

- 尽可能减少宏单元之间的空白区域

除预留布线资源外,减少宏单元之间的空白区域可以增加标准单元的利用面积。选择不同的宽高比 (如果该选项可用) 可以消除宏单元之间的空白区域。

- 为电源网络预留空间

所需电源布线的数量会根据功耗而变化。您必须估算功耗并为电源网络预留足够的空间。如果您低估了电源网络所需的空间,则可能会遇到布线问题。

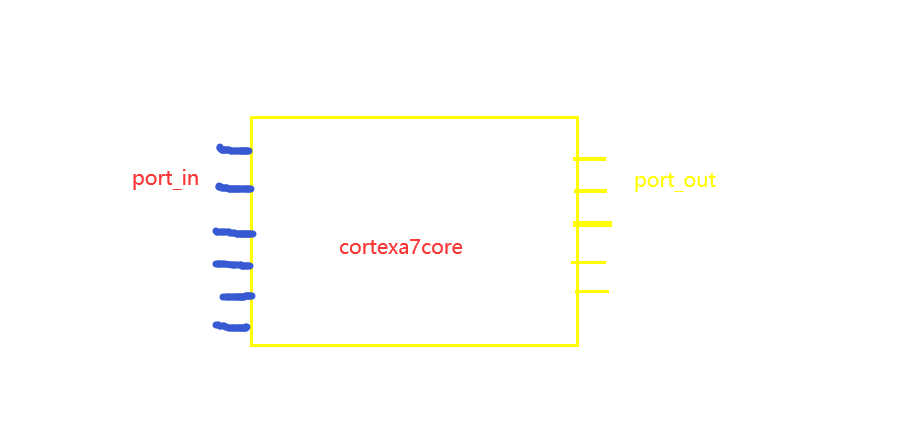

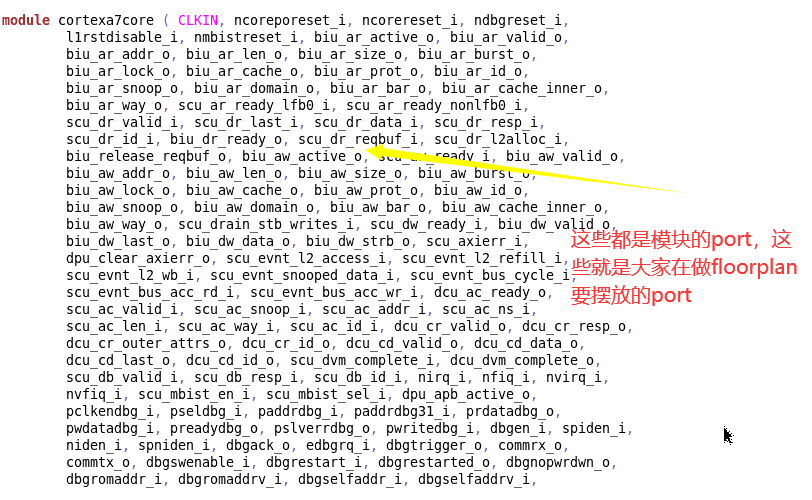

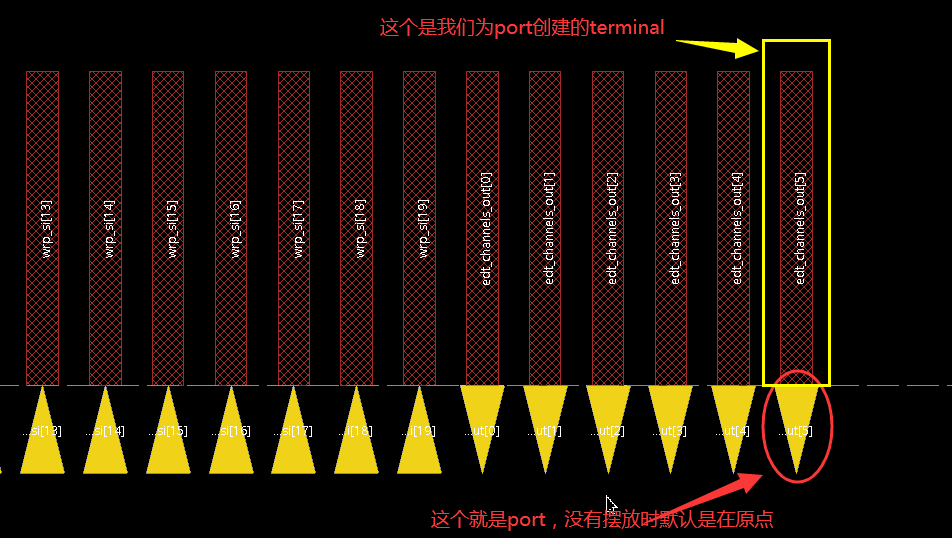

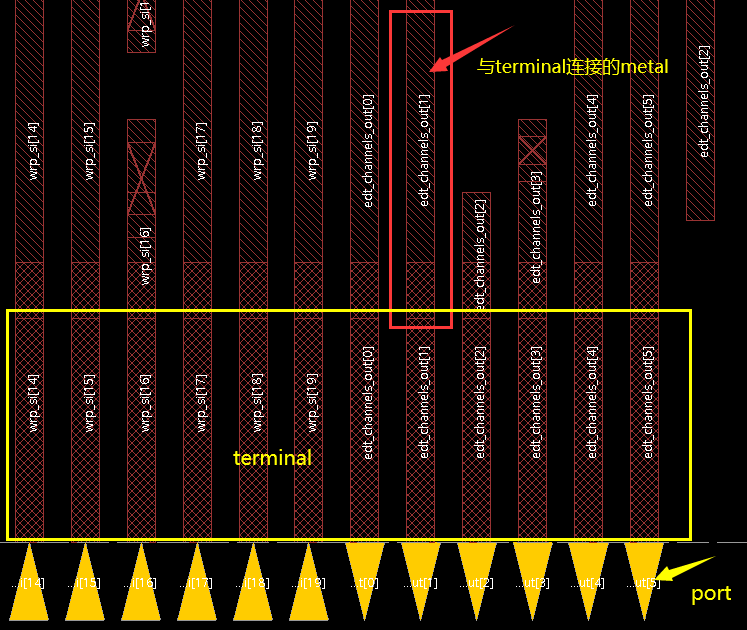

IO Port /IO Terminal:

首先通过两个图来说明port和terminal的概念。port其实就是block level模块的端口或接口信号。

在netlist会这样来描述。module design_name (port1,port2,port3, ...,portn ); 这里的port1直至portn为当前设计模块的输入和输出端口。对应描述的就是一个带功能的黑盒子。

但在数字后端PR实现时需要把这个逻辑连接转成物理连接,即要做metal的连接。显然这个port是逻辑的存在,无法与metal进行一个物理连接。因此,PR阶段就引入了terminal的概念,在摆放port时会在这个port上面create一个terminal,即一块metal shape,而且这个terminal是和这个port是一一对应的。这样后续工具绕线时就可以通过这个terminal的metal shape进行实际的物理连接。

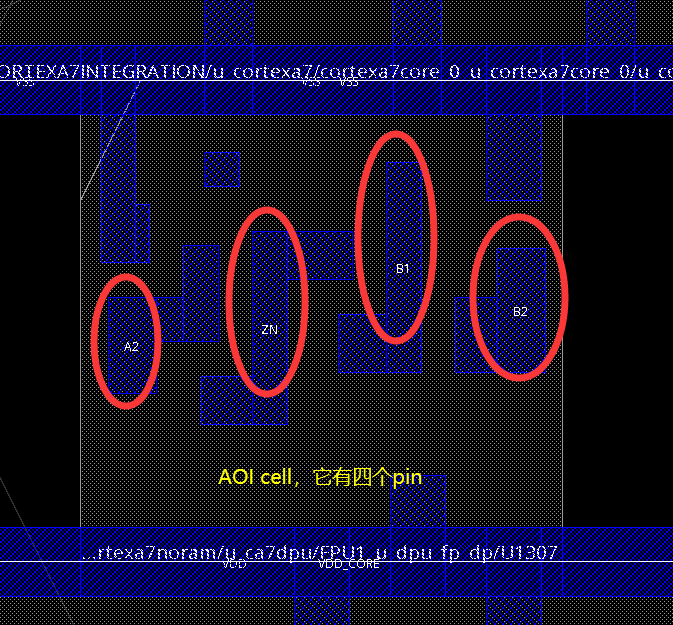

而pin是指对于cell来说的,比如下面这块AOI cell,它总共有四个pin,其中有三个输入pin,分别是A2,B1,B2,还有一个输出pin ZN。 每个cell都有它的功能,所谓的功能就是这个cell它能干什么。功能可以根据标准单元库文档的真值表得知。举个简单的例子,普通inverter,它的功能就是起到数据取反的功能。一个cell要具备特定的功能就肯定要有特定的引脚,就是这里说的pin。这里就可以理解成人要有正常的功能,它就必须有手有脚。通过手脚大脑等才能充分发挥人的功能。