TSMC 12nm A72项目我们需要按照foundary的要求提前在floorplan阶段加好TCD Cell。这个cell是用来做工艺校准的。这个dummy TCD Cell也可以等后续Calibre 插dummy自动插。但咱们项目要求提前在floorplan阶段就先预先规划好位置。

TSCM12nm 1P9M的metal stack结构图如下图所示。

所以这颗TCD cell就会分成FEOL TCD和BEOL TCD两种。这个工艺相比T28nm工艺多了M0和V0,这几层都属于前段FEOL(有的地方会称他们为MEOL)。

根据foundary的要求,在一个2500um2500um 窗口内就必须要有一颗这种Dummy TCD Cell。大芯片比如芯片尺寸超过10000um 10000um才需要加ICOVL这种cell。

摆放好TCD Cell,做好floorplan工作,务必做calibre drc的检查。这个在之前T28nm工艺的a7core项目还可以不做,但T12nm是必须做的,否则大概率都会有base layer 的drc violation。

这里重点提醒的是FEOL TCD cell的poly方向必须和标准单元,memory的poly方向一致,而且是垂直方向!

而且还需要给TCD Cell添加好blockage和routing blockage。

下图所示为T12NM Calibre DRC相关检查item。两个TCD cell也不允许摆放太近!

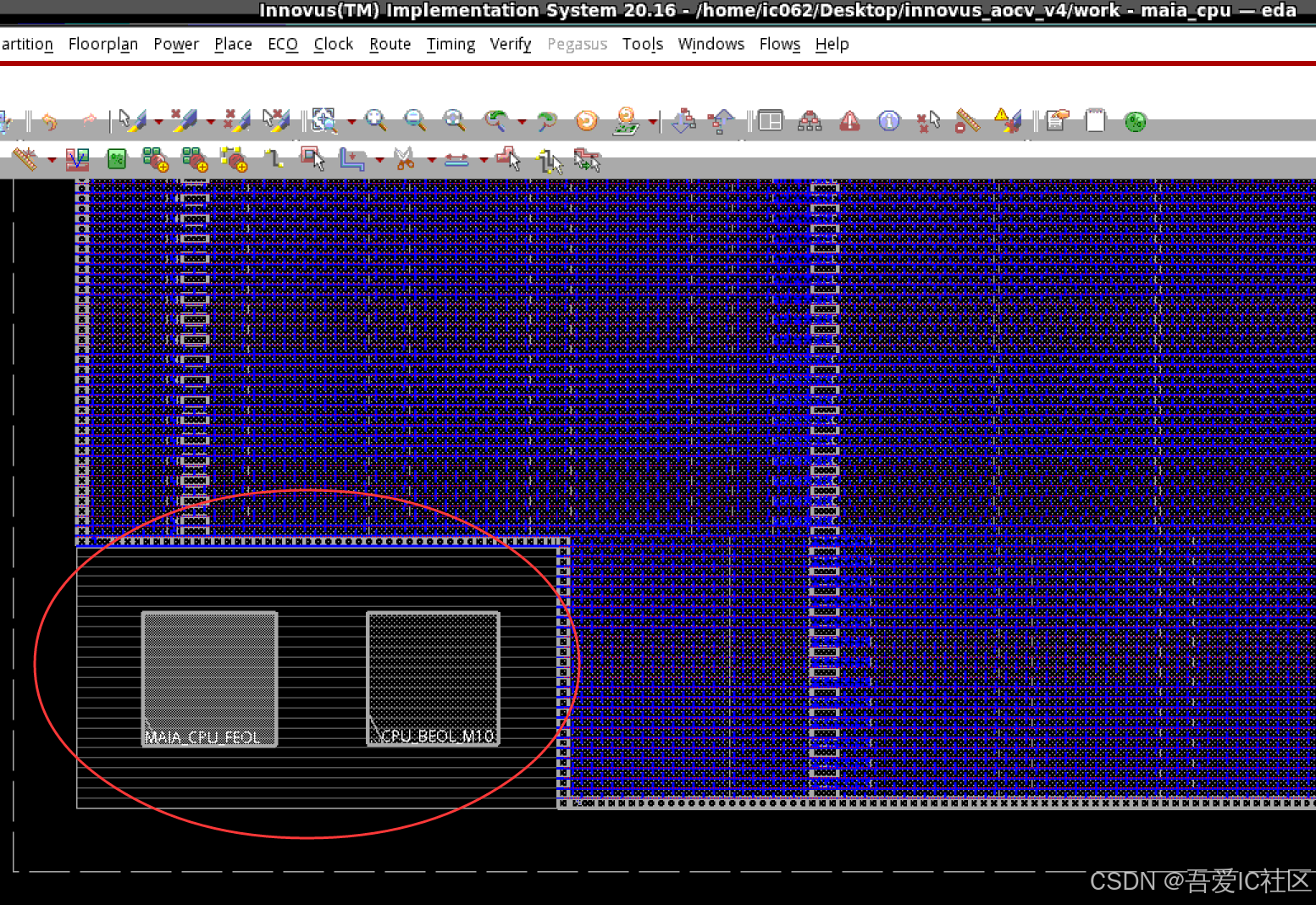

下图所示为咱们T12nm maia_cpu A72添加TCD cell后的layout截图。欢迎大家讨论这样的摆放是否合理?这类TCD Cell一般摆放到什么位置比较合理?