STM32-复位和时钟控制RCC

- 2-STM32-复位和时钟控制RCC

- 摘要

- 说明

-

- 本文参考资料如下:

- 一、STM32最小系统回顾

-

- STM32F103C8T6核心板原理图

- 二、复位

- 三、时钟

-

- 3.1 时钟树

- 3.2 STM32启动过程

- 3.2 SystemInit()函数

-

- 3.2.1 SystemInit()第1句:

- 3.2.2 SystemInit()第2句:

- 3.2.3 SystemInit()第3句:

- 3.3 SetSysClock()函数:

- 3.4 SetSysClockTo72()函数:

-

- 3.4.1 SetSysClockTo72()第1句:

- 3.4.2 SetSysClockTo72()第2句:

- 3.4.3 SetSysClockTo72()第3句:

- 3.4.4 SetSysClockTo72()第4句:

- 3.4.5 SetSysClockTo72()第5句:

- 3.4.6 SetSysClockTo72()第6句:

- 3.4.7 SetSysClockTo72()第7句:

- 四、标准库与HAL库区别

-

- 4.1 HAL库SystemInit()函数

- 4.1 HAL库配置系统时钟为72MHz函数

-

- 4.1.1 Stm32_Clock_Init函数

- 4.1 HAL库配置系统时钟为72MHz函数

- 五、总结

- 六、资料连接

2-STM32-复位和时钟控制RCC

摘要

在上一篇文章中,我们讲解了STM32F103C8T6最小系统中复位和时钟硬件部分 ,在本章中讲解最小系统中的复位和时钟的软件部分 。本文章根据《1-STM32F10x-中文参考手册》的第6节复位和时钟为依据,并介绍时钟源选择外部8MHz晶震HSE,通过SystemInit()函数将STM32时钟配置为72HMz的代码,并在最后对比标准库和HAL库对时钟配置的不同。

说明

本系列,将整理STM32F103内置外设的使用,"基于标准库"进行学习开发,并将手册说明与标准库代码进行对应学习,在文章最后提供本系列中参考的文章和工程代码下载链接。

本文参考资料如下:

markdown

## 1.硬件平台

STM32F103C8T6最小系统板

## 2.软件平台

MDK5

## 3.参考文档

1.《1-STM32F10x-中文参考手册》

2.《3-STM32F103xCDE数据手册-中文》

3. 《STM32F103C8T6核心板原理图》

4.《Cortex-M3权威指南》一、STM32最小系统回顾

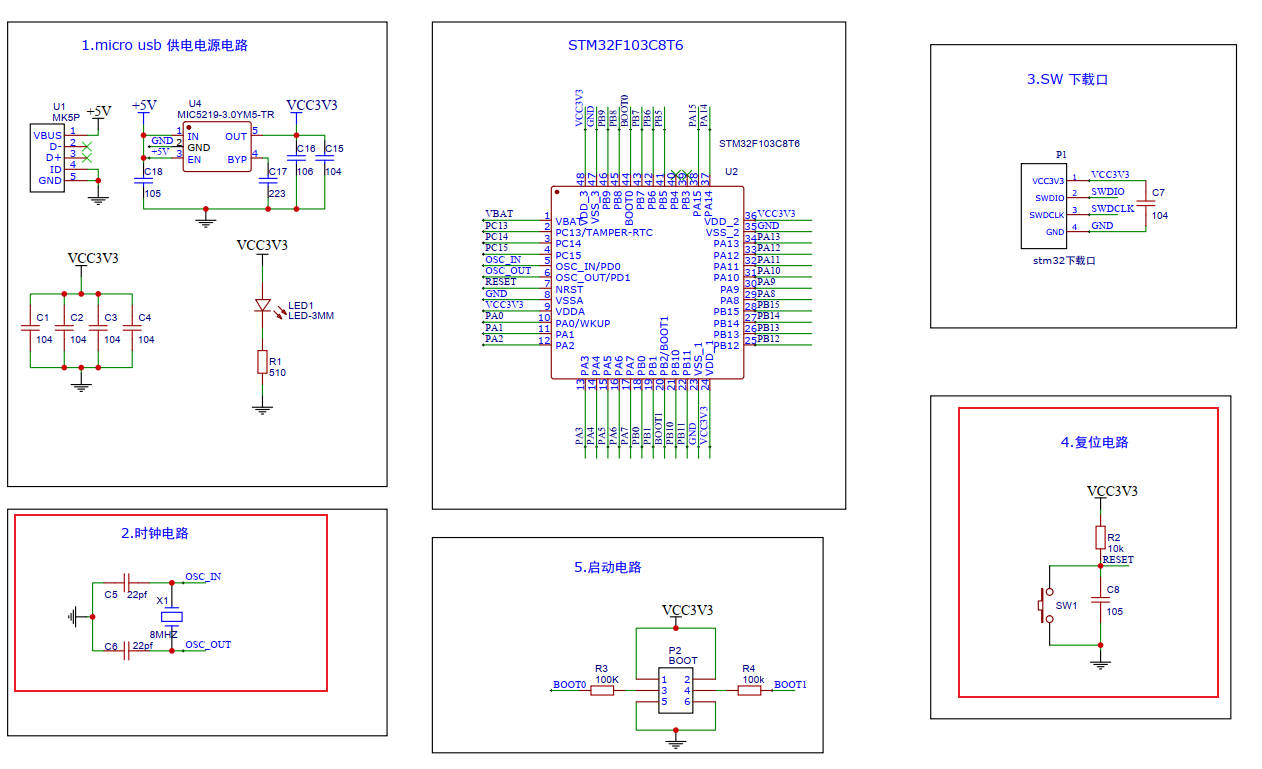

在上一节STM32最小系统中,讲解了STM32最小系统由:电源、时钟、下载、复位、启动 五个部分组成,本文主要讲解时钟和复位两个部分,因为这两个部分和后续编程紧密相连,而电源、下载、启动三个部分相对固定,编程上不需要太多改动。

STM32F103C8T6核心板原理图

图中标红的两个部分,时钟和复位就是本文要讲述的部分。复位使用NRST引脚复位 ,时钟使用外部晶体震荡器HSE

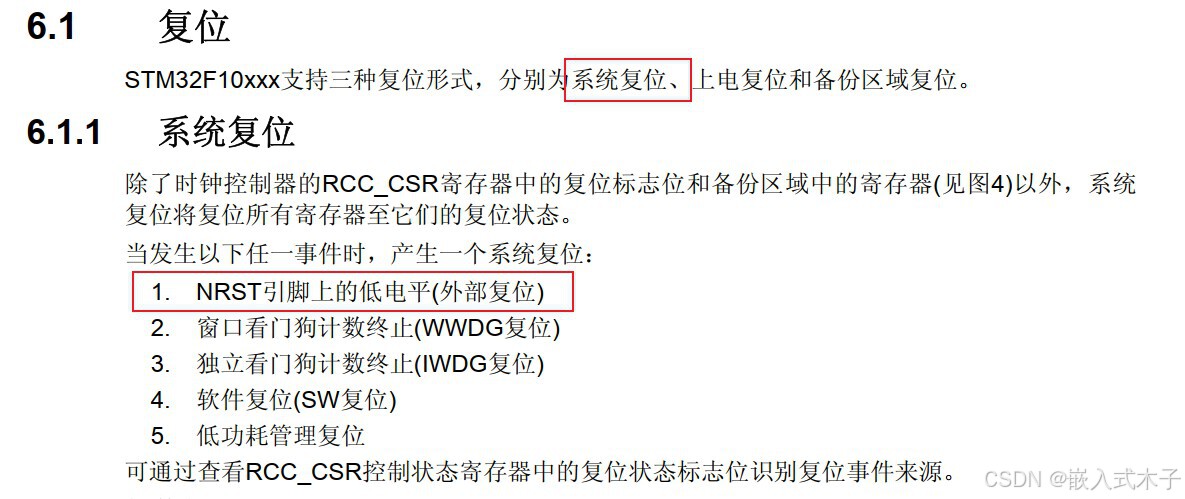

二、复位

由《1-STM32F10x-中文参考手册》的第6节复位和时钟可知,STM32复位方式有三类:系统复位、上电复位、备份区域复位 ,其中系统复位包含了:NRST引脚复位 。

由系统复位方式可知:一共有5种复位方式,STM32最小系统中的复位就是NRST引脚复位,是硬件复位方式,也是最常用的一种复位方式。其余四种都是软件复位,IWDG、WWDG、SW三种复位方式,在后续看门狗实验时讲解。低功耗复位在低功耗实验时讲解。

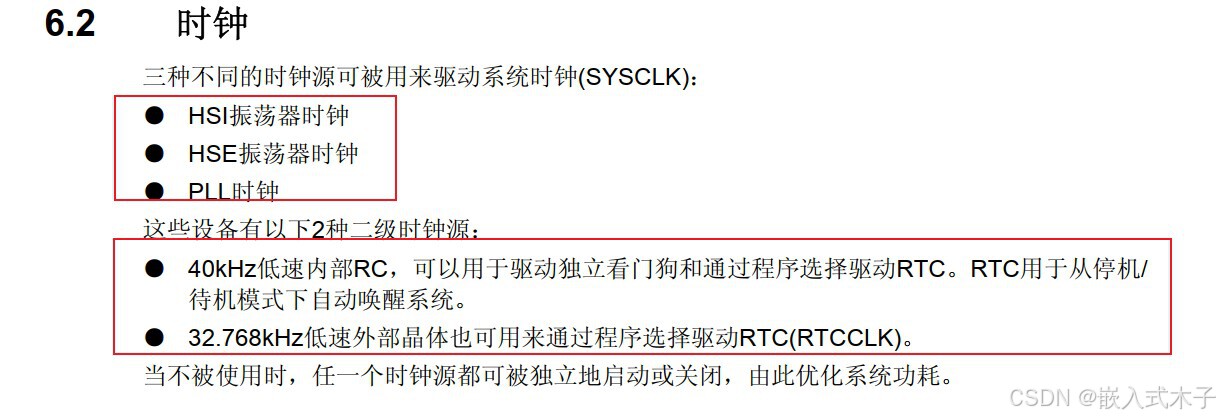

三、时钟

根据《1-STM32F10x-中文参考手册》的第6节时钟部分可知,STM32F103有5种时钟源,但是系统时钟源SYSCLK只有三种选择,HSE、HSI、PLL,LSI和LSE两种低速时钟是提供给RTC和IWDG使用。其中HSE和LSE是需要我们自己外接晶振的,HSI和LSI是STM32F103C8T6内置的,PLL是取自HSE或HSI。由于HSI不精确,所以为了系统时钟SYSCLK能达到72MHz,我们只能选择HSE。如果没有外接HSE的话,单片机会自动使用内部8MHz的HSI作为系统时钟SYSCLK,此时系统时钟就只有8MHz,且不精确。

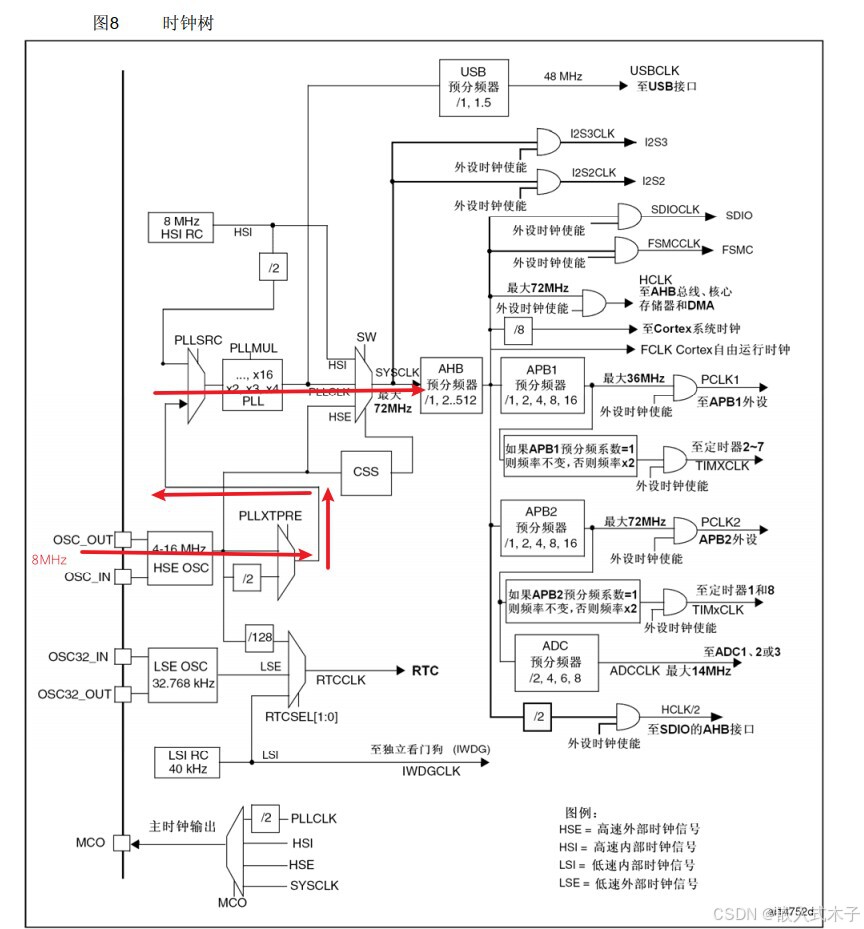

3.1 时钟树

时钟树是《1-STM32F10x-中文参考手册》的第6节时钟 的图,此图介绍了5种时钟源是如何提供给单片机内部其它外设的,我们本文主要关心图中红色线:通过外接8MHz晶振,并通过倍频器PLL进行9倍放大后,得到72MHz的系统时钟SYSCLK的过程。外接8MHz晶振我们在STM32最小系统中,我们已经连接了时钟电路,即已经接好了外部8MHz晶振,接下来我们通过SystemInit()函数 配置RCC的时钟控制寄存器CR和时钟配置寄存器CFGR,将SYSCLK配置为72MHz。

注:图中梯形表示选择器,矩形表示执行器。

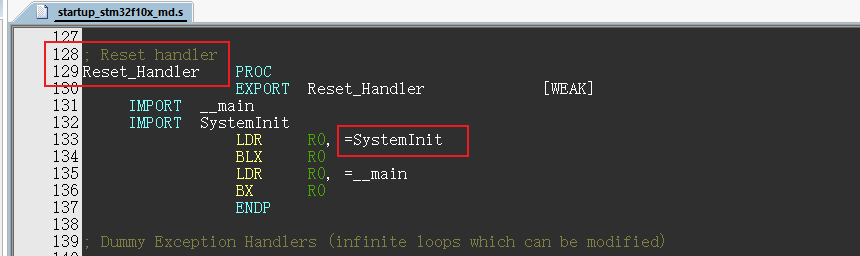

3.2 STM32启动过程

单片机上电后第一行执行的代码是汇编文件startup_stm32f10x_md.s中的Reset_Handler标签,然后执行SystemInit()后才执行main()。所以在执行我们的main()函数之前,单片机会执行SystemInit()函数将单片机时钟配置为72MHz。

Assembly

; Reset handler

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT __main

IMPORT SystemInit

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDP3.2 SystemInit()函数

在SystemInit()函数中会调用SetSysClock()--->>SetSysClockTo72(),SetSysClockTo72()执行完后STM32系统时钟为72MHz,是8MHz外部高速晶振HSE通过PLL进行9倍频后得到。

C

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F10X_CL */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#ifdef STM32F10X_CL

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}3.2.1 SystemInit()第1句:

C

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

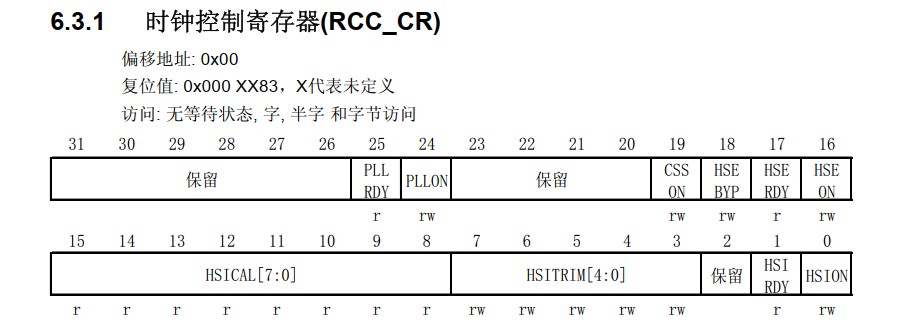

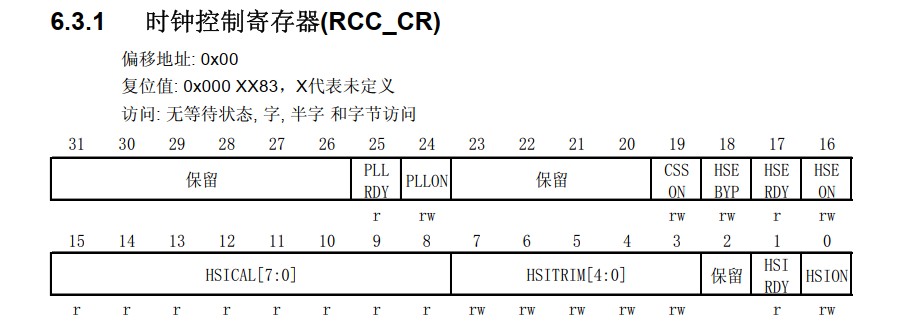

这一行通过位或运算,将RCC->CR寄存器最低位置1,开启HSI时钟。这一句其实我感觉不要也是可以的,因为手册中CR寄存器复位值是0x0000 xx83,即HSION默认值就是1。

3.2.2 SystemInit()第2句:

C

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

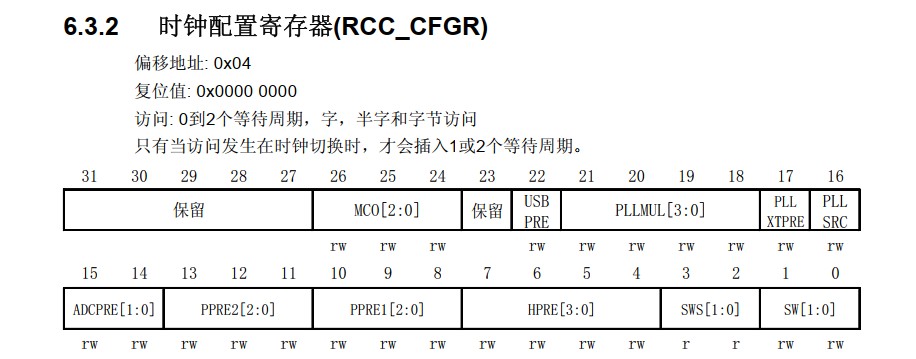

其中#ifndef STM32F10X_CL条件成立,因为在STM32F103C8T6标准库中,并没有定义这个宏,因此执行RCC->CFGR &= (uint32_t)0xF8FF0000;正如备注所示是复位SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits。对照时钟复位寄存器CFGR中说明,0x00转化二进制是0000 0000,即SW[1:0]被置为00,HPRE[3:0]被置为0000,PPRE1[2:0]被置为000,PPRE2[2:0]被置为000,ADCPRE[1:0]被置为00。0xF8转为二进制是1111 1000,即MCO[2:0]被置为000。

3.2.3 SystemInit()第3句:

C

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;这三句和备注一样,对应查看CR寄存器和CFGR寄存器对应位说明,将右边的16进制数转化位二进制后对应查看。

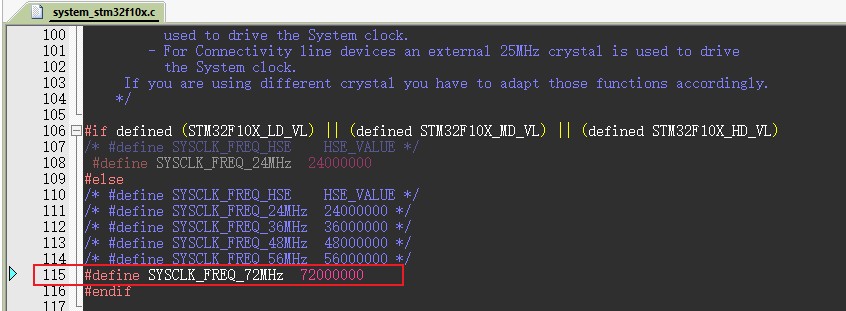

3.3 SetSysClock()函数:

C

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

/* If none of the define above is enabled, the HSI is used as System clock

source (default after reset) */

}

在system_stm32F10x.c的115行定义了宏SYSCLK_FREQ_72MHz,所以会执行 SetSysClockTo72()。

3.4 SetSysClockTo72()函数:

C

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

/* Configure PLLs ------------------------------------------------------*/

/* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz */

/* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

/* Enable PLL2 */

RCC->CR |= RCC_CR_PLL2ON;

/* Wait till PLL2 is ready */

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

#else

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif /* STM32F10X_CL */

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}在SetSysClockTo72()函数中,开启了HSE,并配置了PLL进行9倍频,然后将SYSCLK配置为72MHz。

3.4.1 SetSysClockTo72()第1句:

C

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

时钟控制寄存器CR的bit16是HSEON,将这一位置1,即可开启外部高速时钟HSE。通过按F12跳转到定义发现,在stm32f10x.h中RCC_CR_HSEON定义如下,转换成二进制后,刚好是bit16为1,通过位或运算"|="将bit16置1,而其它位不变。

C

#define RCC_CR_HSEON ((uint32_t)0x00010000) /*!< External High Speed clock enable */3.4.2 SetSysClockTo72()第2句:

C

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}等待HSE稳定,并设置超时时间HSE_STARTUP_TIMEOUT,HSE稳定后将HSEStatus标志位置1,然后进行后续配置,如果失败置为0,默认使用8MHz的HSI作为系统时钟。

3.4.3 SetSysClockTo72()第3句:

C

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2; 这几句是配置FLASH的等待周期的,详情需要查看《STM32F10xxx闪存编程手册》。

3.4.4 SetSysClockTo72()第4句:

C

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;这三句配置三条总线HCLK、PCLK2和PCLK1的时钟频率。即将PCLK2=HCLK = SYSCLK,PCLK1=HCLK/2。此时SYSCLK还不是72MHz,因为还没有配置PLL进行9倍频。

3.4.5 SetSysClockTo72()第5句:

C

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);这两句将PLL配置为对HSE进行9倍频。此时PLL时钟为72MHz。

3.4.6 SetSysClockTo72()第6句:

C

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}这几句是开启PLL时钟,并将其作为SYSCLK时钟源,等待PLL时钟稳定后,即可退出。此时SYSCLK为72MHz,PCLK2=HCLK = SYSCLK=72MHz,PCLK1=HCLK/2=36MHz。

3.4.7 SetSysClockTo72()第7句:

C

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}此段代码是 如果HSE初始化失败,那么默认使用HSI作为SYSCLK时钟,我们也可以在此处进行我们自己的处理,但是通常都不会进行处理。

四、标准库与HAL库区别

共同点 :单片机上电后会立即执行启动文件中的Reset_Handler标签,然后调用SystemInit()函数。

不同点:SystemInit()函数实现不一样,HAL库中SystemInit()函数不会调用 SetSysClock()将系统时钟初始化为72MHz,而是需要我们在main()函数中自己初始化为72Mhz。

4.1 HAL库SystemInit()函数

C

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#if !defined(STM32F105xC) && !defined(STM32F107xC)

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F105xC */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#if defined(STM32F105xC) || defined(STM32F107xC)

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined(STM32F100xB) || defined(STM32F100xE)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

#endif /* STM32F105xC */

#if defined(STM32F100xE) || defined(STM32F101xE) || defined(STM32F101xG) || defined(STM32F103xE) || defined(STM32F103xG)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}最后没有调用 SetSysClock();也就不会调用 SetSysClockTo72();

4.1 HAL库配置系统时钟为72MHz函数

C

int main(void)

{

HAL_Init(); //初始化HAL库

Stm32_Clock_Init(RCC_PLL_MUL9); //设置时钟,72M

while(1)

{

}

}需要我们编写 Stm32_Clock_Init()函数。

4.1.1 Stm32_Clock_Init函数

4.1 HAL库配置系统时钟为72MHz函数

C

void Stm32_Clock_Init(u32 PLL)

{

HAL_StatusTypeDef ret = HAL_OK;

RCC_OscInitTypeDef RCC_OscInitStructure;

RCC_ClkInitTypeDef RCC_ClkInitStructure;

RCC_OscInitStructure.OscillatorType=RCC_OSCILLATORTYPE_HSE; //时钟源为HSE

RCC_OscInitStructure.HSEState=RCC_HSE_ON; //打开HSE

RCC_OscInitStructure.HSEPredivValue=RCC_HSE_PREDIV_DIV1; //HSE预分频

RCC_OscInitStructure.PLL.PLLState=RCC_PLL_ON; //打开PLL

RCC_OscInitStructure.PLL.PLLSource=RCC_PLLSOURCE_HSE; //PLL时钟源选择HSE

RCC_OscInitStructure.PLL.PLLMUL=PLL; //主PLL倍频因子

ret=HAL_RCC_OscConfig(&RCC_OscInitStructure);//初始化

if(ret!=HAL_OK) while(1);

//选中PLL作为系统时钟源并且配置HCLK,PCLK1和PCLK2

RCC_ClkInitStructure.ClockType=(RCC_CLOCKTYPE_SYSCLK|RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2);

RCC_ClkInitStructure.SYSCLKSource=RCC_SYSCLKSOURCE_PLLCLK; //设置系统时钟时钟源为PLL

RCC_ClkInitStructure.AHBCLKDivider=RCC_SYSCLK_DIV1; //AHB分频系数为1

RCC_ClkInitStructure.APB1CLKDivider=RCC_HCLK_DIV2; //APB1分频系数为2

RCC_ClkInitStructure.APB2CLKDivider=RCC_HCLK_DIV1; //APB2分频系数为1

ret=HAL_RCC_ClockConfig(&RCC_ClkInitStructure,FLASH_LATENCY_2); //同时设置FLASH延时周期为2WS,也就是3个CPU周期。

if(ret!=HAL_OK) while(1);

}调用HAL库HAL_RCC_ClockConfig()函数实现将SYSCLK配置为72MHz。

五、总结

通过标准库和HAL库对比,将STM32系统时钟SYSCLK配置为72MHz既可以在main()函数之前,也可以在main()函数里面,即在使用其它片上外设之前都可以。虽然标准库和HAL库调用的库函数不一样,但是最底层都是配置的RCC的CR和CFGR寄存器,只是封装不同而已,所以我们得熟悉手册对RCC使用的说明,再结合标准库和HAL库进行学习,才能理解得更加透彻。