一、UDP协议FPGA IP Core 简述

UDP协议FPGA IP Core通过以太网物理层(如SFP光口或RJ45)与外部主机通信,同时利用AXI4-Stream/AXI4总线协议实现与FPGA内部逻辑的无缝桥接,兼具高速数据传输和硬件设计灵活性。

纯RTL逻辑实现:适用不同速度的以太网接口。

支持接口:支持XI_lite、AXI_full、AXI_stream 等AXI4标准的接口。

高读/写带宽:在数据可靠传输的前提下,1000M以太网接口读写实测速度大于882Mbps。

快速上手,技术支持:Verilog 代码解决方案,方便适配国产FPGA。

二、测试环境搭建

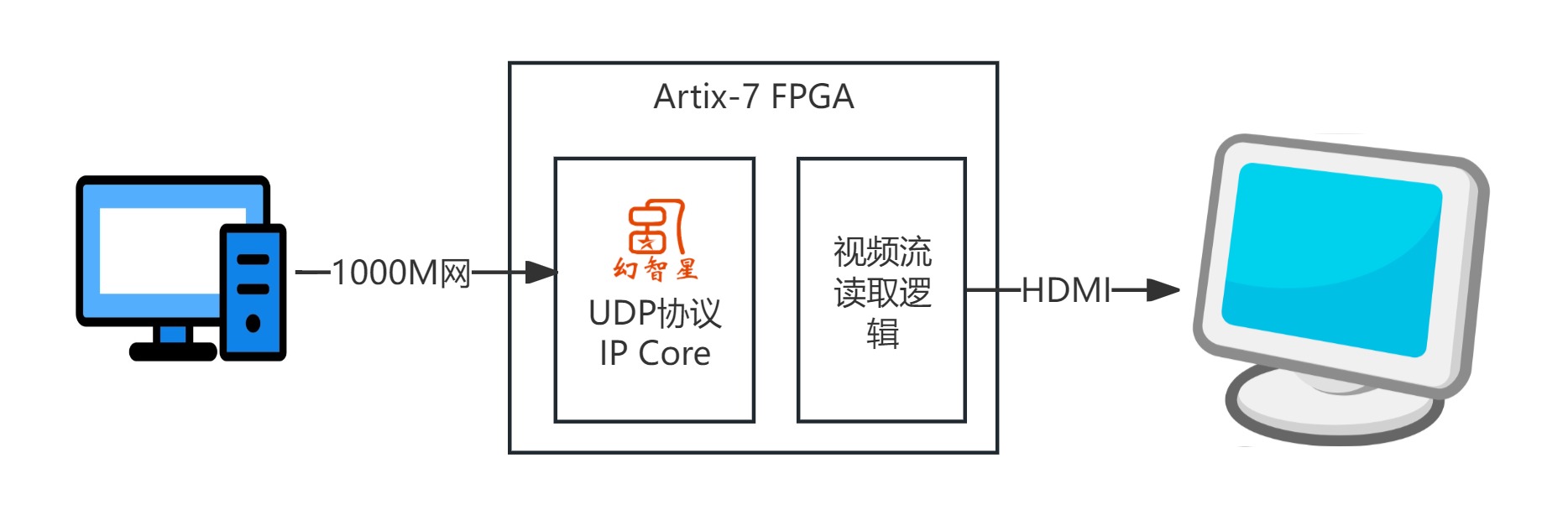

使用Xilinx fpga Artix-7 系列开发板与pc端通过1000M以太网直连。FPGA端部署UDP IP Core,PC端使用Wireshark进行数据抓包与分析,下图是连接示意图:

三、系统架构概述

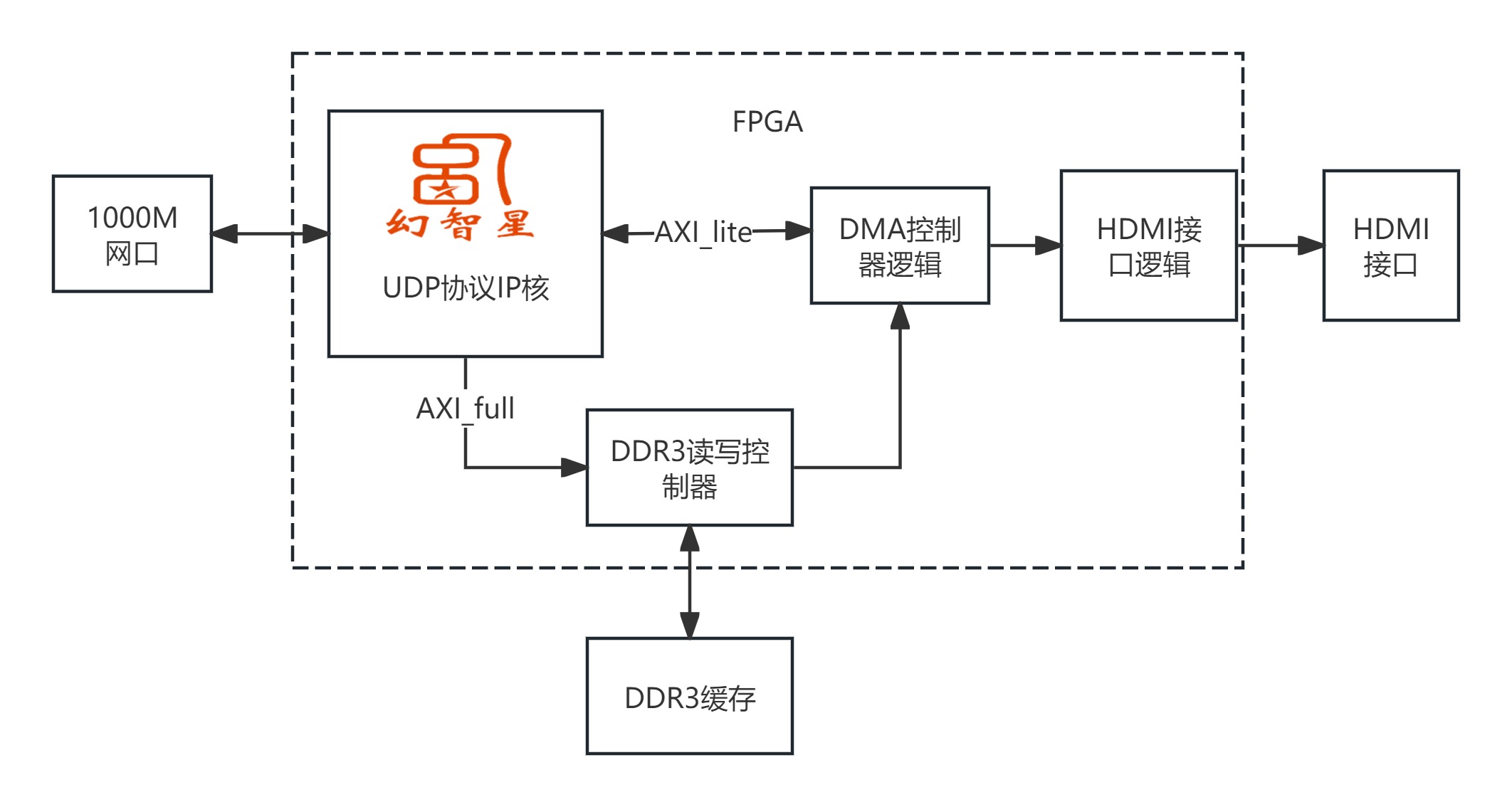

整个视频处理系统采用FPGA作为核心处理器,通过定制化的UDP协议IP核实现高速视频流接收,结合DDR3内存实现数据缓冲,最终通过DMA控制器和HDMI接口完成视频显示输出。

时序控制流程

- UDP IP核接收视频流数据包

- 数据经过协议解析后写入DDR3缓存

- DMA控制器按帧周期读取视频数据

- HDMI发送器从DMA获取数据并进行编码

- 显示器接收TMDS信号完成图像显示

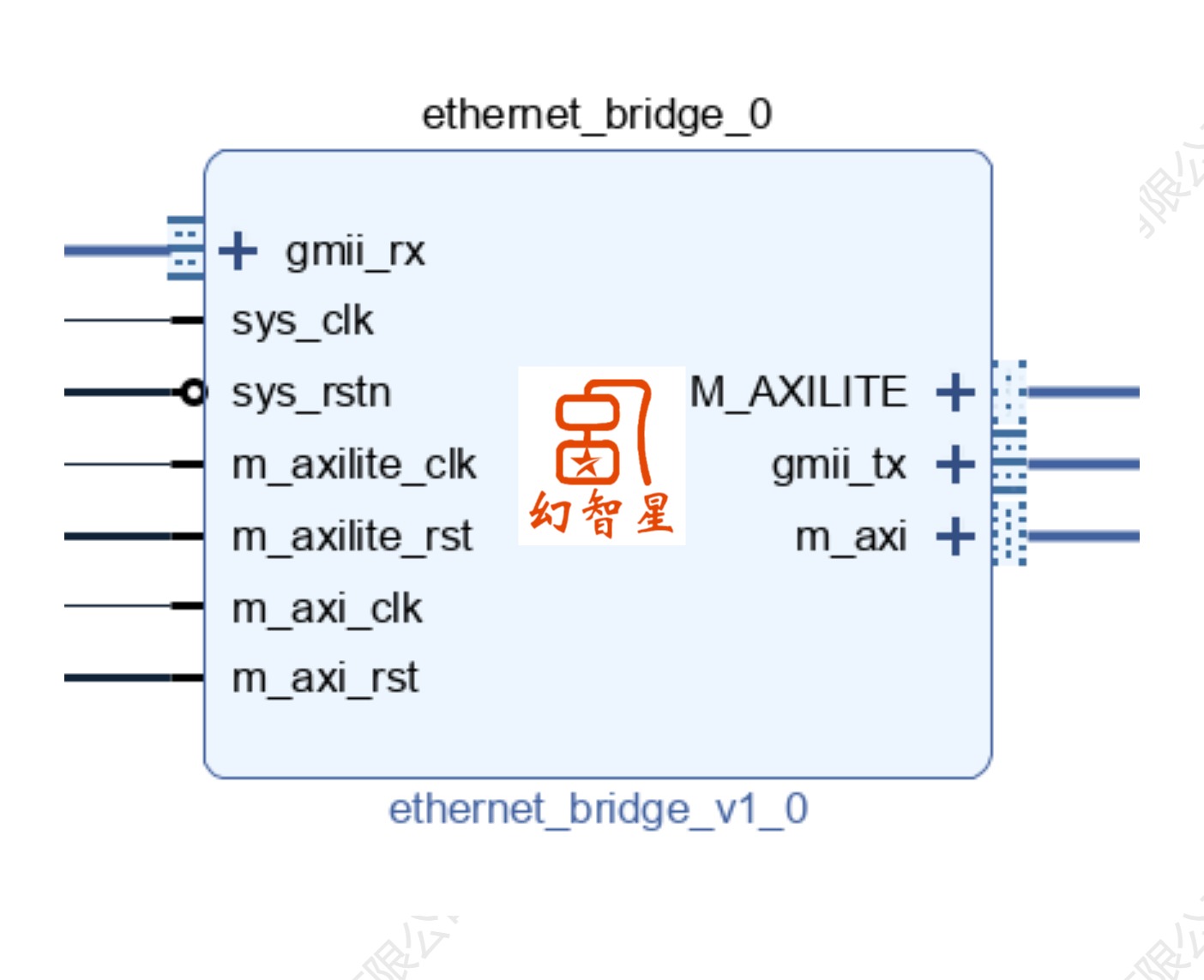

3.1、UDP协议IP核模块

幻智星科技开发的UDP协议IP Core运行在FPGA逻辑层,主要功能包括:

- 支持千兆以太网物理层接口

- 实现UDP协议栈硬件加速

- 内置数据校验和错误重传机制

3.2、DDR3缓存子系统

FPGA通过AXI4接口连接外部DDR3 SDRAM:

- 采用256位宽总线接口

- 工作频率800MHz

- 双Bank交替存储设计

- 乒乓缓冲机制确保数据连续性

3.3、 DMA传输控制器

直接内存访问控制器实现高效数据传输:

- 支持突发传输模式

- 自动地址递增

- 数据预取机制

- 传输状态寄存器组

3.4、 HDMI输出接口

视频显示子系统包含:

- 24位RGB色彩空间转换

- TMDS编码器

- EDID读取模块

- 热插拔检测电路

- 支持1080p@60Hz输出

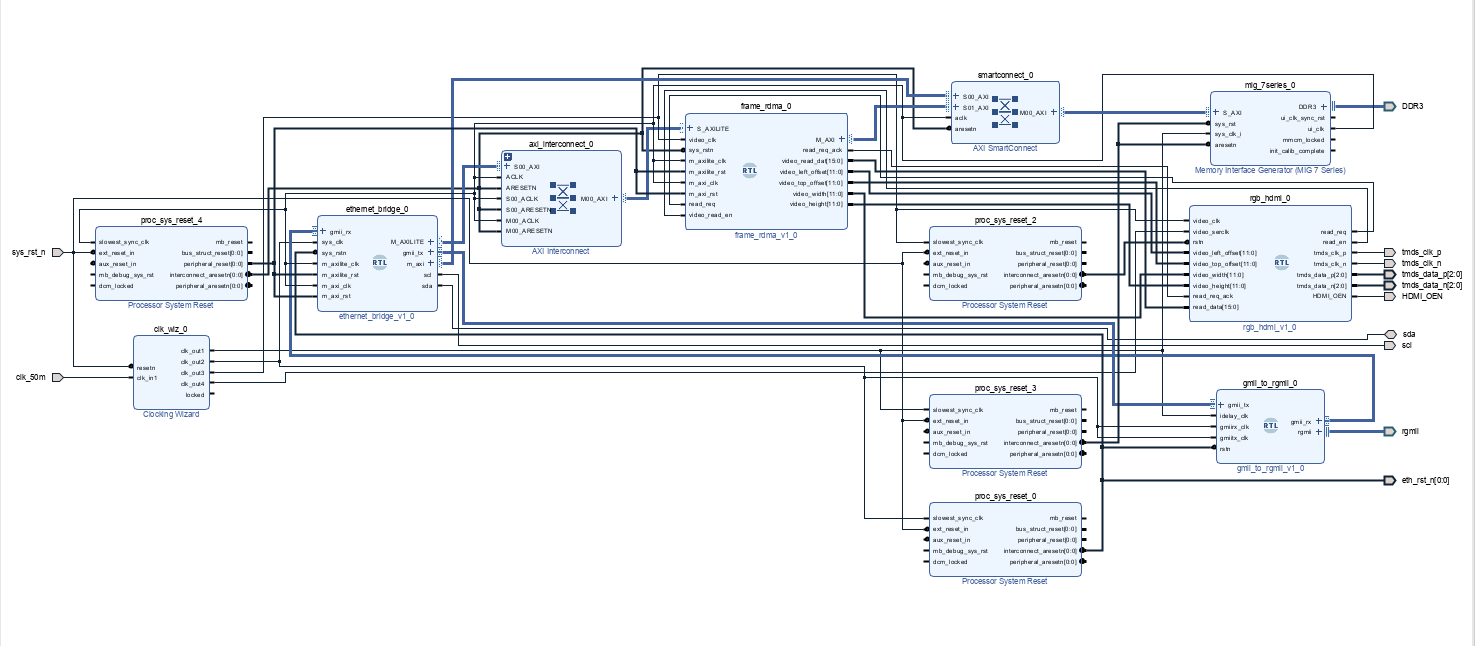

四、vivado 工程图

工程图比较复杂,这里就不细说了,直接上图。

五、pc机端测试软件

测试软件是用QT编写的,界面如下图:

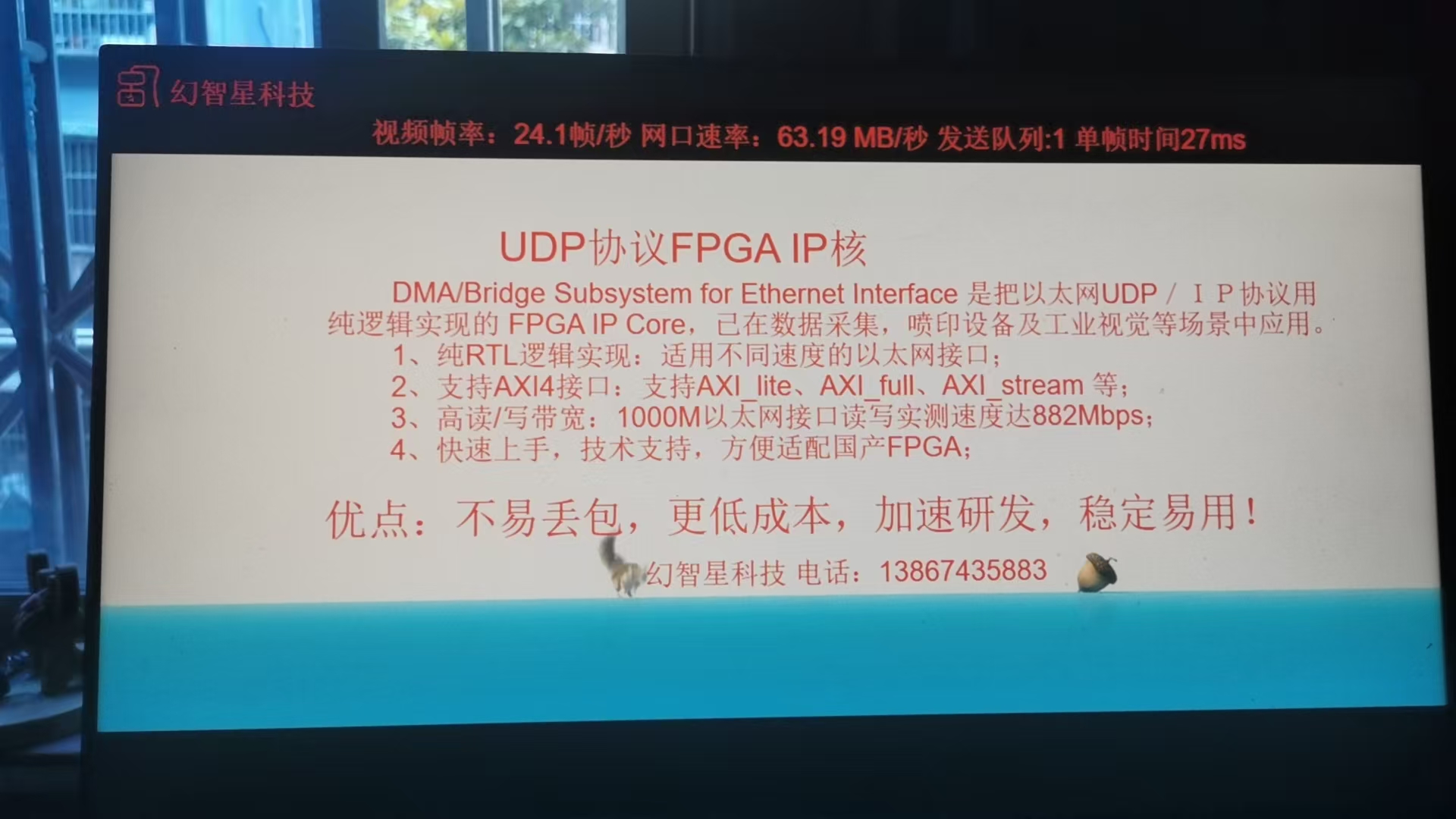

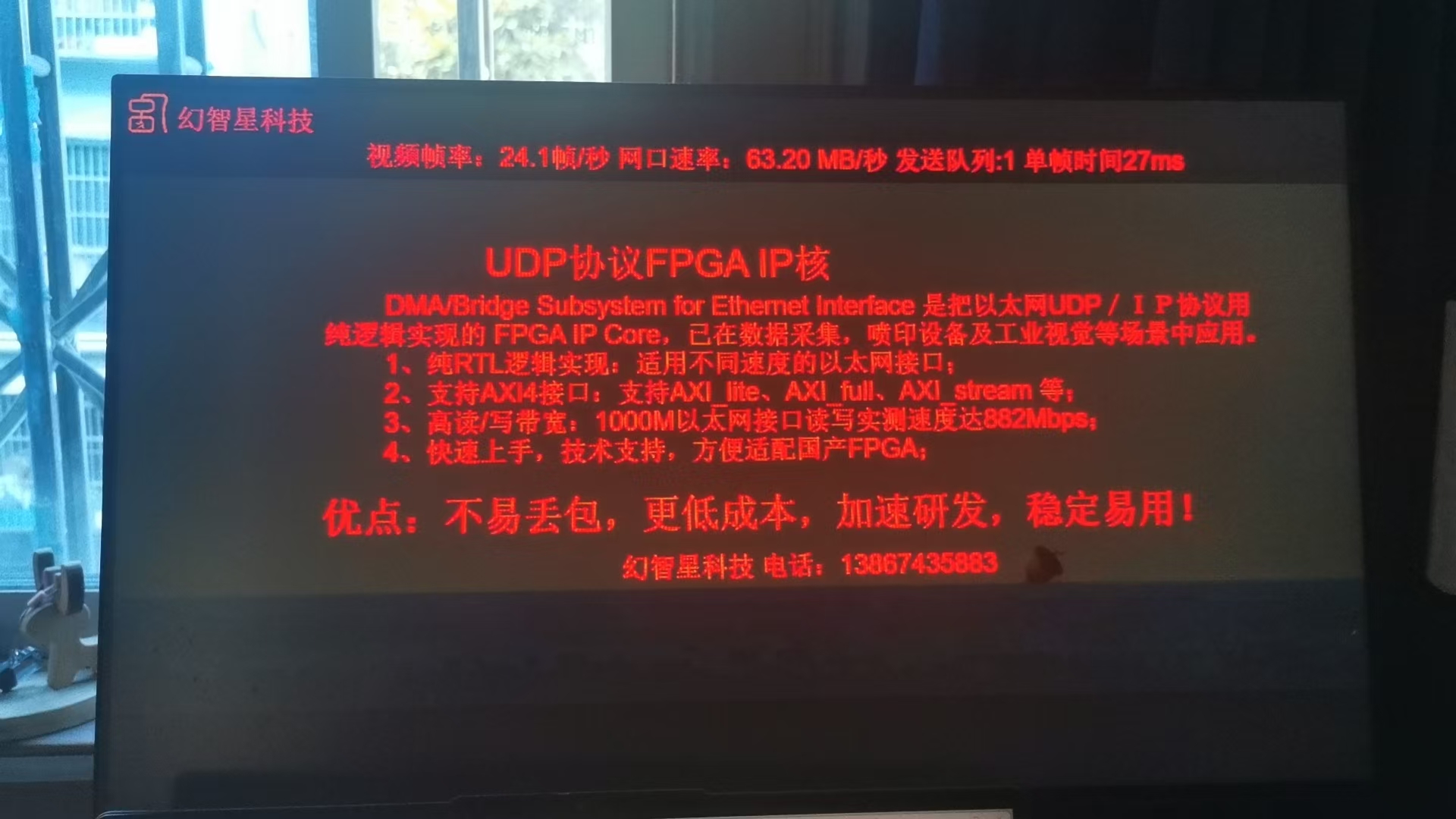

六、实测视频图片

因上传视频效果不怎么好,只能贴再上几张照片见证测试结果:

UDP协议FPGA IP Core 视频传输稳定性测试

性能指标

- 视频流帧率:24帧/秒

- 最大支持分辨率:1280*750@30Hz

- 数据传输带宽:>63.2MB/秒