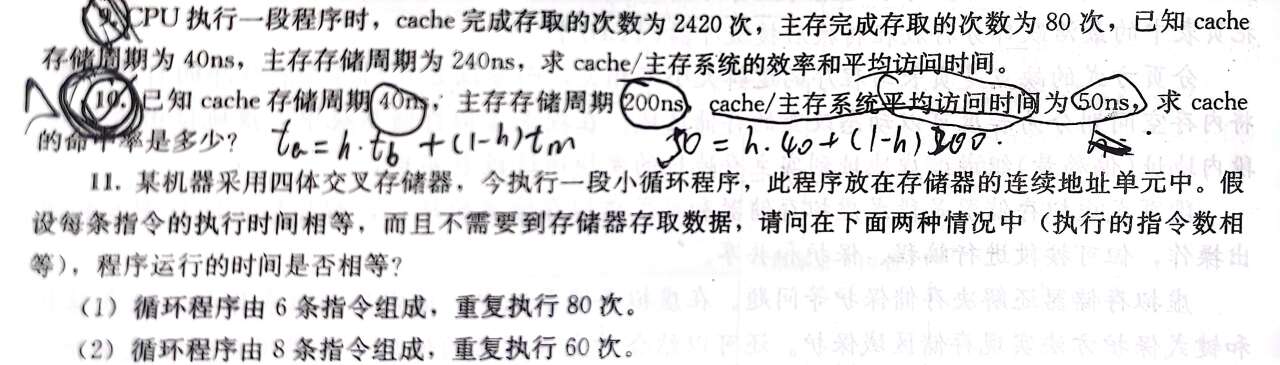

3-9

命中率

平均访问时间

cache的效率为

3-10

由题意可以设命中率为h,列方程

解得h=0.9375

3-11

(这里还是交叉存储器这块的知识)

因此不相等。

3-12

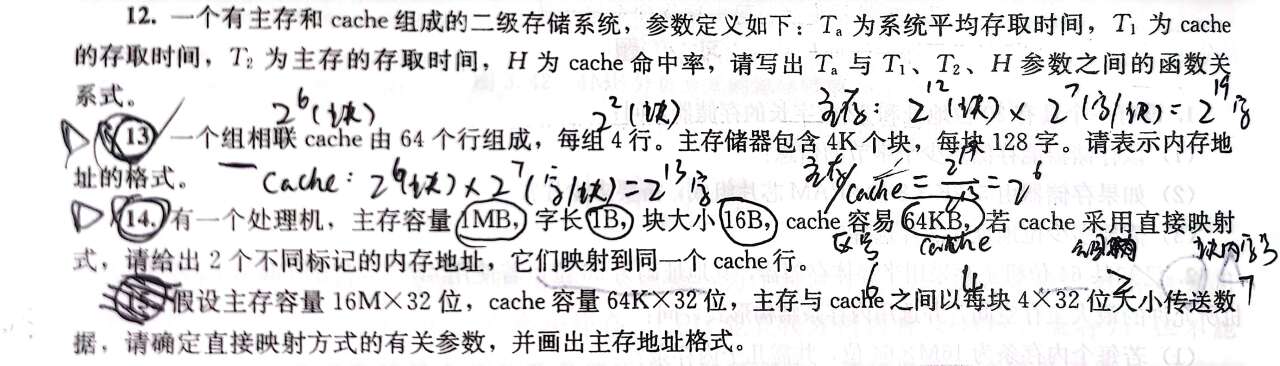

3-13

知识点定位:P95、96

主存4K=2^12个块,块地址有12位。s=12

每块128字,字地址有7位。w=7

故主存的地址格式为19位。

Cache有64行,每组4行,则共16=2^4组,组号为4位。d=4

因此,标记位s-d=8位,组号d=4位,字号w=7位。

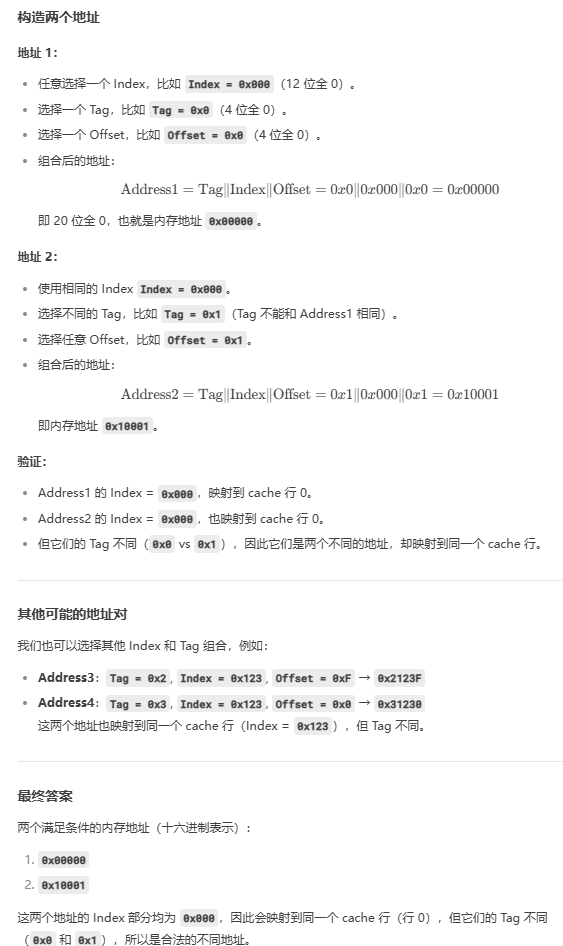

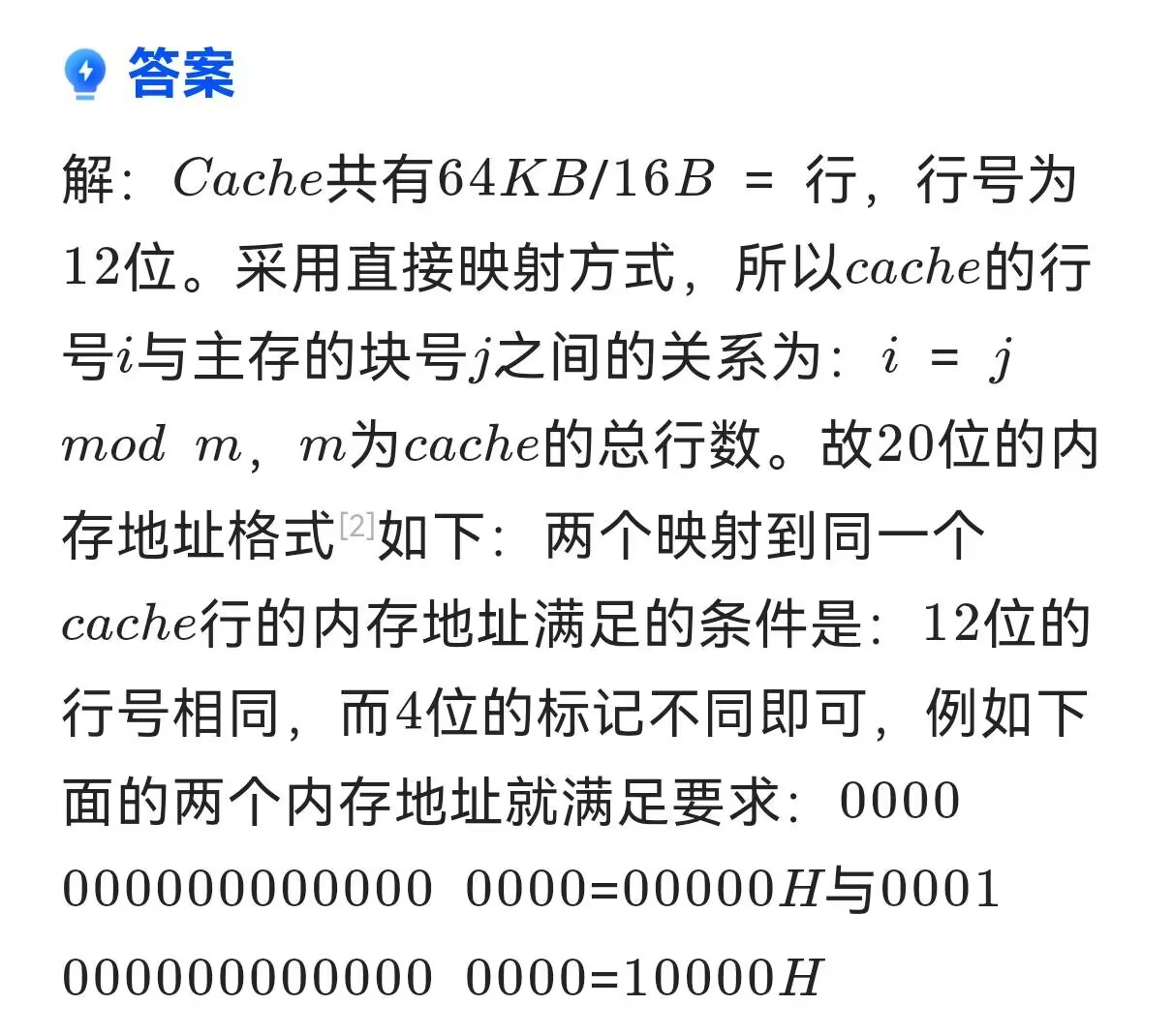

3-14

Cache共有行,行号为12位。

块大小位

主存地址总宽度为位,

所以标记位是20-4-12=4位。

然后剩下的答案我毛线看不懂了。。。

deepseek解释

小猿搜题

3-15

主存容量:16M*32位

cache容量:64K*32位

主存块、cache块大小:4*32位

那么主存块数=

cache块数=

直接映射路数=主存块数/cache块数=2^8=256

索引位位数=

标记位位数=主存地址总位数-索引位位数=24

主存地址格式为 { 标记位24位 , 索引位8位 }

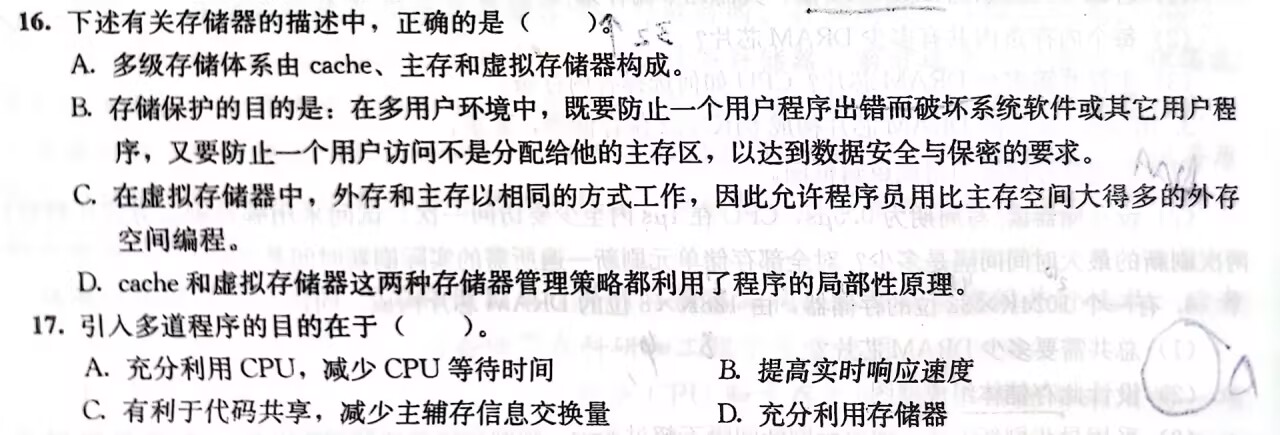

3-16

AI回答都是多选。。。

A. 错误,多级存储体系通常由 cache、主存和外存(如磁盘) 构成,虚拟存储器是一种技术,不是独立的存储层次。

B. 正确,存储保护的核心目标就是防止非法访问和程序间的相互破坏。

C. 错误,虚拟存储器虽然让外存(如磁盘)对程序员"透明",但外存和主存的工作方式不同(如磁盘需要I/O操作),访问速度差异巨大。

D. 正确,cache和虚拟存储器这两种存储器管理策略都利用了程序的局部性原理。

3-17

引入多道程序的目的在于:

A. 充分利用CPU,减少CPU等待时间

多道程序设计通过让多个程序交替执行,使CPU在某个程序等待I/O时切换到另一个程序,减少空闲时间,提高系统吞吐率。

B. 错误,实时响应速度通常由实时系统保证,多道程序可能增加调度开销。

C. 错误,代码共享和减少主辅存交换是分时系统或虚拟存储技术的优化目标,并非多道程序的核心目的。

D. 错误,多道程序主要优化CPU利用率,存储器的充分利用依赖内存管理技术(如分页、分段)。