相关阅读

SDC命令详解![]() https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

目录

set_min_capacitance命令用于设置输入端口的最小需驱动电容(设置了输入端口的min_capacitance属性),这是一种设计规则约束(Design Rule Constraint),Design Compiler进行综合时会尝试确保每个输入端口/输出引脚驱动的电容总和(包括引脚电容和互连电容)不小于设置的最小需驱动电容(优先级高于优化约束(Optimization Constraint))。

在逻辑库中可以使用库属性default_input_pin_cap或库引脚属性capacitance(优先级高于库属性)指定输入引脚的电容(对于输出端口,可以使用set_load命令指定电容,默认情况下电容为0);使用库引脚属性min_capacitance指定输出引脚的最小需驱动电容(对于输入端口,默认情况下最小需驱动电容为0)。如果想要移除最小需驱动电容,使用remove_attribute命令。

本文针对Design Compiler,但该命令同样存在于PrimeTime、IC Compiler等工具中,它们大致相同,略有差别。set_min_capacitance命令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_min_capacitance

capacitance_value

object_list

//注:该命令的object_list参数一定要放在capacitance_value参数后 指定最小需驱动电容值

capacitance_value是一个非负的电容值,代表了需要设置在对象上的最小需驱动电容,它的单位要与工艺库中指定的电容单位一致。

指定对象列表/集合

指定一个列表/集合,包含输入端口对象,需要注意的是,无法直接指定某个单元引脚的最小需驱动电容,与set_max_capacitance命令不同的是,也无法为设计对象指定最小需驱动电容。对于列表而言,如果有多于一个对象,需要使用引号或大括号包围(对使用集合无效),关于列表和集合的区别,可以参考下面的博客。

简单使用

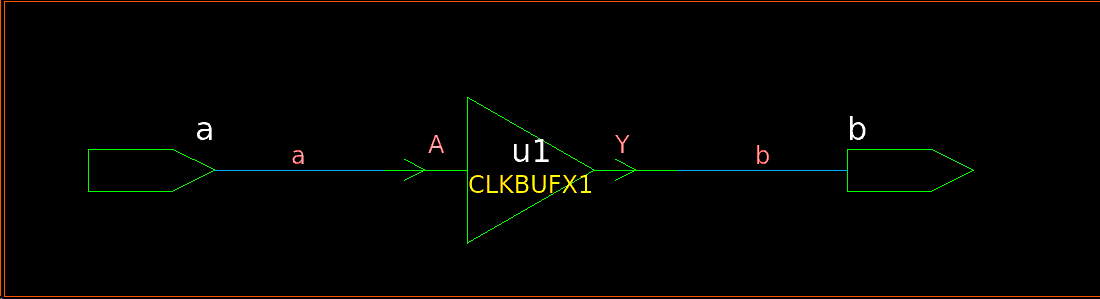

以图1所示的电路图为例,逻辑库中使用库属性default_input_pin_cap定义了电容为0.001,而库单元CLKBUFX1的输入引脚定义了库引脚属性capacitance为0.001682(优先级更高)。

图1 简单的例子

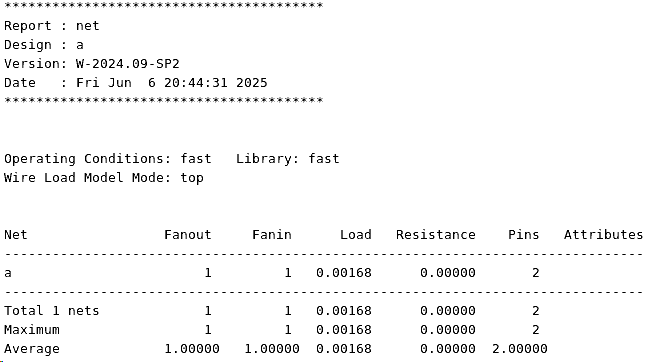

可以使用report_net [get_nets a]命令查看线网a上的总电容(假设互连电容为0),如图2所示。

图2 线网a的总电容

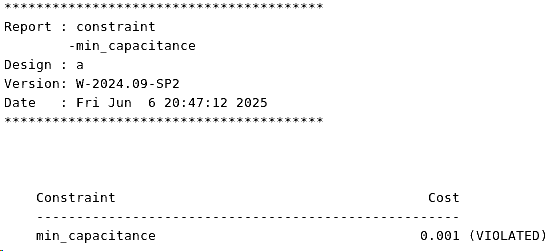

可以从图2中看出,线网a的总电容满足了库引脚属性的约束,但此时单元u1的输出引脚Y驱动的电容为0(假设互连电容为0,且如果不使用set_load命令,输出端口b的电容为0),也可以使用report_constraint -min_capacitance命令查看此时设计的整体约束情况,如图3所示,可以看出此时出现设计规则违例,代价函数的值此时恰好为0.001-0=0.001。

图3 最小需驱动电容(违例)

下面使用set_min_capacitance命令设置输入端口的最小需驱动电容为0.002。

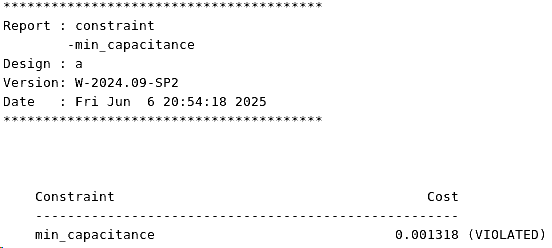

dc_shell> set_min_transition 0.002 [get_ports a]此时的整体约束情况,如图4所示,可以看出此时出现设计规则违例,代价函数的值此时恰好为0.001-0+0.002-0.001682=0.001318。

图4 最小需驱动电容(违例)

写在最后

1、在Design Compiler计算是否满足最小需驱动电容时,只会选择最小条件下线网的总电容而不会考虑最大条件下线网的总电容。