一、片上集成 IP / 功能单元(芯片 Die 内部)

1. 核心计算单元

-

CPU 核心

- 作用:通用指令执行,微架构核心

- 实现方式:大厂自研(x86/Arm 自研微架构);中小厂外购 Arm / SiFive CPU 核 IP

- 通用性:必备

-

GPU 核心

- 作用:图形渲染与通用并行计算

- 实现方式:大厂自研(如 Intel Xe、Apple GPU);中小厂外购 Imagination / Arm Mali GPU IP

- 通用性:PC/手机/汽车必备,服务器可选

-

NPU / AI 加速单元

- 作用:神经网络推理 / 训练加速

- 实现方式:大厂自研(如 Apple 神经引擎、Intel AI 引擎);中小厂外购 CEVA / Synopsys NPU IP

- 通用性:AI SoC 必备,通用芯片可选

-

DSP(数字信号处理器)

- 作用:音频、通信调制解调等实时信号处理

- 实现方式:大厂自研或外购(如 Cadence Tensilica、CEVA)

- 通用性:可选

-

FPU(浮点单元)

- 作用:高精度浮点运算

- 实现方式:通常集成在 CPU 核内,大厂自研,中小厂随 CPU 核授权获得

- 通用性:必备

2. 内存与缓存子系统

-

L1 / L2 / L3 缓存

- 作用:多级高速缓存(SRAM),减少访问主存延迟

- 实现方式:大厂自研(容量 / 关联度 / 一致性协议是性能关键);中小厂使用内存编译器生成 SRAM 宏单元

- 通用性:必备

-

内存控制器

- 作用:管理 DDR / LPDDR / HBM 协议与时序

- 实现方式:大厂自研(内存控制器优化对延迟敏感型应用至关重要);中小厂外购 Rambus / Synopsys 控制器 IP

- 通用性:必备

-

内存 PHY

- 作用:物理层接口,负责信号驱动、时序校准,与内存颗粒物理连接

- 实现方式:大厂自研;中小厂外购(Rambus、Synopsys、Cadence)

- 通用性:必备

-

缓存一致性总线

- 作用:管理多核 / 多集群缓存一致性

- 实现方式:大厂自研(如 ARM AMBA 一致性扩展、Intel 环形/网状总线);中小厂使用标准总线 IP(如 ARM CMN)

- 通用性:多核 SoC 必备

3. 高速互连与 IO 接口

-

PCIe 控制器 + PHY

- 作用:高速外设扩展(SSD、GPU、网卡等),PCIe 5.0/6.0 为当前主流

- 实现方式:大厂自研;中小厂外购 Synopsys / Cadence / Alphawave PCIe IP

- 通用性:服务器 / PC 必备

-

CXL 控制器 + PHY

- 作用:基于 PCIe 的缓存一致性互联,用于 CPU 与加速器、内存池互联

- 实现方式:大厂自研;IP 供应商开始提供 CXL 控制器 IP

- 通用性:服务器可选

-

以太网 MAC + PHY

- 作用:有线网络接口,用于服务器 CPU 的板载网络(如 100GbE)

- 实现方式:大厂自研;中小厂外购

- 通用性:可选

-

SerDes

- 作用:高速串行 / 解串器,是 PCIe、以太网、CXL 等物理层的基础。高速 SerDes(112G/224G)是技术壁垒

- 实现方式:大厂自研(英伟达、Intel、博通);中小厂外购 Alphawave / Synopsys / Cadence

- 通用性:必备(凡有高速接口的芯片)

-

USB 控制器 + PHY

- 作用:USB 接口(USB4、Type-C 等)

- 实现方式:大厂自研(如 Intel);中小厂外购

- 通用性:消费电子必备,服务器可选

-

SATA 控制器 + PHY

- 作用:传统存储接口,逐步被 PCIe/NVMe 替代

- 实现方式:外购成熟 IP

- 通用性:可选

-

MIPI 接口(DSI / CSI)

- 作用:显示 / 摄像头接口

- 实现方式:外购 MIPI IP(如 Synopsys、Cadence)

- 通用性:移动 / 汽车必备

-

I3C / I2C / SPI / QSPI

- 作用:低速外设控制总线,连接传感器、触摸屏、EEPROM 等

- 实现方式:通常外购或使用开源 IP

- 通用性:必备

-

GPIO

- 作用:通用输入输出,用于控制 LED、按键、中断等

- 实现方式:必备基础 IO 单元,通常由晶圆厂提供或设计服务公司集成

- 通用性:必备

-

SD / eMMC 接口

- 作用:存储卡 / 嵌入式存储

- 实现方式:外购 IP

- 通用性:可选

4. 显示与多媒体

-

显示控制器

- 作用:管理显示输出(DP / HDMI / eDP),处理屏幕刷新、分辨率缩放

- 实现方式:大厂自研;中小厂外购

- 通用性:PC / 移动必备,服务器可选

-

HDMI / DP PHY

- 作用:显示接口物理层,负责信号输出

- 实现方式:外购(如 Synopsys、Analogix)

- 通用性:PC / 移动必备,服务器可选

-

视频编解码器

- 作用:硬件加速 H.264 / H.265 / AV1 等视频格式编解码

- 实现方式:大厂自研(如 Intel Quick Sync);中小厂外购(如芯原 VPU IP)

- 通用性:可选

-

音频 DSP + 接口

- 作用:音频处理与输出(I2S、HDA)

- 实现方式:外购成熟 IP

- 通用性:可选

5. 片上基础架构与安全

-

片上互联(NoC / 总线)

- 作用:连接所有模块的通信骨干,决定数据吞吐与延迟

- 实现方式:大厂自研互连架构(核心性能优化点);中小厂外购 Arteris 等 NoC IP

- 通用性:必备

-

时钟管理单元(PLL)

- 作用:时钟生成与分配,支持动态频率调整

- 实现方式:大厂自研(频率与功耗平衡是关键);中小厂外购 PLL IP

- 通用性:必备

-

电源管理单元(PMU)

- 作用:电压域控制、DVFS(动态电压频率调整)、上电时序

- 实现方式:大厂自研(功耗优化核心);可外购部分模拟 IP

- 通用性:必备

-

安全模块

- 作用:加密引擎(AES/SHA/RSA)、真随机数生成器(TRNG)、安全启动、可信执行环境(如 Intel SGX/TDX)

- 实现方式:大厂自研安全架构;可外购安全 IP(如 Rambus)

- 通用性:消费 / 服务器必备

-

调试与追踪单元

- 作用:JTAG、嵌入式追踪、性能监测

- 实现方式:部分自研,部分使用 EDA 工具生成

- 通用性:必备(开发调试阶段)

-

可测试性设计(DFT)逻辑

- 作用:扫描链、BIST 等测试电路,用于芯片制造测试

- 实现方式:由 EDA 工具插入,非人工设计

- 通用性:必备(制造测试)

6. 模拟与混合信号 IP

-

ADC / DAC

- 作用:模数 / 数模转换,用于温度传感、电压监测、音频输入输出、射频接收等

- 实现方式:大厂自研或外购

- 通用性:必备(至少集成少量 ADC)

-

温度传感器

- 作用:芯片结温监测,用于热管理、动态降频

- 实现方式:大厂自研;中小厂外购

- 通用性:必备

-

电压 / 电流传感器

- 作用:供电状态监测,配合 PMU 实现精确 DVFS 控制

- 实现方式:可选,多集成在 PMU 内

- 通用性:可选

-

上电复位(POR)

- 作用:芯片上电时复位所有寄存器,保证逻辑从确定状态启动

- 实现方式:必备基础模拟电路,通常由晶圆厂提供

- 通用性:必备

-

内部振荡器(RC)

- 作用:基础时钟源,用于启动和低功耗模式

- 实现方式:必备基础模拟电路,通常由晶圆厂提供

- 通用性:必备

-

晶体振荡器接口

- 作用:外接高精度晶振,提供精确时钟

- 实现方式:必备基础电路,通常由晶圆厂提供

- 通用性:必备(需求精确时钟时)

7. 基础库与辅助 IP

-

标准单元库

- 作用:基础逻辑门(与、或、非、触发器等),数字电路的基础建材

- 实现方式:由晶圆厂或第三方提供,适配特定工艺,设计公司直接使用

- 通用性:必备

-

内存编译器(SRAM Compiler)

- 作用:生成定制化片上 SRAM,用于缓存、寄存器文件、缓冲区

- 实现方式:由晶圆厂或 EDA 厂商提供,设计公司调用

- 通用性:必备

-

ROM 编译器

- 作用:生成只读存储器,用于存储启动代码

- 实现方式:由晶圆厂或 EDA 厂商提供

- 通用性:必备

-

GPIO 单元

- 作用:引脚驱动、电平转换、ESD 防护

- 实现方式:由晶圆厂提供 I/O 库,设计公司直接使用

- 通用性:必备

-

ESD 保护单元

- 作用:静电放电保护,每个芯片引脚都需要

- 实现方式:由晶圆厂提供,设计公司集成

- 通用性:必备

8. 封装与 Die-to-Die 互连 IP(Chiplet 架构)

-

Die-to-Die 接口(UCIe / BoW / OpenHBI)

- 作用:多芯片封装内互连,用于连接计算芯粒、IO 芯粒、HBM

- 实现方式:大厂自研或外购(如 Alphawave、Synopsys 的 UCIe IP)

- 适用场景:采用 Chiplet 设计的芯片

-

TSV / 微凸块接口

- 作用:3D 堆叠互连,用于 HBM 与主芯片的连接,或逻辑芯片与 SRAM 堆叠

- 实现方式:需与晶圆厂 3D 封装工艺协同设计

- 适用场景:需要 HBM 或 3D 堆叠的芯片

-

芯片间互连控制器(CXL / CCIX / 私有)

- 作用:管理多芯片一致性协议,如 NVLink-C2C

- 实现方式:大厂自研或外购

- 适用场景:多 Die 服务器 SoC

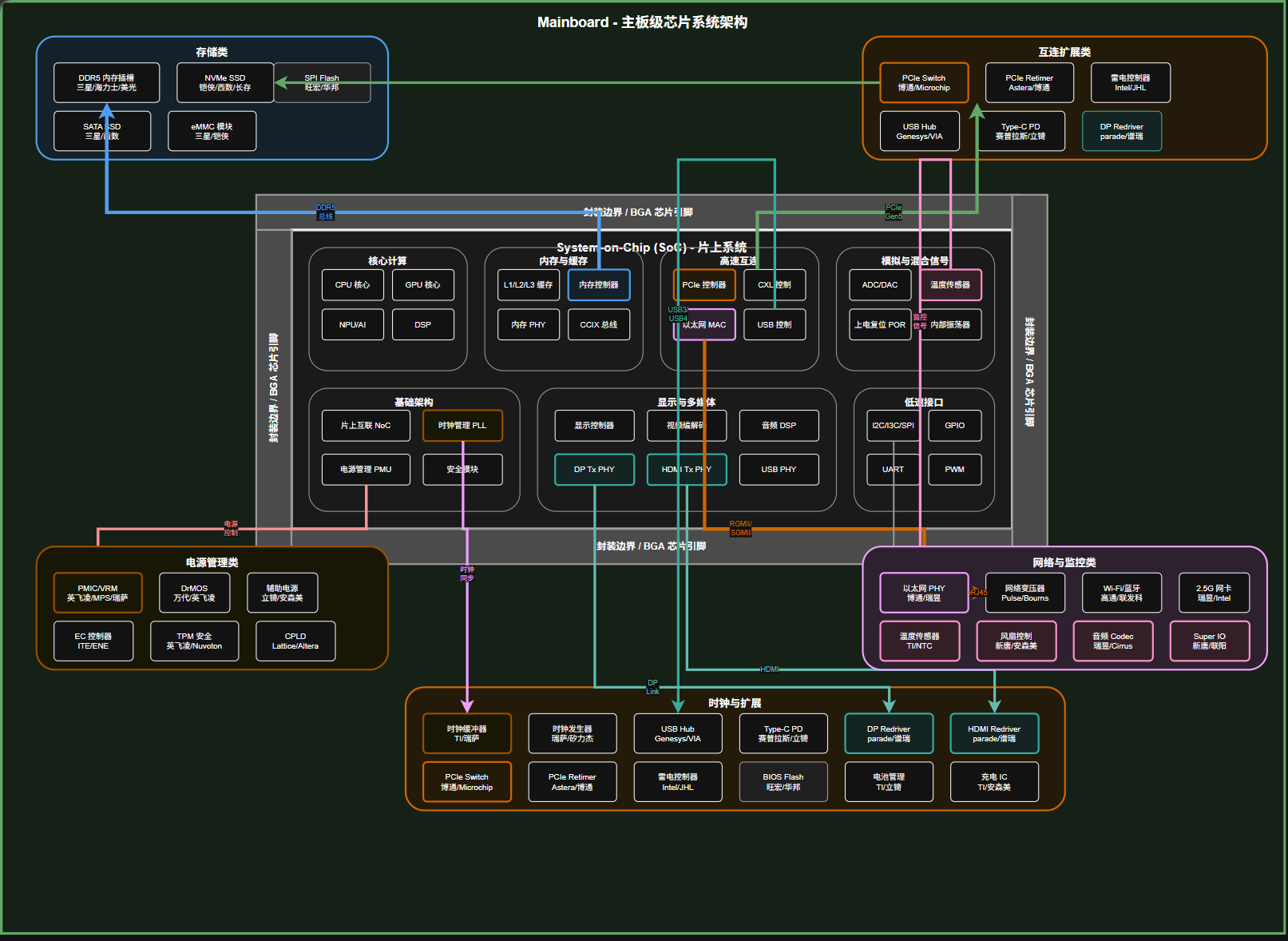

二、片外配套芯片(主板 / 系统级)

这些是独立元器件,与主芯片配合完成完整系统功能。

存储类

-

DDR / HBM 内存颗粒

- 作用:系统主存

- 典型供应商:三星、海力士、美光

-

NAND 闪存 / SSD

- 作用:非易失性存储

- 典型供应商:铠侠、西部数据、长江存储、三星、海力士

互连扩展类

-

PCIe Switch / Retimer

- 作用:扩展 PCIe 通道、信号重定时,用于多 GPU / NVMe 连接

- 典型供应商:博通、Microchip、Astera Labs

-

时钟缓冲器 / 时钟发生器

- 作用:为高速接口提供低抖动时钟

- 典型供应商:TI、瑞萨、Silicon Labs

电源管理类

-

多相 PMIC / VRM

- 作用:CPU / GPU 核心供电,多相电压调节模组

- 典型供应商:英飞凌、MPS、瑞萨、TI

-

辅助电源芯片

- 作用:主板 IO、内存供电

- 典型供应商:立锜、安森美

网络与通信类

-

以太网 PHY

- 作用:若主芯片未集成以太网 MAC/PHY,需独立 PHY 芯片

- 典型供应商:博通、瑞昱、Marvell

-

Wi-Fi / 蓝牙模块

- 作用:无线连接

- 典型供应商:博通、高通、联发科

音频类

- 音频 Codec

- 作用:音频输入输出转换

- 典型供应商:瑞昱、Cirrus Logic

接口与监控类

-

Super IO

- 作用:低速接口管理(风扇控制、串口、PS/2 等)

- 典型供应商:新唐、联阳

-

温度传感器 / 风扇控制器

- 作用:系统散热管理

- 典型供应商:TI、Maxim(ADI)

说明

-

"大厂自研" vs "中小厂外购"

大厂(Intel、AMD、苹果、英伟达、海思等)具备全栈自研能力,上述列表中绝大多数片上 IP 均为自研,尤其是 CPU 核、互连、内存控制器、高速 SerDes 等决定性能的核心模块。中小 SoC 设计公司则外购大部分数字 IP 和物理 IP,通过设计服务公司完成整合与后端。

-

"必备"与"可选"

基于通用 SoC(如手机、PC、服务器)的一般需求划分。对于极简微控制器(MCU),部分类别(如 GPU、高速接口)自然省略。

-

Chiplet 相关 IP

正在成为高性能芯片的主流选择,但传统单片式芯片不包含此类 IP。

-

模拟混合信号 IP

虽然面积占比小,却是芯片正常工作不可或缺的部分,每颗芯片均包含基本模拟单元(POR、振荡器、少量 ADC 等)。