相关阅读

Power Compiler![]() https://blog.csdn.net/weixin_45791458/category_13013065.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_13013065.html?spm=1001.2014.3001.5482

正如下面的博客所说,从2007版本开始,Power Compiler已经支持UPF标准,并用于指定多电压设计的低功耗设计意图。Design Compiler:两种工作模式(线负载模式和拓扑模式)![]() https://blog.csdn.net/weixin_45791458/article/details/144830461?spm=1001.2014.3001.5501

https://blog.csdn.net/weixin_45791458/article/details/144830461?spm=1001.2014.3001.5501

本文将讨论Power Compiler在UPF模式下是如何对单元进行映射的,但是本文不涉及多工艺角和多工作模式(Multicorner-Multimode, MCMM),关于它的更多介绍,可以参考下面的博客。如果一个设计是MCMM模式下的多电压设计,需要同时满足两者的规则。

下面将用一个简单的例子进行说明,例1展示了一段RTL代码,其中顶层模块top的设计电压是1.16V,下面有两个子模块sub1和sub2,设计电压为分别是0.95V和1.16V。

// 例1

// 顶层模块(1.16V电压域)

module top #(parameter WIDTH = 8)

(

input wire clk,

input wire rst_n,

input wire [WIDTH-1:0] data_in,

output wire [WIDTH-1:0] data_out

);

wire [WIDTH-1:0] data_sub;

// 子模块1(0.95V 电压域)

submodule1 #(

.WIDTH(WIDTH)

) sub1 (

.clk (clk),

.rst_n (rst_n),

.data_in (data_in),

.data_out(data_sub)

);

// 子模块2(1.16V 电压域)

submodule2 #(

.WIDTH(WIDTH)

) sub2 (

.clk (clk),

.rst_n (rst_n),

.data_in (data_sub),

.data_out(data_out)

);

endmodule

// 子模块1(0.95V电压域)

module submodule1 #(parameter WIDTH = 8)

(

input wire clk,

input wire rst_n,

input wire [WIDTH-1:0] data_in,

output reg [WIDTH-1:0] data_out

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

data_out <= {WIDTH{1'b0}};

else

data_out <= data_in + 1'b1;

end

endmodule

// 子模块2(1.16V电压域)

module submodule2 #(parameter WIDTH = 8)

(

input wire clk,

input wire rst_n,

input wire [WIDTH-1:0] data_in,

output reg [WIDTH-1:0] data_out

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

data_out <= {WIDTH{1'b0}};

else

data_out <= data_in + 2'd2;

end

endmodule首先是逻辑库准备环节,为了满足多电压设计,需要1.16V和0.95V的标准单元库以及1.16V到0.95V和0.95V到1.16V的电压转换器(Level Shifter)库,如下列表所示。

saed32hvt_ff1p16v125c.db

saed32hvt_ff0p95v125c.db

saed32hvt_dlvl_ff0p95v125c_i1p16v.db

saed32hvt_ulvl_ff1p16v125c_i0p95v.db为了让Power Compiler将各模块中的单元映射到对应电压的逻辑库,需要使用使用set_voltage命令指定各电压域的工作电压,使用set_operating_conditions命令指定整个设计的工作温度和工作工艺。在此之前首先需要一个UPF脚本创建电压域,如下所示。

# top.upf

#========================================================

# Top domain : 1.16V

#========================================================

create_supply_net VDD

create_supply_net VSS

create_supply_set ss_top \

-function {power VDD} \

-function {ground VSS}

create_power_domain PD_top -include_scope -supply {primary ss_top}

create_supply_port VDD

create_supply_port VSS

connect_supply_net VDD -ports VDD

connect_supply_net VSS -ports VSS

add_power_state -supply ss_top -state ON_1p16 { \

-supply_expr { power == {FULL_ON 1.16} && ground == {FULL_ON 0.0} }

}

#========================================================

# Sub1 domain : 0.95V

#========================================================

create_supply_net VDD_sub1

create_supply_set ss_sub1 \

-function {power VDD_sub1} \

-function {ground VSS}

create_power_domain PD_sub1 -elements {sub1} -supply {primary ss_sub1}

create_supply_port VDD_sub1

connect_supply_net VDD_sub1 -ports VDD_sub1

add_power_state -supply ss_sub1 -state ON_0p95 { \

-supply_expr { power == {FULL_ON 0.95} && ground == {FULL_ON 0.0} }

}

#========================================================

# Sub2 domain : 1.16V

#========================================================

create_supply_net VDD_sub2

create_supply_set ss_sub2 \

-function {power VDD_sub2} \

-function {ground VSS}

create_power_domain PD_sub2 -elements {sub2} -supply {primary ss_sub2}

create_supply_port VDD_sub2

connect_supply_net VDD_sub2 -ports VDD_sub2

add_power_state -supply ss_sub2 -state ON_1p16 { \

-supply_expr { power == {FULL_ON 1.16} && ground == {FULL_ON 0.0} }

}

#========================================================

# System power state

#========================================================

create_power_state_group PST

add_power_state -group PST -state RUN {

-logic_expr { ss_top == ON_1p16 && ss_sub1 == ON_0p95 && ss_sub2 == ON_1p16 }

}包含set_voltage命令和set_operating_conditions命令的SDC脚本如下所示。

# top.sdc

set_operating_conditions ff1p16v125c -library saed32hvt_ff1p16v125c

set_voltage -object_list VDD 1.16

set_voltage -object_list VDD_sub1 0.95

set_voltage -object_list VDD_sub2 1.16

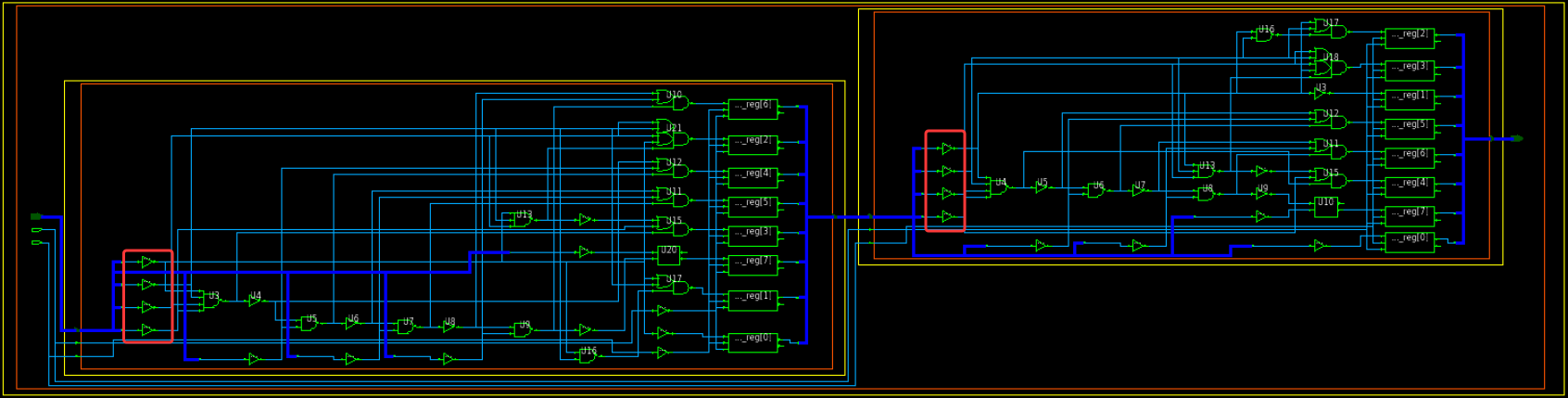

set_voltage -object_list VSS 0.0综合脚本如下所示,综合结果如图1所示,其中红色框内的就是因为跨电压域而插入的电压转换器。

# top.tcl

set target_library "./lib/saed32hvt_ff1p16v125c.db \

./lib/saed32hvt_ff0p95v125c.db \

./lib/saed32hvt_dlvl_ff0p95v125c_i1p16v.db \

./lib/saed32hvt_ulvl_ff1p16v125c_i0p95v.db"

set link_library "* $target_library"

read_verilog ./rtl/top.v

load_upf ./top.upf

source ./top.sdc

insert_mv_cells

compile_ultra

图1 例1的综合结果

使用report_cell命令可以查看单元信息,从V:T:P列可以观察到,子模块sub2中的标准单元被映射到了1.16V的标准单元库saed32hvt_ff1p16v125c,而且还有来自电压转换器库saed32hvt_ulvl_ff1p16v125c_i0p95v的0.95V到1.16V的电压转换器;子模块sub2中的标准单元被映射到了1.16V的标准单元库saed32hvt_ff0p95v125c,而且还有来自电压转换器库saed32hvt_dlvl_ff0p95v125c_i1p16v的1.16V到0.95V的电压转换器(这里显示的是0.95V到0.95V是因为该电压转换器是高到低转换,可以只使用目标电压域的电源)。需要注意的是,只有使用UPF命令才会使Power Compiler根据电压进行映射,report_cell命令的结果也才会显示V:T:P列,

dc_shell> report_cell sub2/*

****************************************

Report : cell

Design : top

Version: W-2024.09-SP5

Date : Thu Mar 26 22:26:31 2026

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

lo - local optimization is disabled

n - noncombinational

r - removable

ry - resynthesis is disabled

st - structuring is off

u - contains unmapped logic

Cell Reference Library Area Attributes V:T:P

--------------------------------------------------------------------------------

sub2/U3 INVX0_HVT saed32hvt_ff1p16v125c

1.270720 1.16:125.00:1.01

sub2/U4 NAND4X0_HVT saed32hvt_ff1p16v125c

2.033152 1.16:125.00:1.01

sub2/U5 INVX0_HVT saed32hvt_ff1p16v125c

1.270720 1.16:125.00:1.01

sub2/U6 NAND2X0_HVT saed32hvt_ff1p16v125c

1.524864 1.16:125.00:1.01

sub2/U7 INVX0_HVT saed32hvt_ff1p16v125c

1.270720 1.16:125.00:1.01

sub2/U8 NAND2X0_HVT saed32hvt_ff1p16v125c

1.524864 1.16:125.00:1.01

sub2/U9 INVX0_HVT saed32hvt_ff1p16v125c

1.270720 1.16:125.00:1.01

sub2/U10 HADDX1_HVT saed32hvt_ff1p16v125c

3.303872

r 1.16:125.00:1.01

sub2/U11 OA21X1_HVT saed32hvt_ff1p16v125c

2.541440 1.16:125.00:1.01

sub2/U12 OA21X1_HVT saed32hvt_ff1p16v125c

2.541440 1.16:125.00:1.01

sub2/U13 NAND3X0_HVT saed32hvt_ff1p16v125c

1.779008 1.16:125.00:1.01

sub2/U14 INVX0_HVT saed32hvt_ff1p16v125c

1.270720 1.16:125.00:1.01

sub2/U15 OA21X1_HVT saed32hvt_ff1p16v125c

2.541440 1.16:125.00:1.01

sub2/U16 NAND2X0_HVT saed32hvt_ff1p16v125c

1.524864 1.16:125.00:1.01

sub2/U17 OA21X1_HVT saed32hvt_ff1p16v125c

2.541440 1.16:125.00:1.01

sub2/U18 OA221X1_HVT saed32hvt_ff1p16v125c

3.049728 1.16:125.00:1.01

sub2/data_in[0]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[1]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[2]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[3]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[4]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[5]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[6]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_in[7]_UPF_LS LSUPX1_HVT saed32hvt_ulvl_ff1p16v125c_i0p95v

7.116032

lo, ry, st 0.95->1.16:125.00:1.01

sub2/data_out_reg[0] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[1] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[2] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[3] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[4] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[5] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[6] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

sub2/data_out_reg[7] DFFARX1_HVT saed32hvt_ff1p16v125c

7.116032

n 1.16:125.00:1.01

--------------------------------------------------------------------------------

Total 32 cells 145.116226

dc_shell> report_cell sub1/*

****************************************

Report : cell

Design : top

Version: W-2024.09-SP5

Date : Thu Mar 26 22:31:33 2026

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

lo - local optimization is disabled

n - noncombinational

r - removable

ry - resynthesis is disabled

st - structuring is off

u - contains unmapped logic

Cell Reference Library Area Attributes V:T:P

--------------------------------------------------------------------------------

sub1/U3 NAND4X0_HVT saed32hvt_ff0p95v125c

2.033152 0.95:125.00:1.01

sub1/U4 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U5 NAND2X0_HVT saed32hvt_ff0p95v125c

1.524864 0.95:125.00:1.01

sub1/U6 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U7 NAND2X0_HVT saed32hvt_ff0p95v125c

1.524864 0.95:125.00:1.01

sub1/U8 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U9 NAND2X0_HVT saed32hvt_ff0p95v125c

1.524864 0.95:125.00:1.01

sub1/U10 OA21X1_HVT saed32hvt_ff0p95v125c

2.541440 0.95:125.00:1.01

sub1/U11 OA21X1_HVT saed32hvt_ff0p95v125c

2.541440 0.95:125.00:1.01

sub1/U12 OA21X1_HVT saed32hvt_ff0p95v125c

2.541440 0.95:125.00:1.01

sub1/U13 NAND3X0_HVT saed32hvt_ff0p95v125c

1.779008 0.95:125.00:1.01

sub1/U14 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U15 OA21X1_HVT saed32hvt_ff0p95v125c

2.541440 0.95:125.00:1.01

sub1/U16 NAND2X0_HVT saed32hvt_ff0p95v125c

1.524864 0.95:125.00:1.01

sub1/U17 OA21X1_HVT saed32hvt_ff0p95v125c

2.541440 0.95:125.00:1.01

sub1/U18 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U19 INVX0_HVT saed32hvt_ff0p95v125c

1.270720 0.95:125.00:1.01

sub1/U20 HADDX1_HVT saed32hvt_ff0p95v125c

3.303872

r 0.95:125.00:1.01

sub1/U21 OA221X1_HVT saed32hvt_ff0p95v125c

3.049728 0.95:125.00:1.01

sub1/clk_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[0]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[1]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[2]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[3]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[4]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[5]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[6]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_in[7]_UPF_LS LSDNSSX1_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

1.779008

lo, ry, st 0.95->0.95:125.00:1.01

sub1/data_out_reg[0] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[1] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[2] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[3] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[4] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[5] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[6] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/data_out_reg[7] DFFARX1_HVT saed32hvt_ff0p95v125c

7.116032

n 0.95:125.00:1.01

sub1/rst_n_UPF_LS LSDNSSX2_HVT saed32hvt_dlvl_ff0p95v125c_i1p16v

2.033152

lo, ry, st 0.95->0.95:125.00:1.01

--------------------------------------------------------------------------------

Total 37 cells 111.569217对于标准单元,Power Compiler会保证set_voltage命令和set_operating_conditions命令指定的工作温度、工作工艺和各电压域的工作电压与映射的标准单元库中的特征化环境(nom_process、nom_temperature、nom_voltage)一致,下面展示了标准单元库saed32hvt_ff0p95v125c的特征化环境。

// saed32hvt_ff0p95v125c.lib

library ("saed32hvt_ff0p95v125c") {

*****

nom_voltage : 0.950000;

nom_temperature : 125.000000;

nom_process : 1.01;

operating_conditions (ff0p95v125c) {

process : 1.01;

voltage : 0.950000;

temperature : 125.000000;

tree_type : "worst_case_tree";

}

*****如果修改标准单元库saed32hvt_ff0p95v125c的特征化环境(如nom_voltage)使之不匹配,此时综合会出现以下错误。

Error: The target_library does not contain an inverter characterized for operating condition (voltage = 0.950000V, process = 1.010000, temperature = 125.000000). (MV-006)

This problem occurred at:

Error: The target library does not contain an inverter.

An inverter is required for mapping. (OPT-101)对于电压转换器,Power Compiler会保证set_voltage命令和set_operating_conditions命令指定的工作温度、工作工艺和各电压域的工作电压与映射的标准单元库中的部分特征化环境(nom_process、nom_temperature)以及voltage_map和pg_pin定义的电压一致,下面展示了电压转换器库saed32hvt_ulvl_ff1p16v125c_i0p95v的特征化环境以及voltage_map和pg_pin定义的电压。

library ("saed32hvt_ulvl_ff1p16v125c_i0p95v") {

*****

nom_voltage : 1.160000;

nom_temperature : 125.000000;

nom_process : 1.01;

operating_conditions (ulvl_ff1p16v125c_i0p95v) {

process : 1.01;

voltage : 1.160000;

temperature : 125.000000;

tree_type : "worst_case_tree";

}

voltage_map(VDDH,1.160000);

voltage_map(VDDL,0.950000);

voltage_map(VSS,0.000000);

cell (LSUPX1_HVT) {

input_voltage_range (0.7,1.16);

output_voltage_range (0.7,1.16);

cell_footprint : "LSUP";

level_shifter_type : "LH";

is_level_shifter : true;

area : 7.116032 ;

cell_leakage_power : 8.339406e+06;

driver_waveform_rise : "preDrv";

driver_waveform_fall : "preDrv";

pg_pin (VDDH) {

voltage_name : "VDDH";

pg_type : "primary_power";

std_cell_main_rail : true;

}

leakage_power () {

when : "!A";

value : "8.3394061e+06";

}

leakage_power () {

when : "A";

value : "6.5904314e+06";

}

pg_pin (VDDL) {

voltage_name : "VDDL";

pg_type : "primary_power";

}

pg_pin (VSS) {

voltage_name : "VSS";

pg_type : "primary_ground";

}

pin (A) {

input_signal_level : "VDDL";

fanout_load : 0.092000;

related_power_pin : "VDDL";

related_ground_pin : "VSS";

level_shifter_data_pin : true;

direction : "input";

fall_capacitance : 1.363858;

fall_capacitance_range(1.223080,1.459050);

capacitance : 1.359803;

rise_capacitance : 1.355747;

rise_capacitance_range(1.214900,1.425217);

max_transition : 1.024000;

}

*****对于电压转换器而言,无论如何改变nom_voltage,其不会影响映射(确定一个电压转换器库的nom_voltage也是没有意义的,因为一个电压转换器可能有两个电源)。