你应该使用更宽的走线宽度吗?你怎么知道呢?

最近,一位工程师问我关于走线宽度和插入损耗之间的关系,同时调整介电高度以保持 50Ω 的单端阻抗。

在高层次上,这里有五个变量在起作用,包括走线宽度、铜重量、介电高度、Dk 和 Df。包括频率和树脂含量,我们实际上是在谈论七个变量。(然后是带状线与微带线配置,它们稍微改变了情况,以及影响预浸料厚度和铜粗糙度的铜百分比。为了讨论,我们将保持简单,并在以后的专栏中讨论其中的一些因素。

当时钟频率高于大约 1GHz 且互连长度超过 12 英寸时,有损传输线效应会成为重要的信号完整性问题。假设我们谈论的是带状线并从我正在查看的 [Megtron 6 (G)] 的叠层中获取数据,我们将在两种不同的走线宽度/介电高度组合之间使用插入损耗比较。(Dks 相似,但略有不同,具体取决于树脂含量。

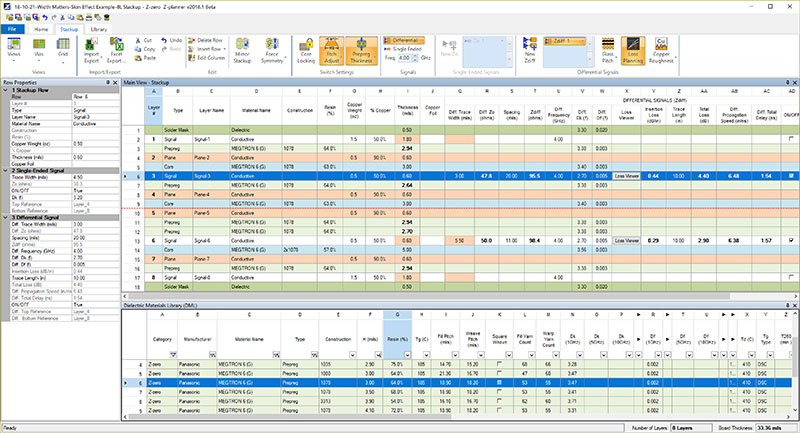

示例设计。从 Megtron 6 (G) 表中,一个 8 层叠层示例提供了一个方便的说明:

- 第 3 层 --- 走线宽度较窄,电介质

较薄 宽度 = 3 mils 3 mils

纤芯(单层 1078 玻璃);半盎司。2.64 mils 的铜

压制预浸料(单层) - 第 6 层 --- 更宽的走线、更厚的

电介质宽度 = 5.5 mils

5 mils 的磁芯(双层 1078 玻璃);半盎司。5.64 mils 铜

压制预浸料(双层 1078 玻璃) - 电介质的电气特性:

磁芯:Dk = 3.64 (RC = 54%);Df = 0.004

预浸料:Dk = 3.4(RC = 63%;1078 玻璃);介电常数 = 0.003

在 4GHz 时,图 1 中的 Y 列显示以 0.44dB/in 计算的插入损耗。对于第 3 层的 3 mil 宽走线和 0.29dB/in。对于第 6 层的 5.5-mil 线路,根据传统观点,较窄的走线宽度会导致信号衰减增加。

图 1. 使用Z-planner软件的8层叠层示例显示,第3层的走线宽度为3 mil,第6层的走线宽度为6 mil,两个单端阻抗均约为50Ω。

**关键损失组件。**除了铜粗糙度考虑(未来专栏的主题)之外,插入损耗有两个主要组成部分:导体损耗和介电损耗。

*导体损耗:*从 DC 到几 MHz 的频率,走线中的电流穿过走线的整个横截面积。然而,在较高频率下,电流沿线路的周边流动,而不是均匀地流过整个横截面。因此,随着互连路径的有效横截面减小,信号和返回路径导体的串联电阻随频率的平方根增加。这种类型的损失通常被称为"皮肤效应"。无论名称如何,在 1GHz 及以上时都需要关注。

*介电损耗:*第二个重要的损耗机制是介电损耗,它只是将电能从交变电场转化为热量。介电损耗通常以每英寸分贝为单位,随频率的增加而增加,并与材料的耗散因数 (Df) 成反比,Df 是材料的树脂类型和分子结构的函数。根据树脂含量,"标准损耗"FR-4 材料的 Dfs 范围为 0.015-0.02。与标准损耗材料相比,较低的 Df 值相当于更多的输出信号到达其目的地,以及更高的材料成本。

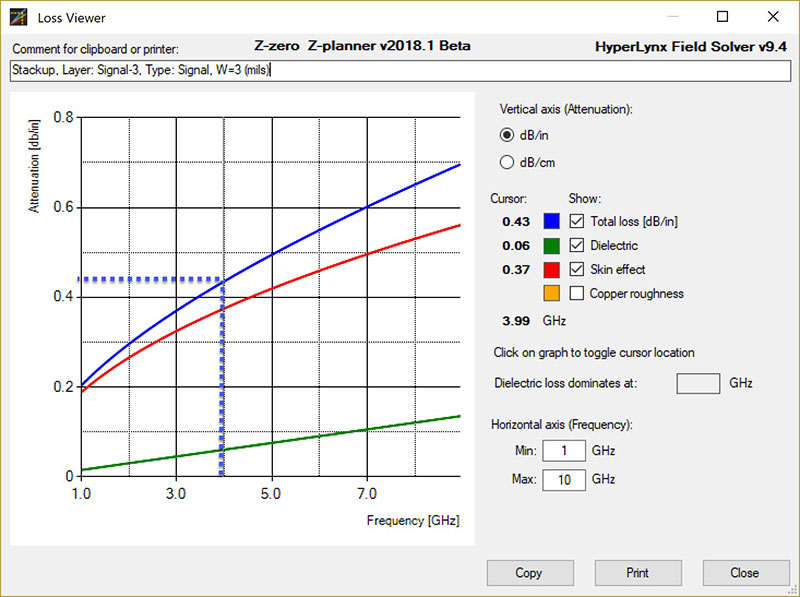

由于我们在示例中的两个信号层上使用了相似的电介质,因此我们不应期望第 3 层的窄迹线和第 6 层上的较宽迹线之间的介电损耗分量有很大差异。我们可以通过使用软件工具来检查导体损耗和介电损耗对这些层的贡献来确认这一点。W = 3 mil 外壳的第 3 层结果如图 2 所示。

图 2. 损耗查看器显示了第 3 层的介电损耗 (0.06 dB/in.) 和导体损耗(集肤效应;0.37 dB/in.) 的贡献明细。

在这里,我们可以看到介电损耗仅贡献 0.06dB/in.,而导体损耗(集肤效应)贡献了整整 0.37dB/in。-- 整整六倍的介电损耗贡献!当然,我们希望将插入损耗数乘以走线长度,以产生总通道损耗。

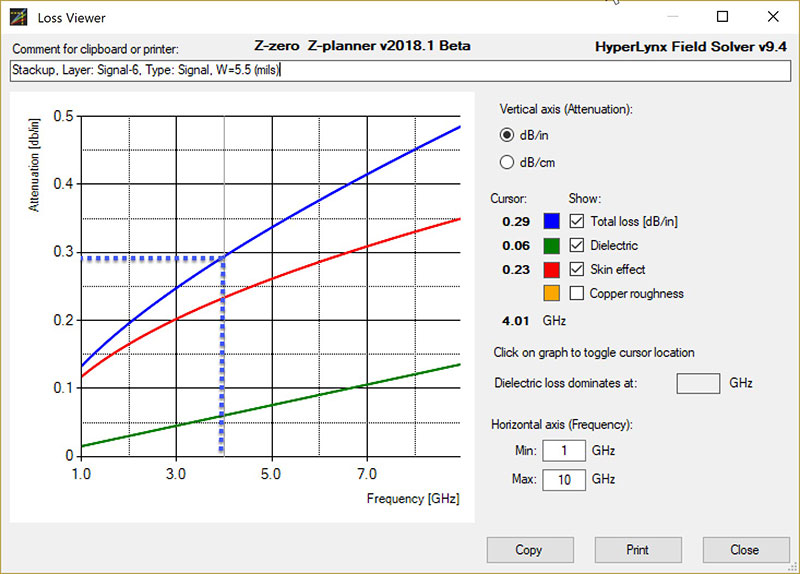

图 3 显示了第 6 层上 5.5 mil 走线的相同曲线。在这里,我们可以看到我们的介电损耗没有改变,而集肤效应却显著下降 -- 仅为 0.23dB/in。当然,较厚的电介质会导致更大的整体电路板厚度,但如果您想从互连预算中消除最后几个分贝,那么在设计过程的早期获得这一见解会很有帮助。

图 3. 损耗查看器显示第 6 层的介电损耗 (0.06 dB/in.) 和导体损耗(集肤效应;0.29 dB/in.) 的相对贡献。

结论

我们可以用这个例子走得更远,看看损耗更高但价格更低的层压板。我们还可以探索铜粗糙度和树脂含量的影响。我们将在以后的专栏中介绍其中一些其他设计因素。

有人说走线宽度在损耗方面并不是什么大问题,但在这里我们了解到更宽的走线宽度可以成为减少插入损耗的一个很好的杠杆。Megtron 6 (G) 是一种相对昂贵的低损耗电介质,在市场上各种层压板中,它低估了介电损耗的可能性范围。对于实际设计,您可能希望在叠层设计工具中进行材料权衡,然后与您的电路板供应商专门讨论权衡。