**少年有维特的烦恼,而SI/PI工程师有串扰的烦恼。**串扰是在做SI相关的工程师经常听到或遇到的问题,但实质上能理解串扰的工程师还是少数。不管是在低速或是高速电路的设计甚至射频电路、天线都会有串扰的问题存在。有人可能会想说天线?! 是的,像阵列天线会特别强调Iolation。简单来说,两条传输线或导体,相邻布线就会有串扰的风险。

引起串扰的原因是什么?

串扰是因为传输线之间,透过电磁场相互耦合而产生出的干扰能量(杂讯)。好像有点抽象,说白了就是互容和互感的效应。如果是EE相关背景应该都不陌生。也就是说两条微带(带状)传输线中间相隔空气(FR4),就会形成寄生电容,互感也是如此。如果不熟悉电容电感可以先看看维基百科电容 电感的解释。传输的能量(讯号)所含的高频成分越多,串扰效应会越明显。

这句话是什么意思?讯号里的高频成分?首先我们要先知道的传输讯号的属性, 简单来说一般我们传输的数位讯号(方波)他是属于宽频的讯号,如果数位波形越理想所涵盖的高频成分就会越多,讯号所需要的Rise time就越快。不懂可以看一下海绵宝宝跟派大星的傅立叶转换的关系(梗图支援一下XD)。海绵宝宝的头越方正,派大星旁边的高频谐波成分就越多(红色圈圈)!

海绵宝宝做傅立叶转换

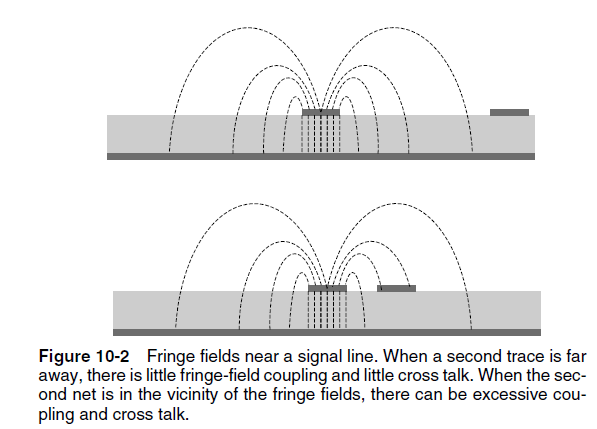

看个图可能比较容易理解,由下图可以看到,由微带传输线所引起的电力线之边缘场会影响到邻近的传输线导体。也可以解释成磁流透过寄生电容流入另一条导线。 (I=CdV/dt)

reference from [1]

近端串扰与远端串扰

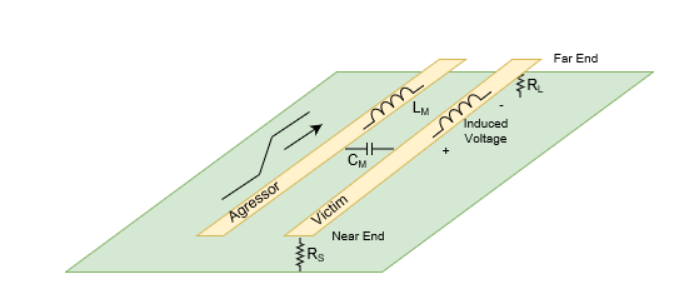

在实务上工程师将串扰分成近端与远端两种干扰模式,通常为了快速理解将导线分成有源(攻击线, agressor)与无源(静态线, Victim)两种状态。在静态线上靠近源端的量测点可被定义成近端,反之靠近终端者为远端。如图所示:

Crosstalk from Mutual Inductance [2]

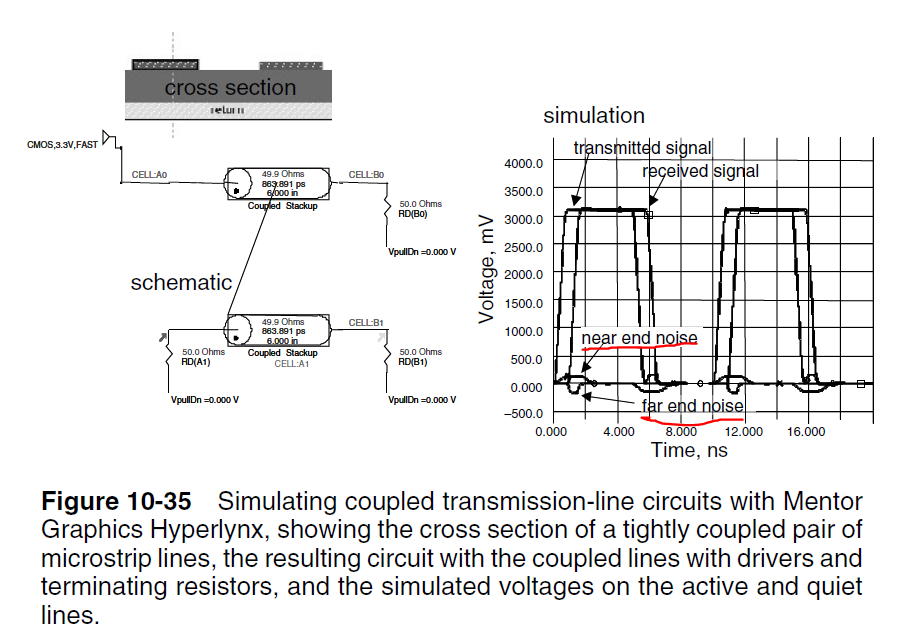

当Agressor传输一个步阶方波,前面提到由于寄生电容在电压变化时,会产生磁流流进Victim,一部分往近端方向前进,另一部分往远端。同时两导线也有互感效应,但不同的是根据楞次定律,当一导体感受到瞬间电压变化会产生反向电压抗拒,故在远端处除了电容耦合电压外,也会有一反向的感应电压产生负向的电流。近端的干扰时间为导体时延(长度)的两倍(去回),远端则是持续Rise time的时间,Waveform如下图:

1

也就是串扰会发生在电压变化的情况,所以呼应前段所说,高频成分越多,rise time越快,发生串扰的风险越高。另位从数学式也可以看出近端是电容与电感耦合效应相加,远端是相减。远端上电感感应的能量(能量累加)会大于电容互耦的能量,所以在Waveform上会是呈现负值的电压。详细可以参考网际星空Crosstalk的解释。有趣的是远端串扰跟传输线长度与Rise time大小有关,从前面的解释应该可以略知一二。

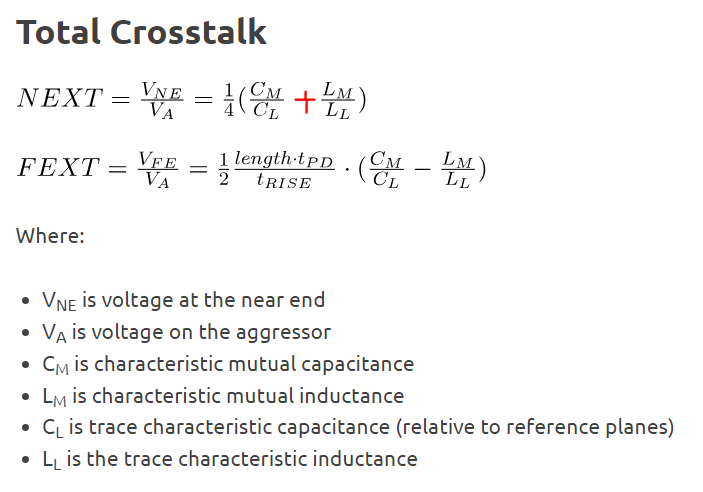

Xtalk数学式

减小串扰的方法

电路布线常会有串扰的风险,最后简单说明几个减小串扰的方法,常见增大走线间距、使两导体的有串扰风险的区域最小化、相邻层走线时传输线互相彼此垂直、降低板材介电常数(确保阻抗控制)、内层布线(减小远端串扰)...等。至于内层布线可以消除远端串扰的原因在于,内层布线导体接触的介电质相同,电感与电容互耦的能量可以相消。故内层布线的远端串扰通常可以小于-50 dB。其实减小串扰的重点就是减小两导体间的互耦效应。 [3]

一些有用的方法

看到这里你或许会想,不是阿!哪有每个电路的空间都么大,让我可以两条讯号线间距很远。确实,有些结构是很难避免的,所以需要思考哪些结构是主要的发生点,以及哪一部分可以避免。

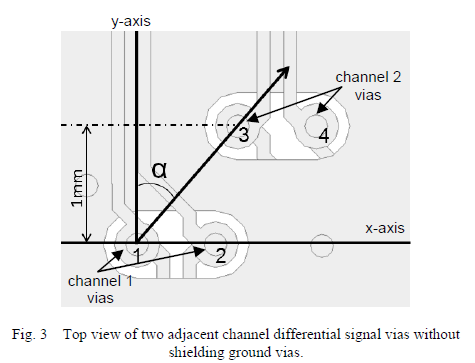

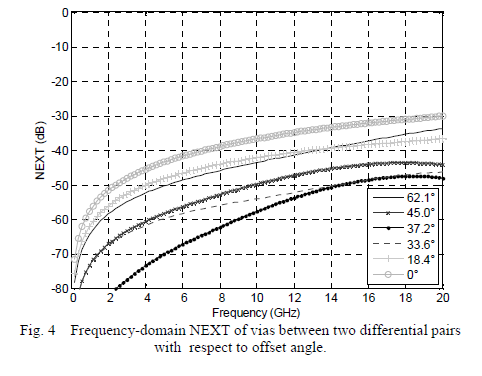

像是可以利用Via 错位的方式减少串扰的影响(先忽略P/N没有对称的情况XD),如下图:

相邻Via错位布线[4]

近场的影响[4]

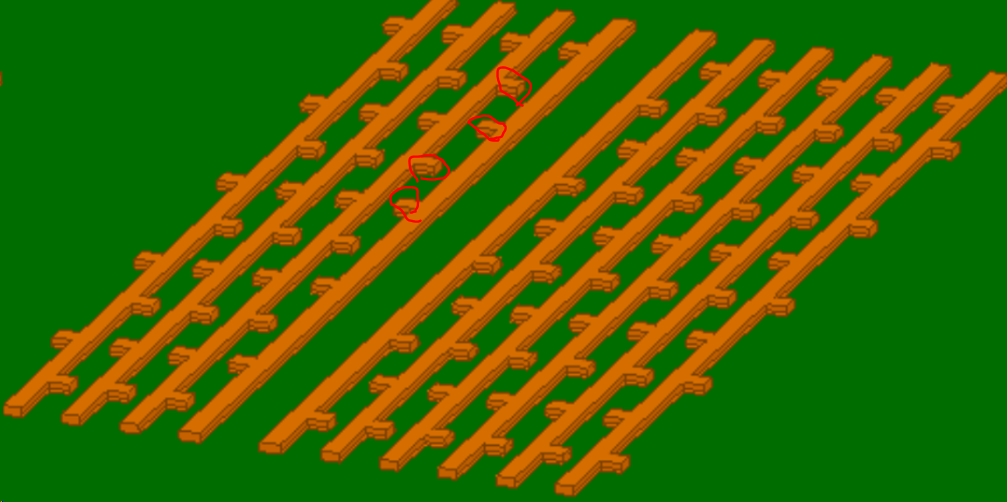

酷炫一点的像是2015年Intel发表的文章,利用再传输线上增加Stub(tabbed line)的结构,增加互容的能量,减少远端的串扰。 [5]

利用Stub结构减小远端串扰[5]

结语

后来想想人的行为跟串扰很像,靠得太近容易吵架(loss)。有适当的距离反而产生美感。或许会想,那活人(agressor)对死人(Victim)呢? 活人可能还是会有点Loss(怕爆)吧XD

参考文献:

1\] Eric Bogatin, Cross Talk in Transmission Lines, SIGNAL AND POWER INTEGRITY-- SIMPLIFIED \[2\] [Practical EE , Crosstalk](https://practicalee.com/crosstalk/ "Practical EE , Crosstalk") \[3\][高速先生,串扰探秘-近端串扰与远端串扰](https://www.eet-china.com/mp/a53783.html "高速先生,串扰探秘-近端串扰与远端串扰") \[4\] Kunia Aihara, Minimizing Differential Crosstalk of Vias for High-speed Data Transmission, IEEE, 2014 \[5\] [Kunze, Richard K., Yunhui Chu, Z. Yu, San K. Chhay, Mauro Lai, and Yanjie Zhu. "Crosstalk mitigation and impedance management using tabbed lines." Intel white paper (2015).](https://docplayer.net/62847888-Crosstalk-mitigation-and-impedance-management-using-tabbed-lines.html "Kunze, Richard K., Yunhui Chu, Z. Yu, San K. Chhay, Mauro Lai, and Yanjie Zhu. “Crosstalk mitigation and impedance management using tabbed lines.” Intel white paper (2015).")