1. 概述

本文介绍一种基于FPGA实现信号发生器的方法,并说明DDS实现频率控制的原理,给出正弦波、三角波、矩形波和锯齿波的仿真结果。

2. DDS实现原理

DDS(直接数字频率合成)是一种通过数字技术直接生成所需频率模拟信号的电子方法,其核心原理是利用数字方式精确控制相位累加和波形查表,再通过数模转换(DAC)和滤波来产生高分辨率和高稳定性的模拟信号。其中相位累加器是一个N位宽的二进制加法器,在每个参考时钟周期上,将存储在频率调谐字寄存器中的值M累加到当前相位值上,累加器的输出是一个离散的相位值,范围是0到2^N-1,对应相位0~2π。M越大,每个时钟周期增加的相位越多,相位累加器溢出的速度越快,意味着生成的输出信号频率越高。波形查表中存储了所需输出波形在一个完整周期内各个离散相位点对应的幅度量化值。

输出频率计算公式:

f_out = (M × f_clk) / (2^N)

其中:

-

M 为频率调谐字

-

f_clk 为参考时钟频率

-

N 为相位累加器位数

频率分辨率为:

f_clk / 2^N

根据奈奎斯特采样定理,无混叠的理论最大输出频率为 f_clk/2。

3. 源码实现原理及仿真结果

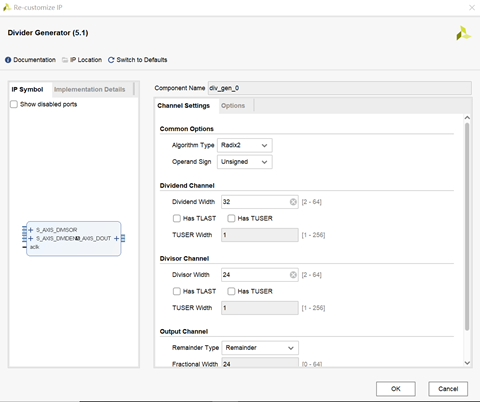

本文所提供的源码实际上是借鉴DDS的基本原理,相位累加器的位宽为8,即一个完整周期内波形查找表中应储存256个离散相位点。实现原理是先计算波形原始周期(这里为参考时钟周期)是生成波形周期的多少倍,多少倍数就多少分频,然后利用分频器原理得到实际生成波形的时钟信号,该时钟信号的周期就是想要的生成信号的周期,利用该时钟信号去查找存储的波形数据即可。这里用到官方的除法器IP核,用于节省时序资源。

Divider IP核介绍

在FPGA中直接使用除法运算符(/)通常会导致综合工具推断出非常庞大、低效的逻辑结构,消耗大量的查找表(LUT)和触发器(FF),并且时序性能可能很差。Divider Generator IP核解决了这个问题,其支持的运算类型有:

-

整数除法

-

定点小数除法

-

分数模式

-

余数输出和模运算

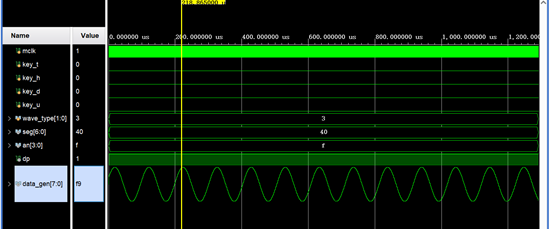

仿真结果

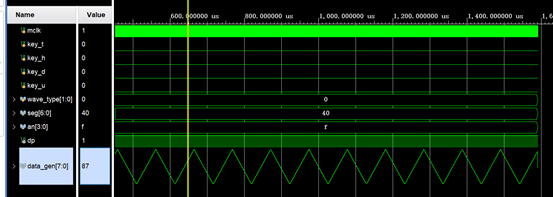

三角波:

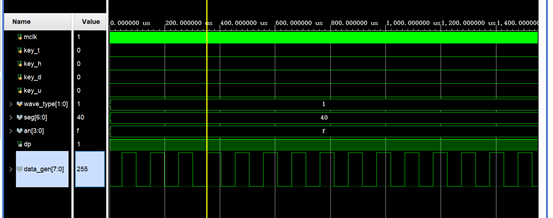

方波:

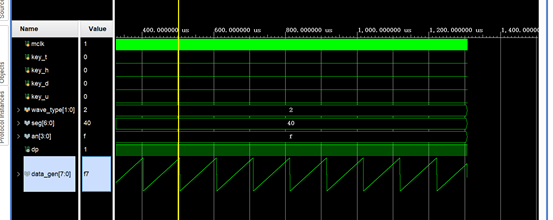

锯齿波:

正弦波:

本期分享结束,感谢大家看完,私信我可获取相关源码工程