FPGA模块越写越多,规范性和可移植性却堪忧。要是有一个工具可以根据模块接口描述文件生成verilog和c头文件就好了。苦苦搜寻找到了几款免费的工具,SystemRDL、cheby和rggen。笔者学习了下cheby和reksio,reksio是gui版的cheby,这是是欧洲核子研究中心 (CERN)的控制电子和机电一体化 (CEM) 部门开源的接口生成工具,使用体验非常棒,直接看效果。

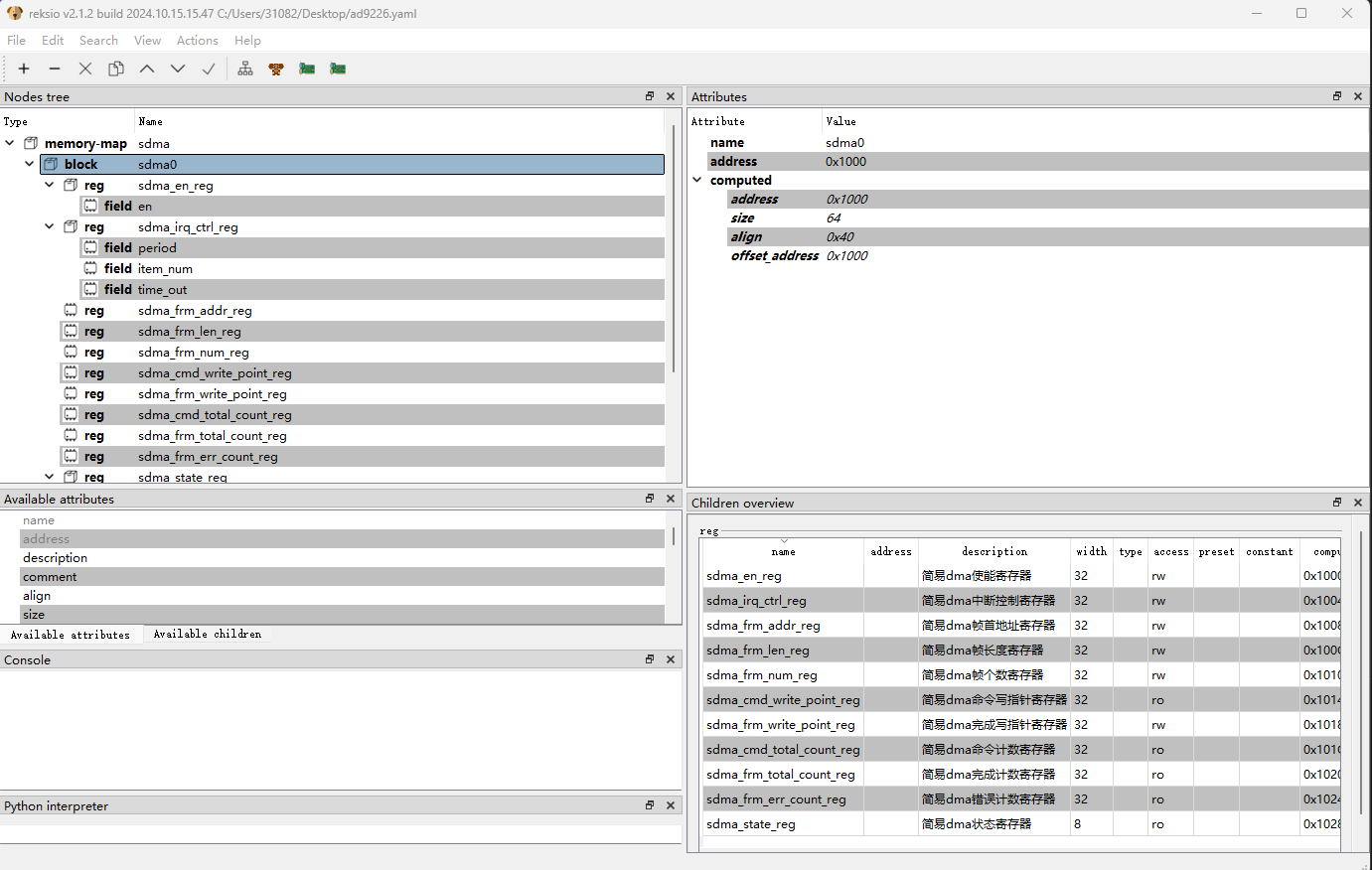

1、使用reksio图形软件描述寄存器属性

-

Noders tree面板中是寄存器的树形结构描述,可以灵活添加各种对象,如block、reg

-

Attributes面板是每个对象具有的属性,可以在此界面修改属性

-

右下角的Children overview中是子对象的的整体预览

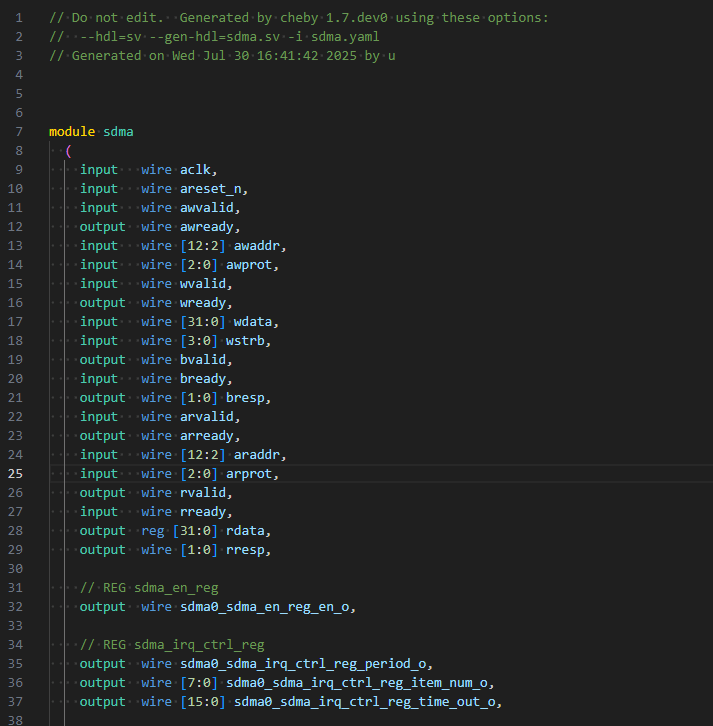

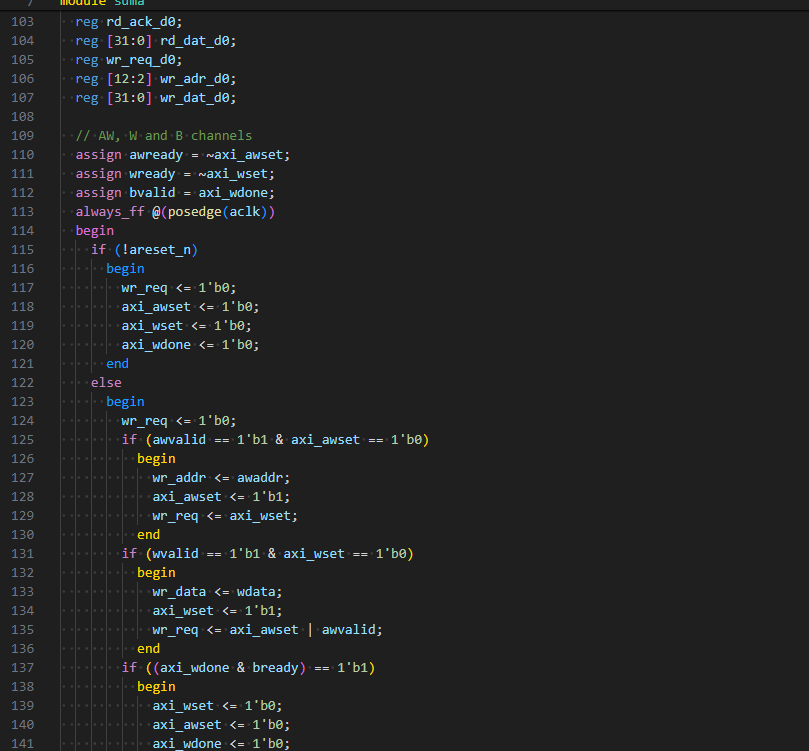

2、生成sv格式接口包装

使用cheby命令自动生成sv代码,sdma.sv中将axi总线命令转换成了寄存器的读写

bash

cheby --hdl=sv --gen-hdl=sdma.sv -i sdma.yaml

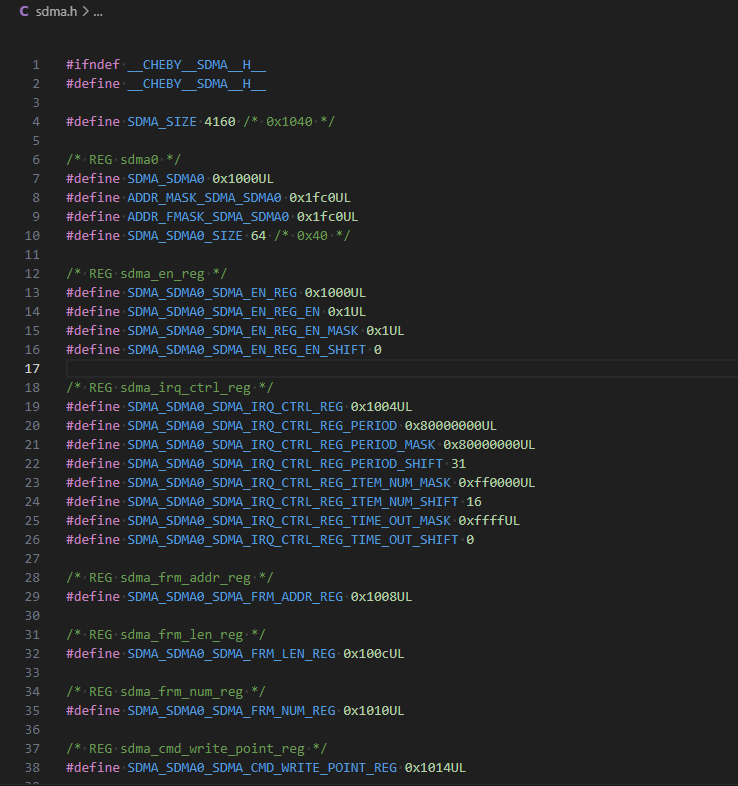

3、生成c头文件

使用cheby命令自动生成c头文件代码

bash

cheby --gen-c=sdma.h -i sdma.yaml

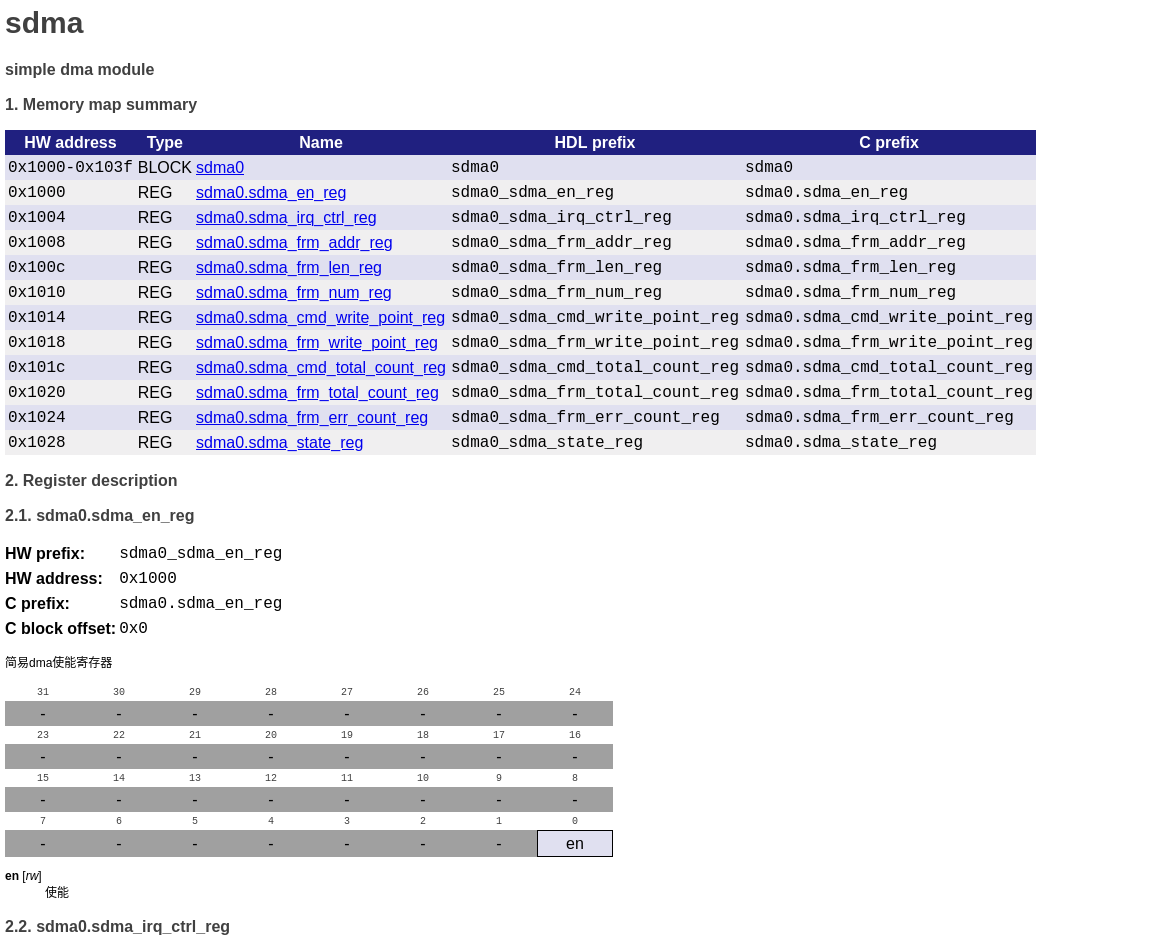

4、生成模块接口文档

这个功能就niub了,能直接生成接口文档,再也不用担心接口文档写错了。

cheby --gen-doc=sdma.html -i sdma.yaml

最后,附上以上工具源码位置

https://gitlab.cern.ch/be-cem-edl/common/cheby

https://gitlab.cern.ch/Cheburashka/reksio