1、基本概念

- 建立时间(setup time): 在时钟采样沿之前,数据必须提前到达的最短时间。

- 保持时间(hold time) : 在时钟采样沿之后,数据必须保持稳定不变的最短时间。

可以总结为:时钟到来之前,数据需要提前准备好;时钟到来之后,数据还要稳定一段时间。

那么EDA工具是如何知道标准单元中每个 flip-flop 的建立保持时间要求呢?

答案是通过工艺库中包含的timing library库(比如后端工具innovus设计导入阶段加入的 .lib文件)

2、寄存器内部结构及工作原理

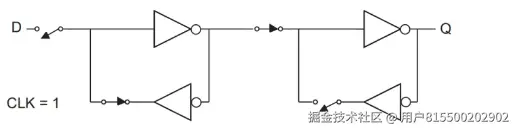

为什么会有建立时间和保持时间的要求?要想了解这个问题我们要先了解D触发器内部的数字电路结构,如下:

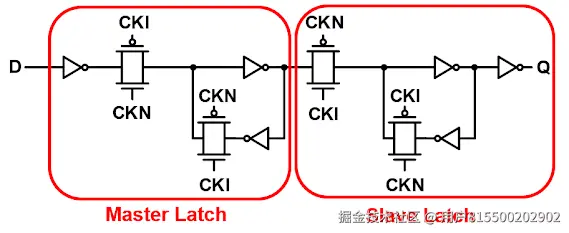

触发器电路包含一个主锁存器和一个从锁存器。每个锁存器由两个传输门(Transmission gates, TG)和三个反相器构成。其中,CKN为CLK信号本身,CKI为CLK的反相。

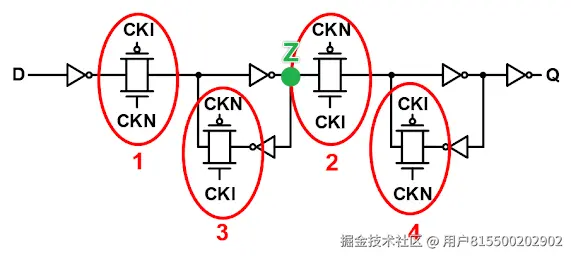

为了方便介绍,我们将传输门标号如下:

-

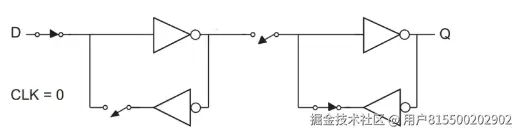

当CLK=0时

- TG1和TG4导通,TG2和TG3关断(电路图简化为下图):主锁存器为传输状态,新数据从D → Z;而从锁存器为锁存状态,Q不变

- TG1和TG4导通,TG2和TG3关断(电路图简化为下图):主锁存器为传输状态,新数据从D → Z;而从锁存器为锁存状态,Q不变

-

当CLK=1时

- TG1和TG4关断,TG2和TG3导通(电路图简化为下图)。从锁存器为传输状态,数据从Z → Q; 而主锁存器为锁存状态,Z不变。(此时外部D为隔离状态)

- 总结起来就是,在CLK的低电平阶段,新数据将在主锁存器中建立。一旦CLK变为高电平,数据将通过从锁存器传递到 output。

3、为什么需要建立/保持时间?

建立时间

从上面的分析,可以知道的是:新数据(来自 D)必须在CLK=1之前到达Z,以便数据可以正确地锁存到主锁存器中。而到达内部节点Z需要时间(经过TG1和两个反相器,他们都有delay)。如果这个时间不足,在CLK上升沿到来之后,Z点可能处于不稳定的状态(既非0也非1),从而导致亚稳态。

保持时间

然而,物理世界不存在理想的器件,TG1在CLK=1后不会立即关断(需要时间)。因此在CLK=1之后,传输门完全关闭之前,不得更改数据,否则数据可能"溜进"主锁存器,与原有数据Z发生冲突,导致亚稳态

代码与文字齐飞,逻辑共创意一色 !若我的文章让你会心一笑,点个赞我们一起笑谈"IC人生"!