一、pcie实现虚拟串口概述

1.可以使用xdma和pcie接口来实现虚拟串口

2.虚拟串口设计的设计内容包括逻辑设计和驱动设计两部分内容

3.用于工业相机,工业控制,pci卡或者pcie卡

4.底层本质上还是pcie,pcie驱动相机的串口,pcie作为桥,上位机把

pcie当作串口来使用

二、设计

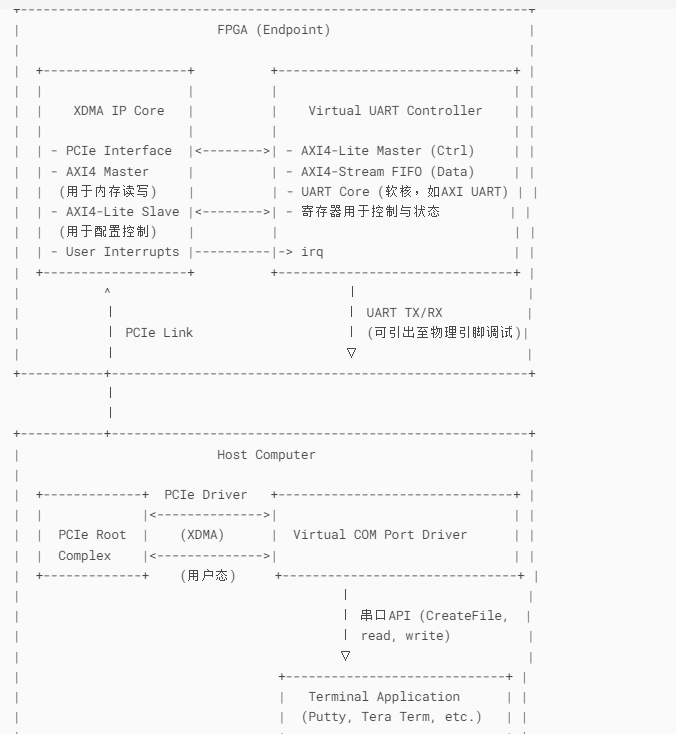

1.使用xilinx的xdma ip核,然后通过pcie总线来实现一个虚拟的串口

2.FPGA逻辑部分,通过axilite接口设计一个axilite_uart来驱动工业相机

3.windows驱动从pcie抽象出来一个串口,这个串口设计可以在windows驱动上做,

也可以直接在qt应用层来做,如果自己用就在qt上开发即可,功能是可以实现的,

但是通用性就没有那么好,如果想通用,那么就在windows驱动去设计,可以看

一些图像采集卡的厂家,都是在windows驱动中去做的,然后在windows的注册表中

注册串口号

4.主机操作系统呈现为一个标准的串口(COM口或tty设备)。主机上的应用程序可以像使用普通串口一样与之通信,而实际的数据传输是通过高速的PCIe总线完成的。

5.可以在设备管理器中发现一个你新开发的串口端口号

三、虚拟串口设计框架图

四、虚拟串口控制器核心设计

1.使用axilite接口,用于接收pc的控制命令,比如波特率的设置,

数据位的设备,停止位,奇偶校验等

定义一组寄存器:

CTRL_REG: 使能发送、使能接收、中断使能、复位等控制位。

STATUS_REG: 发送忙、接收就绪、溢出错误等状态位。

BAUD_DIV_REG: 波特率分频值(根据FPGA时钟计算)。

FIFO_TX_DATA: 主机写入要发送的数据。

FIFO_RX_DATA: 主机读取接收到的数据。

IRQ_EN_REG: 控制哪些事件可以产生中断(如RX有数据、TX空闲)。

2.uart core

可以使用Xilinx的AXI UART Lite或AXI UART 16550 IP核,也可以自己用VHDL/Verilog编写一个简单的UART收发器。

3.中断逻辑:

当RX FIFO非空(有数据可读)或TX FIFO为空(可以接收新数据)时,根据中断使能寄存器的设置,产生一个脉冲信号连接到XDMA的usr_irq_req端口。

这将触发一个MSI/MSI-X中断到主机,通知驱动进行处理。

五、驱动和应用程序设计

在主机端,我们需要让操作系统将这个特定的PCIe设备识别为一个串口。

方案一:定制内核驱动(Linux/Windows)

这是最正统但也是最复杂的方法。

Linux驱动:

你需要编写一个字符设备驱动或TTY层驱动。

驱动需要:

探测到你的特定PCIe设备(通过Vendor ID和Device ID)。

映射PCIe BAR空间,从而能够读写FPGA端的寄存器。

处理来自XDMA的中断(MSI/MSI-X)。

实现tty_driver、tty_operations等结构体定义的函数,如open, close, write, set_termios等。

在write函数中,将用户要发送的数据通过XDMA的H2C Stream通道或MMIO(Memory-Mapped I/O)写入FPGA。

在中断处理例程中,从C2H Stream通道或MMIO读取FPGA收到的数据,并通过tty_flip_buffer_push提交给TTY层,最终被用户空间的read调用获取。

创建一个/dev/ttyXXX设备节点。

Windows驱动:

同样需要编写一个KMDF或WDM驱动程序。

更为复杂,需要遵循Windows的串口驱动框架(SerCx或SerCx2)。

你需要实现一系列EvtDriverDeviceAdd、EvtIoRead、EvtIoWrite、EvtInterruptIsr等回调函数。

驱动程序需要进行签名才能在64位系统上加载,这增加了开发难度和成本。

2.桥接程序(用户态):

你只需要编写一个运行在用户空间的应用程序。

这个程序的工作是:

打开/dev/xdmaX_h2c_0和/dev/xdmaX_c2h_0等设备文件。

使用select或epoll监听中断事件文件(/dev/xdmaX_events_0),或者使用轮询方式。

当检测到"有数据可读"的中断时,从c2h设备文件读取数据(FPGA发来的数据)。

将读取到的数据写入一个真实的虚拟串口(如使用sudo socat -d -d PTY,raw,echo=0 PTY,raw,echo=0创建的一对伪终端/dev/pts/X之一)。

同时,监听另一个伪终端,如果有数据到来(来自主机上的终端程序,如Putty),则将其写入h2c设备文件(发送给FPGA)。

优点: 完全在用户空间开发,无需深入内核驱动开发,调试方便。可以利用libudev等库实现设备的热插拔管理。

缺点: 性能稍低于内核驱动,且需要运行一个后台守护进程。

六、驱动设计的两种方案对比