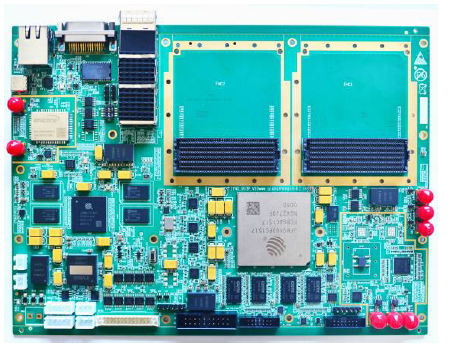

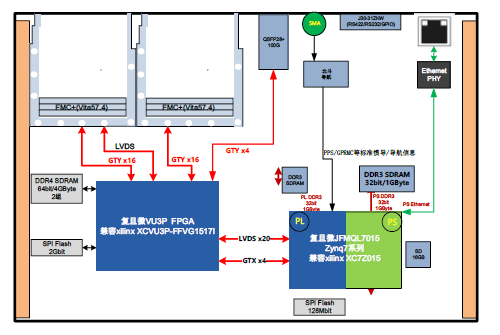

FT-ZYNQ-VU3P 是一款基于复旦微 ZYNQ+VU3P 总线架构的全国产化高速信号处理平台,搭载 2 个 FMC+接口,可支持任意 FMC功能接口的扩展(包含各类国产非国产的 AD 卡/DA 卡/以及其他各类标准子卡)。

技术指标

复旦微VU3P FPGA:

FPGA:JFM9VU3P,兼容进口XCVU3P-2FFVG1517I;

接出 2 个FMC+接口(每个FMC 上16x GTY、LA 全管脚);

2 组4GByte 64bit DDR4 SDRAM;

一组国产PLL 时钟控制器,用于给全板每个GTY 提供时钟;支

持给FMC 直供采样时钟;

1 组GTY 4x 和20 对LVDS 用于两个FPGA 之间互联;

对外 1 个QSFP28+光纤接口;

复旦微ARM FPGA 处理器:JFMQL7015

PS 上1 组1GByte 32bit DDR3 SDRAM;

PS 上一个RJ45 以太网;

PL 上1 组1GByte 32bit DDR3 SDRAM;

北斗导航芯片

双天线输入;

UART 协议信息输出;

支持 PPS 输出;

支持PPS 输入;

物理与电气特征

板卡尺寸:160 x 223mm

板卡供电:5A max@+12V(±5%)

散热方式:风冷散热

环境特征

工作温度:-40°~﹢65°C,存储温度:-55°~﹢125°C;

工作湿度:5%~95%,非凝结

软件支持

各接口测试工程:

应用范围

软件无线电;

雷达与基带信号处理;