一、嵌入式

1、核心定义:

以应用为中心,以计算机技术为基础,软硬件可裁剪的专用计算机系统。

能够根据用户需求(功耗、体积、可靠性)进行灵活裁剪。

二、计算机系统

1、软件的基本组成

系统软件、应用软件

2、硬件基本组成

运算器、控制器、存储器、输入设备、输出设备

3、软件与硬件的层级架构及协作关系

(1)kernal

-

内核,操作系统最核心的部分

- 关键工作

- 硬件资源的管理:CPU调度、内存管理、设备驱动接口

- 系统服务的提供:提供最基础的系统调用接口,让上层的应用软件能调用硬件资源

- 关键工作

(2)内核与CPU之间的关系

- CPU是硬件,负责指令执行和运算;内核是软件,负责资源管理和调度

-

CPU是执行指令的物理硬件,内核是操作系统核心代码;

-

CPU直接运行内核指令,而内核通过任务调度决定CPU执行哪些任务(包括自身和用户程序),并处理中断事件

-

粗暴理解 > 内核是集结一系列的代码和指令,CPU是接收中断信息去执行依据指令代码

-

粗暴理解> 同样CPU 是内核运行的硬件载体,内核负责管理 CPU 计算能力分配

-

(3)处理器

-

CPU(Center Processing Unit):中央处理器 是一种通用的强大的处理器 脑力劳动CEO

GPU(Graphics Processing Unite):图形处理器 体力劳动者

FPU:浮点型运算单元

-

在嵌入式行业:

MPU(Micro Processing Unit):微处理器 偏向处理 强调通用

MCU(Micro Contral Unit):微控制器 偏向控制 强调高集成度

-

单片机:单片微型计算机

DSP(digital signal Processing):数字信号处理器 为了进行高强度数学运算的专用芯片

SOC(System on chip):片上系统,SOC是一个设计和集成的概念,更像是一个城市的蓝图,把市政府(MPU)、警察局(MCU)、(工厂)GPU、研究所(DSP)modam(机场),规划在一起,形成一个功能完善的城市

(4)RAM(Random Access Memory)

高速易失,临时存储

- 定义:随机存取存储器,可直接被处理器寻址访问

- 特点:

- 高速读写:速度比ROM更快

- 易失性:断电后数据丢失(Volatile Memory)

- 成本较高:价格昂贵,常用于临时数据存储(如运行中的程序)

- 用途:内存(DRAM)、缓存(SRAM)

(5)ROM(Read-Only Memory)

低速非易失(部分),长期存储

- 定义:只读存储器,通常不能直接被处理器寻址(需通过块设备访问)。

- 特点:

- 低速访问:速度较RAM慢

- 非易失性:传统ROM断电后数据丢失(但现代如Flash ROM可保留数据)

- 成本较高:价格便宜,常用于固件存储(如BIOS)

- 用途:固件、嵌入式系统存储等

(6)SOC(System on Chip,片上系统)

- 定义:SOC是一个高度集成的芯片设计概念,将多个功能模块集成在单一芯片上,类似于一个"城市"的规划。

- 组成部分:

- MPU(Micro Processing Unit):负责通用处理,类比为"市政府"

- MCU(Micro Control Unit):负责控制任务,类比为"警察局"

- GPU(Graphics Processing Unit):负责图形处理,类比为"工厂"

- DSP(Digital Signal Processor):负责数字信号处理,类比为"研究所"

- Modem(通信模块):负责数据通信,类比为"机场"

(7)CPU架构分类

- X86:主要用于PC和服务器(如Intel、AMD处理器)

- ARM:广泛用于移动设备、嵌入式系统(如智能手机、物联网设备)

- MIPS:曾用于网络设备、嵌入式系统,现逐渐被RISC-V取代

- RISC-V:开源指令集架构,近年发展迅速,适用于多种场景

(8)外设模块(Peripherals)

- GPIO(General Purpose Input/Output)

- 通用输入输出接口,用于连接外部设备

- Timer(定时器)

- 提供精确的时间控制,用于任务调度、PWM生成等

- UART(Universal Asynchronous Receiver/Transmitter)

- 串行通信接口,用于设备间数据传输。

- PWM(Pulse Width Modulation)

- 脉冲宽度调制,用于电机控制、LED调光等

(9)ARM内核架构版本

- Cortex-A系列(Application Processors)

- 高性能,用于MPU(如智能手机、平板电脑)

- Cortex-R系列(Real-time Processors)

- 实时性强,用于工业控制、汽车电子

- Cortex-M系列(Microcontrollers)

- 低功耗,用于MCU(如智能家居、传感器)

(10)指令集(Instruction Set Architecture, ISA)

- CISC(Complex Instruction Set Computer)

- 复杂指令集,单条指令可执行复杂操作(如X86)

- RISC(Reduced Instruction Set Computer)

- 精简指令集,指令简单高效(如ARM、RISC-V)

4、软件与硬件关系总结

二者并非孤立存在,通过"分层协作"与"指令交互"实现计算机的完整功能:

硬件是基础,软件是延伸

二者相互依赖,协同进化

分层隔离,降低复杂度

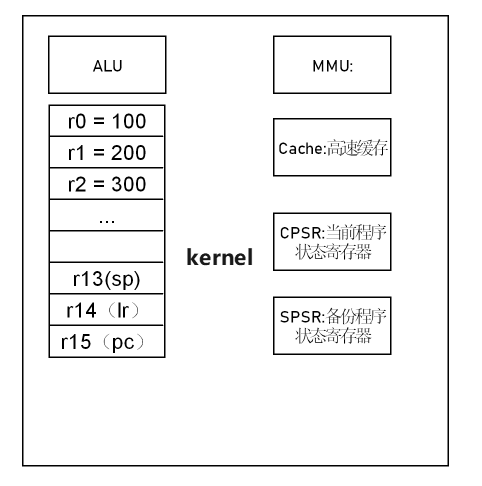

二、CPU核心组件

1、ALU 算术逻辑单元

功能:执行加减乘除、位运算(AND/OR/XOR)等操作

延伸:现代CPU采用多ALU设计,支持SIMD指令(如Intel AVX)加速并行计算

2、寄存器组

通用寄存器**(r0-r12)**:存储临时数据,ARM架构中r13-r15为特殊寄存器(不能通过地址访问)

特殊寄存器:

r13(sp):堆栈指针,管理函数调用时的局部变量

r14(lr):保存函数返回地址,实现子程序跳转

r15(pc):程序计数器,指向下一条指令地址

延伸:x86架构中对应寄存器为EAX/EBX/ESP/EIP等

3、MMU 内存管理单元

功能:通过页表(Page Table)实现虚拟地址→物理地址转换,支持内存保护

延伸:Linux系统采用多级页表(如4级页表),减少内存占用

4、Cache 高速缓存

分级设计:

L1 Cache:分指令缓存(I-Cache)与数据缓存(D-Cache),延迟1-3周期

L2/L3 Cache:容量更大,共享核心间数据

5、CPSR/SPSR 状态寄存器

CPSR:存储当前模式(用户/内核)、中断状态、条件标志(Z/N/C/V)

SPSR:异常发生时保存CPSR,用于恢复现场

6、总线系统与外设

(1)总线类型:

单总线:简单但带宽受限,适合低功耗MCU(如STM32)。

多总线分层:

AHB:高速设备(如DMA、GPU),支持流水线操作。

APB:低速外设(如UART、GPIO),降低功耗。

(2)外设接口:

GPIO:通过方向寄存器控制引脚输入/输出。

Timer:配置预分频器(Prescaler)和重载值(Auto-reload)生成精确延时。

UART:波特率寄存器(Baud Rate Divisor)决定通信速率

三、RAM相关概念辨析

1、冯.诺伊曼架构和哈佛架构区别

| 对比维度 | 冯・诺伊曼架构 | 哈佛架构 |

|---|---|---|

| 存储方式 | 指令与数据共用1 块主存储器 | 指令与数据分别存储在2 块独立存储器(指令存 + 数据存) |

| 总线结构 | 指令总线与数据总线共用 1 条(单总线) | 指令总线与数据总线独立 2 条(双总线) |

| 访问效率 | 分时访问:同一时间只能取指令或取数据,存在 "总线瓶颈" | 并行访问:可同时取指令和取数据,无总线瓶颈,效率更高 |

| 硬件复杂度 | 低:仅需 1 套存储器和总线,成本低、设计简单 | 高:需 2 套存储器和总线,硬件成本高、设计复杂 |

| 程序灵活性(通用性) | 高:支持指令和数据动态修改(如程序运行中修改数据或指令),适合通用计算 | 低:指令存储器通常为 ROM(只读),程序固化后难修改,更适合专用场景 |

- 冯.诺伊曼架构:最早诞生,没有设置指令和数据的分离

- 哈佛架构:设置指令和数据的分离

- 现在的计算机大多是混合架构,不过ARM是哈佛架构

2、SP(Stack Pointer)栈指针寄存器

作用:指向当前栈内存的顶部地址(栈是一种后进先出的数据结构)

功能:

函数调用时保存局部变量、返回地址等

通过PUSH/POP指令动态调整栈空间

场景:函数调用、中断处理中频繁使用(如ARM的R13通常作为SP)

3、 LR(Link Register)链接寄存器

作用:存储函数调用后的返回地址(子程序执行完跳回原位置)

功能:

调用BL(Branch with Link)指令时,自动将返回地址存入LR

若嵌套调用,需手动保存LR到栈中(防止覆盖)

场景:ARM架构中R14通常作为LR

4、PC(Program Counter)程序计数器

作用:存储下一条待执行指令的内存地址(控制程序流程)

功能:

顺序执行时自动递增(根据指令长度)

跳转/分支指令(如B、BL)直接修改PC值

场景:所有指令执行均依赖PC(ARM中R15为PC)