最近在做一个同时需要MCU与FPGA的项目,具体说是FPGA作为MCU的FSMC(Flexible Static Memory Controller)接口的一个外设,通过SRAM接口与MCU通信。MCU用的是STM32中有FSMC接口的100pins器件STM32F103VET6,FPGA用的是国产安路小精灵系列的EF2L15。使用时发现当两种用同一路电源时,上电后MCU无法正常启动工作。现将我对问题的分析以及解决办法分享如下,以下原创内容欢迎网友转载,但请注明出处:https://www.cnblogs.com/helesheng

1、寻找和分析原因

观察到一个现象:上电后FPGA开始稳定工作后,虽然MCU不能工作,但按下MCU的复位键后,MCU能够恢复工作。因此我推测是MCU在和FPGA连接后无法正常复位造成的。但FPGA的启动过程要经过比特流文件从Flash加载到查找表中的过程;而STM32的程序却是从Flash中一边不断取指,一边执行的。启动速度是STM32完胜,怎么会出现STM32反而被FPGA影响的情况呢?显然问题只能发生在FPGA比特流尚未加载完成,MCU发生复位的阶段。

两者相连的FSMC接口,大部分管脚是MCU作为主设备输出信号,FPGA作为从设备输入信号。但当我用示波器观察时却发现,在安路小精灵系列EF2L15进行比特流加载阶段,这些管脚居然在输出高电平!我将这些IO约束为禁止PULLUP的NONE模式,但发现没有什么卵用:比特流配置过程中它们仍然我行我素的输出高电平------想来也是,还没有完成比特流配置,FPGA怎么知道这些管脚的模式是什么。

既然无法在上电的最初阶段保证MCU的正确上电复位,我只能退而求其次:在FPGA完成比特流配置后,再对MCU进行复位。用示波器观察EF2L15的配置完成管脚DONE,我沮丧的发现:这么一个"小精灵",它的配置时间居然达到了400ms以上,这是常见上电复位芯片无法达到的。(如:我自己比较喜欢的MAX809/810的复位时间都只有200ms左右)。

我又想,干脆让EF2L15加载完成后,再用FPGA管脚输出一个的复位信号给MCU好了(具体代码见下一小节)。令人意想不到的事情再次发生:采用这种方法后,JLINK无法下载和调试MCU了。仔细一考虑,这也有道理:上电过程完成后,FPGA的输出的复位信号钳置了MCU的复位管脚,让JLINK在调试时下载MCU程序后无法复位MCU,从而导致无法调试MCU了。

绕了个大弯子,似乎又回到了原点。在上面的尝试后,我得到了以下两种有效的解决方案:

2、两种解决办法

方法一:缩短FPGA上电后比特流加载时间 + 延长MCU复位时间

既然无法保证将MCU复位时间延迟到400ms以上,把FPGA上电后比特流加载时间缩短也是一个不错的办法,在安路的官网上找到了这篇技术文档《TR404_ELF2 FLASH启动加载时间测试》,它提到有两种方法加快"小精灵"系列上电后比特流加载时间:a、提高读取比特流文件读取时钟;2、采用2位或4位比特流( mspix2或x4)加载代替1位比特流加载。

配置方法如下:

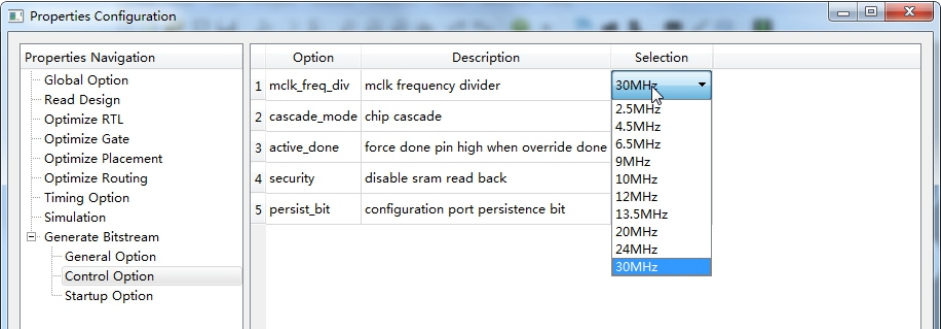

在TD中打开FPGA工程,Process菜单中的属性对话框中进行Properties Configuration,对mclk_freq_div进行配置,将其时钟频率配置到2.5MHz~24MHz之间的更高数值。

图1 Properties Configuration界面配置读取时钟频率

在 TD 软件 Download 界面上,在识别到 EF2 系列芯片以后点击左边的"Attribute BlockEditor",先点 Read,弹出的 boot_mode 属性中选择 mspix1/x2/x4,然后点击Program 按钮,如图2所示,然后在 TD 主界面重新生成 Bitstream。在 Download 界面中选择 bit 文件,下载模式选择PROGRAM FLASH 下载,如图 3 所示。

图2 boot_mode配置

图3 下载界面

经过上述两部配置后,我的比特流加载时间被从400ms压缩到了20ms左右!

惊喜的发现,将比特流加载时间压缩到50ms以内后,不需要改动PCB,只要把STM32的复位电路从10KΩ+0.1uF改成10KΩ+1uF即可使MCU正常上电复位进入正常工作状态了。

方法二:FPGA加载后复位MCU

前面说过有一种思路是用FPGA在加载完比特流,开始运行以后,在输出一个复位MCU的信号。但这个方法的问题是,FPGA输出复位信号的管脚牵制了MCU的复位管脚,导致其无法通过JLINK调试和下载程序。参考STM32内部WWDG、IWDG和软件复位等多种信号共同控制系统总复位信号的电路,可以采用线与(Wired-AND)的方式管理来自FPGA的复位信号。即在MCU的复位电路上对地并联一个NPN晶体管或N沟道MOS管。参考下图4。

图5 "线与"方式实现来自FPGA的复位信号接入

采用这个电路后,来自FPGA的复位信号不会将MCU的复位管脚钳置到高电平,只会在需要时(输出高电平)打开NMOS管,实现低电平复位MCU。其他时间来自按键或MCU内部的WWDG、IWDG和软件复位都可以将MCU的复位信号拉低,以实现复位。

2、两种解决办法优缺点比较

第一种方法最简单,无需改动电路,且能够降低系统上电到运行的延迟时间。但缺点是当FPGA的比特流较大时,比特流加载时间仍然有可能超过MCU上电复位延迟时间,导致MCU无法正常复位。第二种方法最可靠,但要增加电路或修改PCB。