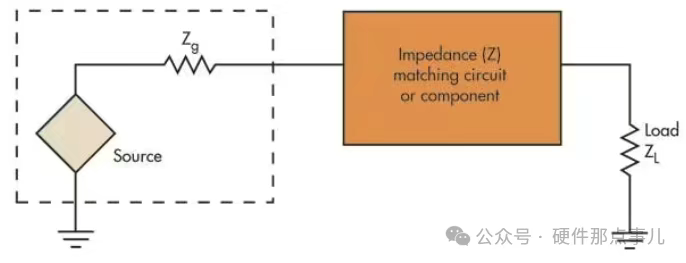

高速电路:阻抗匹配

当你在高速数字电路,如DDR、USB、以太网的信号线上看到一个几十到一百欧姆的电阻时,它的核心使命只有一个,进行阻抗匹配,保证信号完整性。

在低速电路中,我们可以把PCB走线看作理想导线。但在高速世界里,当信号的边沿速率,也就是上升/下降时间快到一定程度时,几厘米的PCB走线就必须被视为传输线。传输线具有一个重要的物理参数------特征阻抗,它通常由PCB的物理结构决定,常见值为单端信号是50Ω或差分信号是100Ω。

当高速信号在传输线上传播时,如果遇到阻抗不匹配的地方,一部分信号能量就会像声波撞到墙壁产生回声一样,被反射回来。在电路中,最大的阻抗失配点通常发生在:

- 信号的驱动端(芯片输出阻抗通常很低,如10-30Ω)。

- 信号的接收端(芯片输入阻抗通常很高,为兆欧级)。

那么这种来回的反射会叠加在原始信号上,造成严重的振铃和过冲,可能导致数据采样错误、逻辑判断失误,甚至损坏芯片。

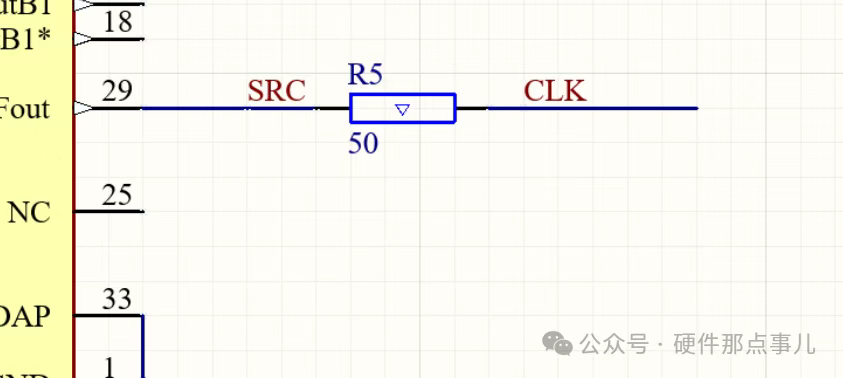

为了驯服反射,聪明的硬件工程师们想到了了一种名为源端串联匹配的技术。就是在紧靠信号驱动端的位置,串联一个电阻 。目标是使驱动端的输出阻抗与串联电阻之和,等于传输线的特征阻抗。由于阻抗完全匹配,返回的反射波能量被完全吸收,不再发生二次反射。振铃被彻底消除。

对于单端信号,50Ω是更常见的标准,因此33Ω、47Ω等电阻更为常用,用于补足芯片自身的输出阻抗。

过流保护与短路防护

当你看到一个1kΩ或更高阻值的电阻串联在信号线上时,它的用途就和高速信号完整性完全无关了。一个1kΩ的电阻会严重破坏高速信号的阻抗匹配,并与线路电容形成巨大的RC延迟。它的主要功能是保护、隔离和滤波,通常用于低速信号或通用输入/输出GPIO引脚。

假设MCU某个引脚用于输出,如果不小心短接到地或电源。如果没有串联电阻,瞬间的大电流会立刻烧毁这个引脚。如果在引脚上串联一个1kΩ的电阻,即使短路到3.3V,电流也只会被限制在 3.3V/1kΩ=3.3mA,这是一个非常安全的水平,足以保护MCU。用GPIO引脚驱动一个指示灯LED时,必须串联一个电阻来限制电流,否则LED会因电流过大而烧毁。

并且在连接两个不同电路板的信号线上,串联一个1kΩ电阻可以防止因两板电位差、上电时序不同或接线错误导致的电流倒灌和芯片损坏。

RC滤波与按键消抖

对于一些慢速信号,如机械按键的输入,串联电阻可以和后级的输入电容组成一个RC低通滤波器。

机械按键在按下和弹起的瞬间,触点会发生多次快速的、不稳定的通断。一个1kΩ电阻和一个0.1μF电容组成的RC滤波器,可以有效地滤除这些高频抖动毛刺,让MCU只接收到一次干净的、稳定的电平变化。