线与"(Wire-And)

数字通信和电路设计中,"线与" 是一种特殊的总线连接逻辑,核心是将多个设备的输出端直接连接在同一条传输线上,通过硬件逻辑实现 "多个设备同时输出时,总线最终状态为'与逻辑'结果" 的功能。它本质是利用特定器件的电气特性(如开漏 / 集电极输出),让多设备共享一条总线,无需额外控制器即可实现简单的多主设备协作或总线竞争处理。

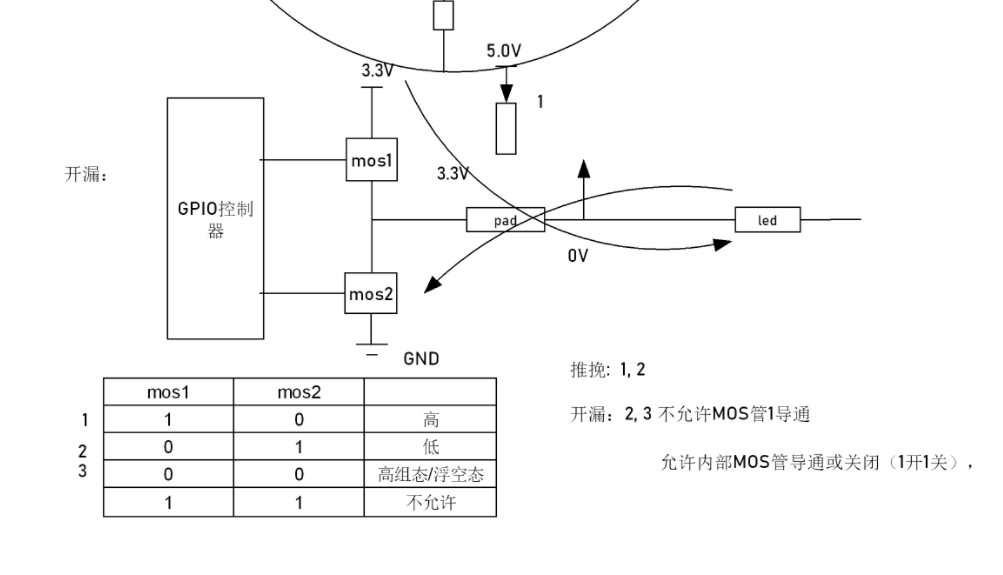

一、"线与" 的核心原理:依赖 "开漏 / 集电极输出" 结构

"线与" 功能无法通过普通的推挽输出(如 TTL 推挽、CMOS 推挽)实现 ------ 因为推挽输出的 "高电平" 是由器件主动输出高电压(如 TTL 的 5V),若多个推挽输出设备同时连接总线,一旦某个设备输出高电平、另一个输出低电平,会导致总线被强制拉到 "高低电平短路" 状态,瞬间产生大电流,烧毁器件或损坏电路。

而 "线与" 必须依赖开漏输出(Open-Drain,OD) 或开集电极输出(Open-Collector,OC) 结构,这类输出的核心特点是:

- 仅能主动拉低总线,无法主动输出高电平:器件输出 "低电平" 时,内部晶体管导通,将总线强制拉到低电平(如 0V);输出 "高电平" 时,内部晶体管截止,总线处于 "悬空" 状态,无法主动提供高电压。

- 需配合上拉电阻实现高电平:为让总线在 "悬空" 时能稳定输出高电平,必须在总线与电源(如 VCC)之间串联一个 "上拉电阻"。当所有设备均输出高电平时(晶体管都截止),总线通过上拉电阻被拉到电源电压(如 5V),表现为高电平;只要有一个设备输出低电平(晶体管导通),总线就会被拉到低电平。

由此,多个开漏 / 集电极输出设备共享总线时,总线的最终状态满足 **"与逻辑"**:只有所有设备都输出高电平(晶体管截止),总线才是高电平;只要有一个设备输出低电平(晶体管导通),总线就为低电平 ------ 这就是 "线与" 的本质逻辑。

1. 线与特性简述

线与是 I2C 总线(SDA、SCL 线)基于开漏输出 + 上拉电阻实现的关键电气特性,核心逻辑为:

- 总线最终电平遵循 "全高才高,一低则低":当所有挂接在总线上的设备均释放总线(内部晶体管截止)时,总线通过上拉电阻被拉至电源高电平(逻辑 "1");只要有一个设备主动拉低总线(内部晶体管导通),总线就会被强制拉至低电平(逻辑 "0")。

- 该特性是 I2C 多主设备协作的基础,例如多主设备同时竞争总线时,通过线与逻辑可实现 "非破坏性仲裁"------ 先拉低总线的设备优先占用,其他设备检测到总线与自身输出不一致时立即释放,避免数据冲突。

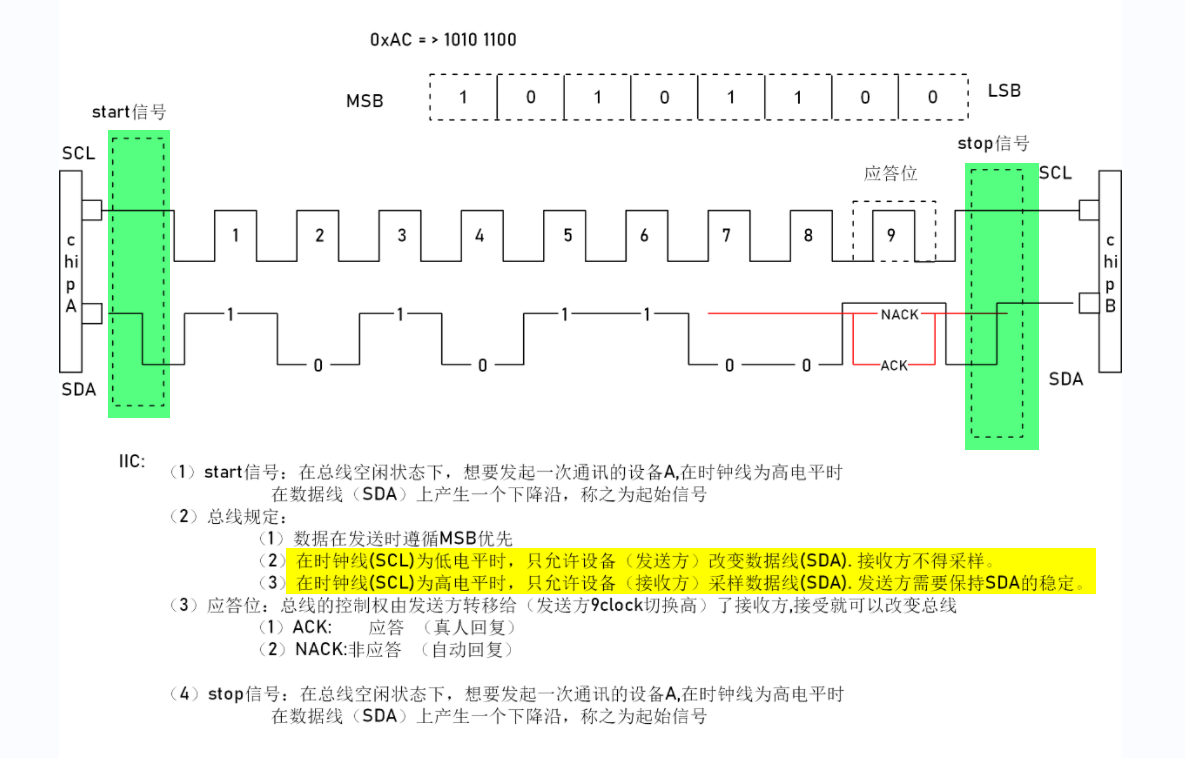

2. I2C 的 Start 信号与 Stop 信号

I2C 的 Start(起始)和 Stop(停止)信号是总线通信的 "边界标记",由主设备生成,通过 SDA 和 SCL 线的电平变化组合定义:

(1)Start 信号(S 信号)

- 定义:在 SCL 线保持高电平(逻辑 "1")的期间,SDA 线从高电平(逻辑 "1")跳变为低电平(逻辑 "0"),此跳变即为 Start 信号。

- 作用:标志一次 I2C 通信的开始,告知所有挂接在总线上的从设备 "即将传输数据",从设备会开始同步 SCL 时钟并准备接收从设备地址。

(2)Stop 信号(P 信号)

- 定义:在 SCL 线保持高电平(逻辑 "1")的期间,SDA 线从低电平(逻辑 "0")跳变为高电平(逻辑 "1"),此跳变即为 Stop 信号。

- 作用:标志一次 I2C 通信的结束,告知从设备 "当前传输已完成",从设备可退出同步状态,总线恢复空闲(高电平)。

关键共性

两者均需在SCL 高电平期间完成 SDA 的跳变 ------ 若 SCL 为低电平时 SDA 跳变,仅视为数据位变化,不被识别为 Start/Stop 信号。

3. I2C 通信时序简述

I2C 通信由主设备主导,完整时序流程可分为 "起始→从设备地址 + 读写控制→应答→数据传输→停止"5 个核心阶段,具体如下:

阶段 1:发送 Start 信号(S)

主设备控制 SCL 为高电平,同时将 SDA 从高拉低,生成 Start 信号,总线进入 "忙" 状态。

阶段 2:传输从设备地址 + 读写控制位(8 位)

- 主设备通过 SDA 线逐位发送7 位从设备地址 (I2C 设备的唯一标识),再发送1 位读写控制位("0" 表示主设备向从设备写数据,"1" 表示主设备从从设备读数据)。

- 传输规则:SDA 线的电平必须在SCL 低电平期间更新 (确保数据稳定),在SCL 高电平期间保持不变(从设备在此期间读取数据位)。

阶段 3:从设备应答(ACK/NACK,1 位)

- 第 8 位(读写控制位)传输完成后,主设备释放 SDA 线(转为输入模式),等待从设备发送应答信号:

- ACK(应答):从设备在 SCL 高电平期间将 SDA 拉低,表示 "已正确接收地址 / 数据",主设备可继续传输。

- NACK(非应答):从设备在 SCL 高电平期间保持 SDA 高电平,表示 "未接收或接收错误",主设备通常会终止通信(发送 Stop 信号)。

阶段 4:数据传输(8 位 / 次,可连续传输)

- 写数据(主→从):主设备逐位发送 8 位数据,每发送完 1 字节,重复 "阶段 3" 的应答流程(从设备发送 ACK/NACK),直至所有数据传输完成。

- 读数据(从→主):从设备逐位发送 8 位数据,每发送完 1 字节,主设备发送 ACK/NACK(ACK 表示 "继续读下一字节",NACK 表示 "读完最后一字节")。

阶段 5:发送 Stop 信号(P)

所有数据传输及应答完成后,主设备控制 SCL 为高电平,同时将 SDA 从低拉高,生成 Stop 信号,总线恢复 "空闲" 状态,一次通信结束。

简化时序总结

Start信号 → 7位从地址+1位读写位 → 从设备ACK → 8位数据 → ACK(循环) → Stop信号