一、Vivado软件安装

下载链接:通过网盘分享的文件:Vivado

链接: https://pan.baidu.com/s/1-uZ594FYP3U0n5c1zWawLw?pwd=4jex 提取码: 4jex

--来自百度网盘超级会员v6的分享

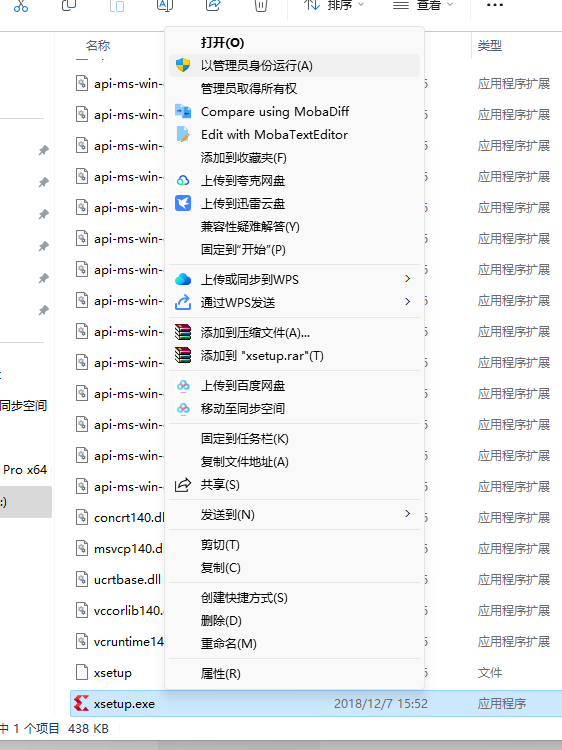

下载完之后,右键点xsetup.exe以管理员方式运行

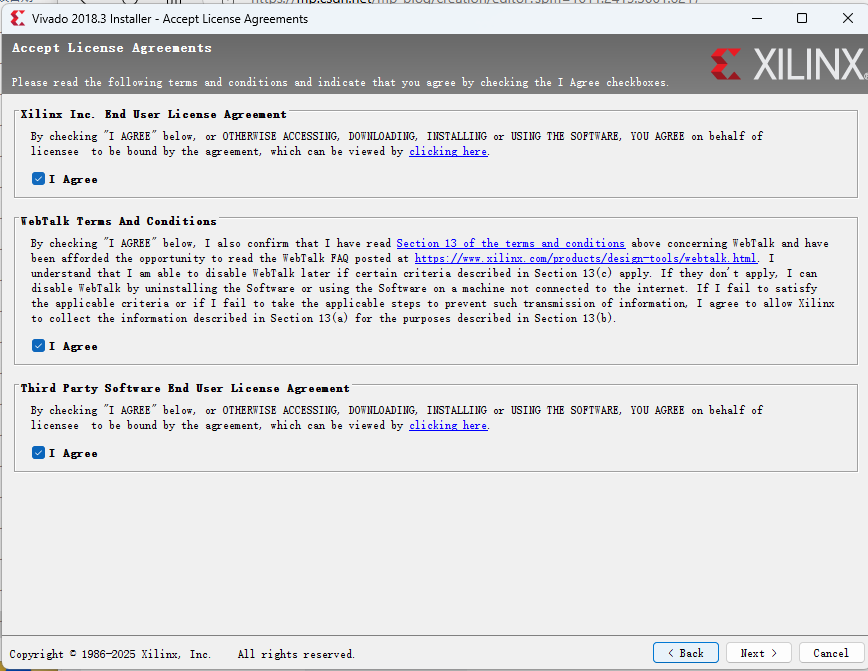

全同意:

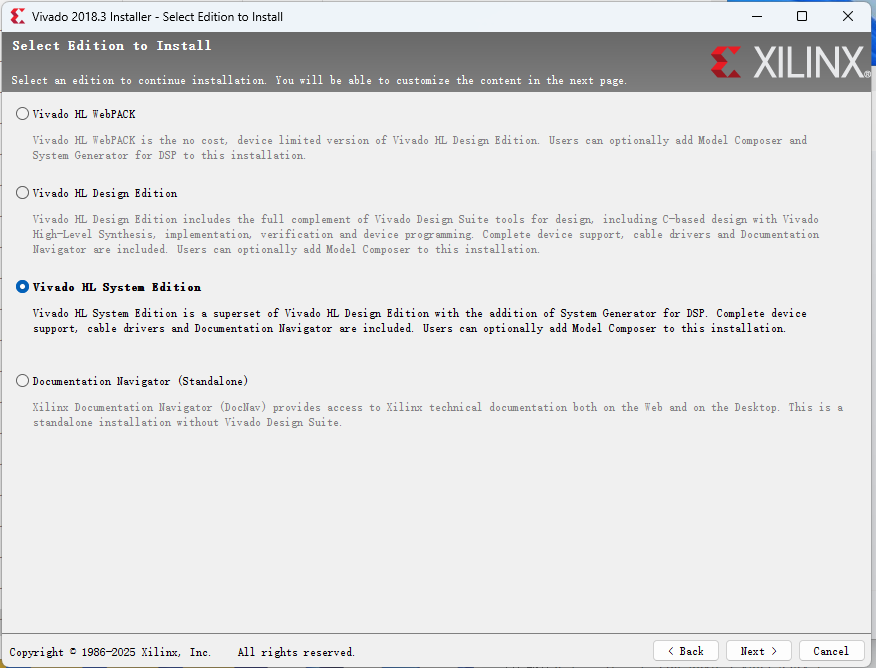

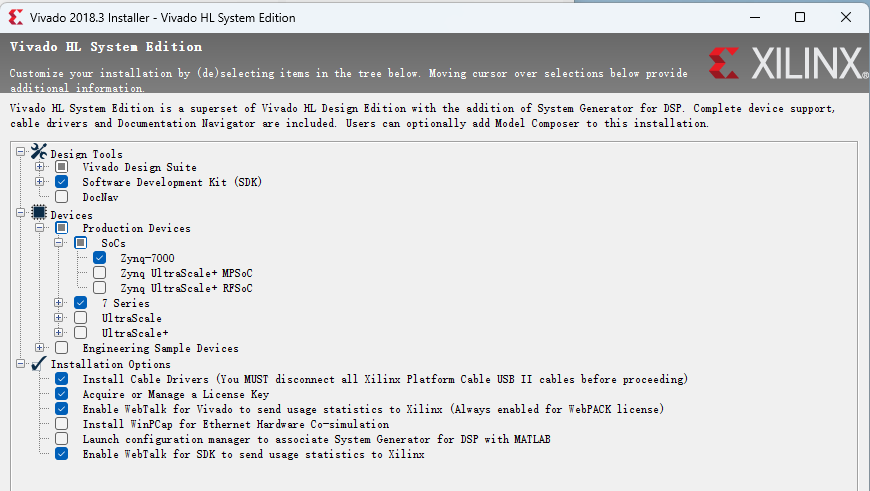

选择第三个

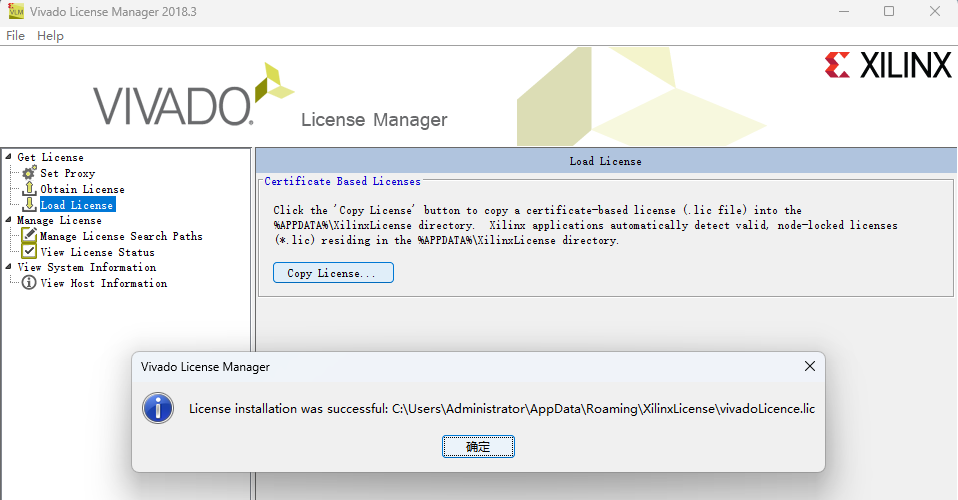

安装完后,点"Copy license",选择.lic文件

二、点灯

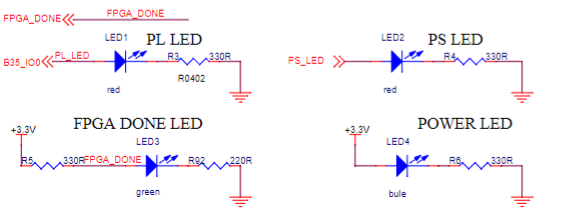

先查看最小系统板的原理图,可以看到LED1的那一头接的网络名称是B35_IO0

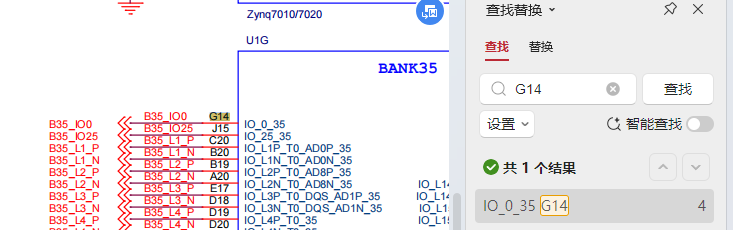

然后在文档中搜索B35_IO0,可以看到这个网格名对应的是G14,那么对应的引脚约束文件中就要写G14

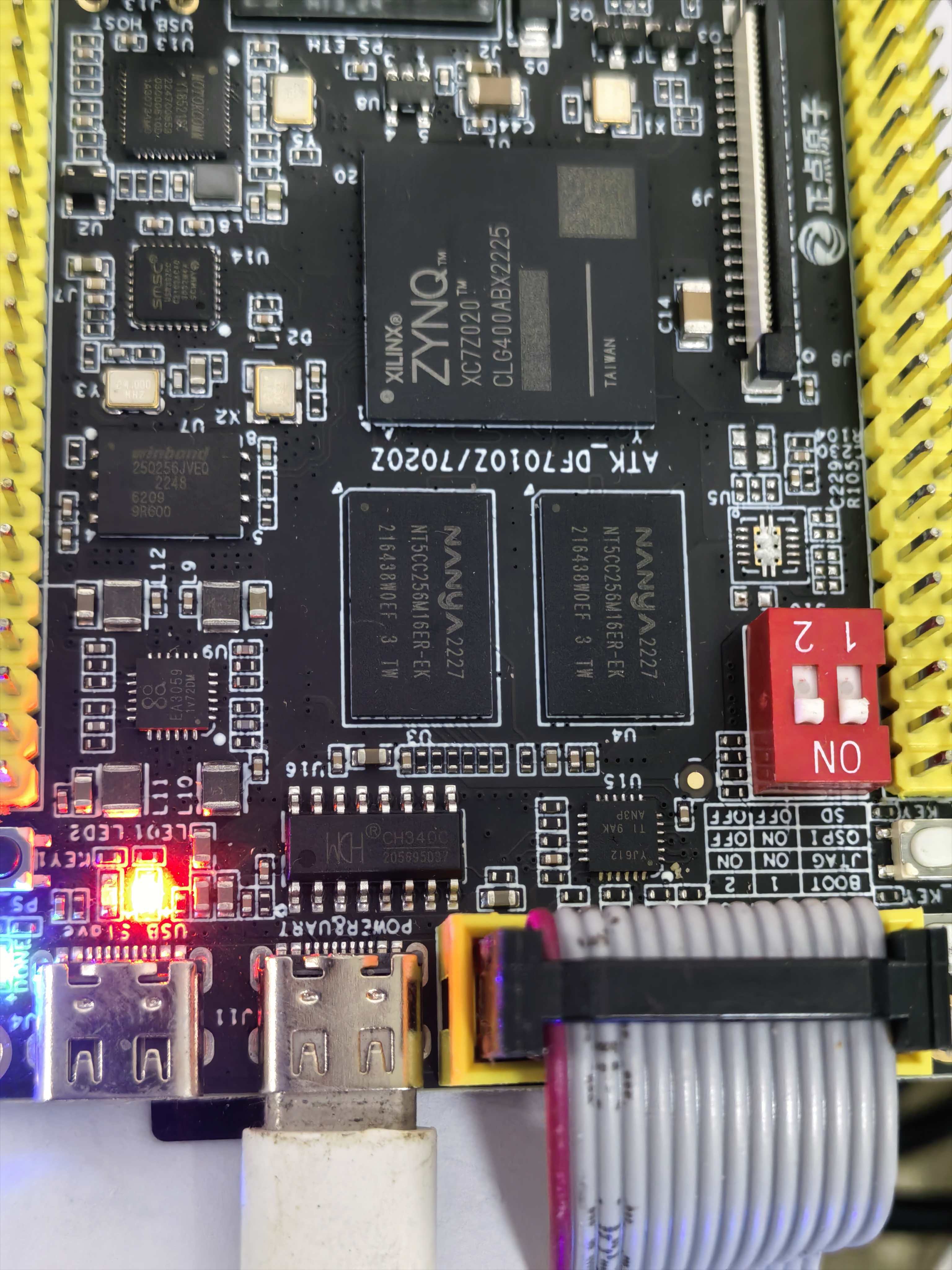

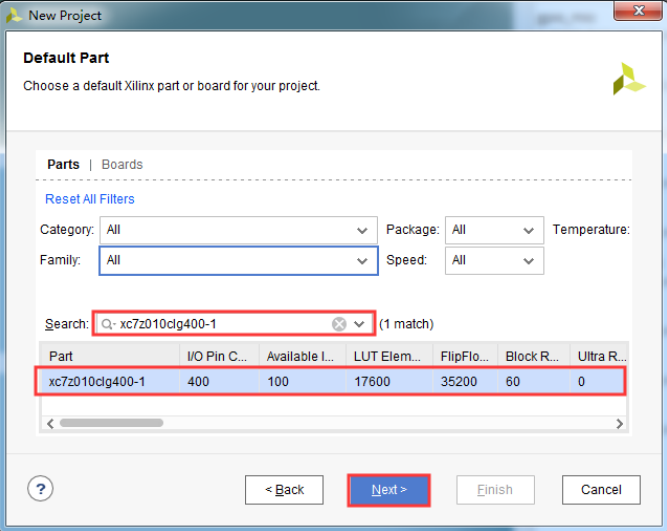

那么新建一个项目,除了下面型号选择:xc7z010clg400-1

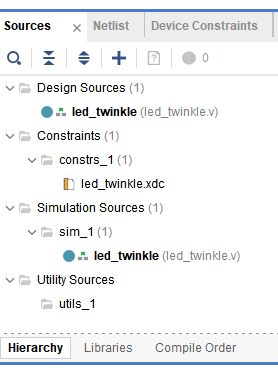

其余部分一路点确定,不熟悉可以看看官方文档,整体的文件路径如下:

led_twinkle.v代码如下:

bash

module led_twinkle(

input sys_clk, // 系统时钟

input sys_rst_n, // 复位信号,低电平有效

output led // 单 LED 输出,连接到 G14 引脚

);

reg [25:0] cnt;

// LED 闪烁逻辑:当 cnt < 2500_0000 时,led = 1(点亮);否则 led = 0(熄灭)

assign led = (cnt < 26'd2500_0000) ? 1'b1 : 1'b0;

// 计数器逻辑:基于 50MHz 时钟,计数到 5000_0000(1秒),然后复位

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

cnt <= 26'd0;

else if (cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmoduleled_twinkle.xdc代码如下:

bash

#时钟周期约束

create_clock -name clk -period 20 [get_ports sys_clk ]

#IO 管脚约束

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN G14 IOSTANDARD LVCMOS33} [get_ports led]然后vivado左侧框有很多绿色运行的按钮,点击的先后顺序和运行意义如下:

-

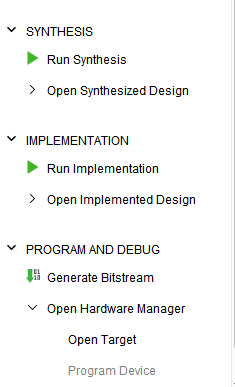

Run Synthesis

- 作用 :将你的Verilog 代码 (

led_twinkle.v)转换为硬件网表 (netlist),并应用约束文件(led_twinkle.xdc)中的时钟和引脚约束。 - 操作 :在 Vivado 的

Flow Navigator中,点击 Run Synthesis。 - 检查 :

- 确保

led_twinkle.v和led_twinkle.xdc已正确添加到项目中,且led_twinkle.xdc被设置为目标约束文件。 - 综合完成后,检查

Messages或Reports窗口,确认没有错误(errors)。如果有警告(warnings),如之前的[Constraints 18-5210],需参考历史对话中的解决方法(例如,检查约束文件是否正确加载)。 - 综合成功后,会生成一个合成检查点文件(例如

led_twinkle.dcp)。

- 确保

- 作用 :将你的Verilog 代码 (

-

Run Implementation

- 作用 :将综合生成的硬件网表 映射到目标器件(

xc7z010clg400-1)的物理资源上,进行布局(placement)和布线(routing),并优化设计以满足时序要求。 - 操作 :在

Flow Navigator中,点击 Run Implementation。 - 前置条件 :必须先成功完成

Run Synthesis。 - 检查 :

- 实现完成后,检查

Messages或Log窗口,确认没有错误。如果有错误(例如时序违例或引脚分配问题),需检查led_twinkle.xdc文件中的引脚分配是否与开发板匹配。 - 打开

Timing Summary报告,确认时序约束是否满足(即没有负的时序裕量,negative slack)。 - 实现成功后,会生成布局布线后的设计检查点。

- 实现完成后,检查

- 作用 :将综合生成的硬件网表 映射到目标器件(

-

Generate Bitstream

- 作用 :将实现后的设计转换为比特流文件 (

.bit),该文件可下载到 ZYNQ7020 开发板的 FPGA 上以控制硬件(例如 LED 闪烁)。 - 操作 :在

Flow Navigator中,点击 Generate Bitstream。 - 前置条件 :必须先成功完成

Run Implementation。 - 检查 :

- 比特流生成完成后,检查

Messages窗口,确认没有错误。 - 成功后,Vivado 会在项目目录的

runs文件夹中生成比特流文件(例如led_twinkle.bit)。 - 如果生成失败,查看详细错误日志,可能的原因包括引脚分配错误、时序未满足或约束文件问题。

- 比特流生成完成后,检查

- 作用 :将实现后的设计转换为比特流文件 (

-

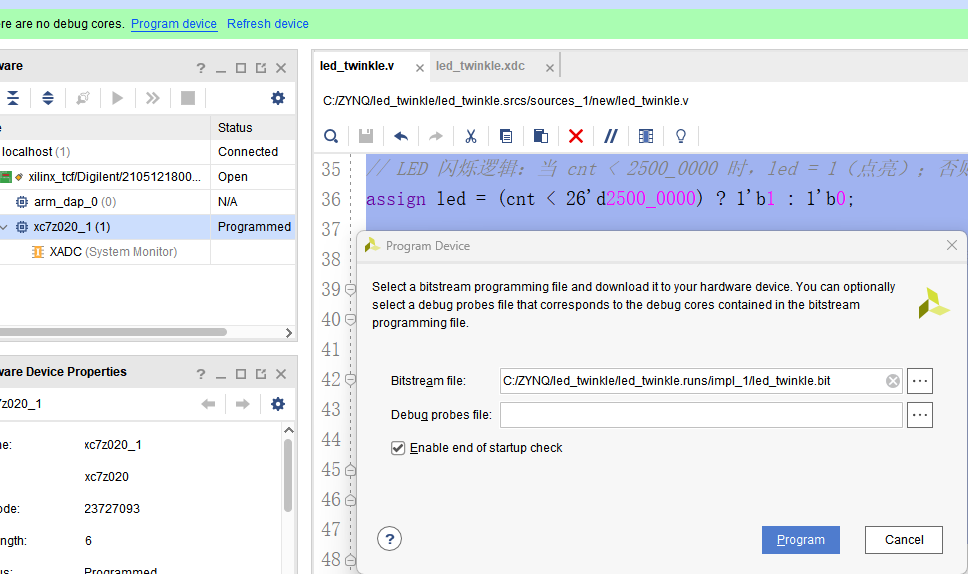

下载到硬件(可选,运行程序到开发板)

- 作用:将生成的比特流文件下载到 ZYNQ7020 开发板,运行 LED 闪烁程序。

- 操作 :

- 连接 ZYNQ7020 开发板到电脑,确保开发板电源已打开。

- 在

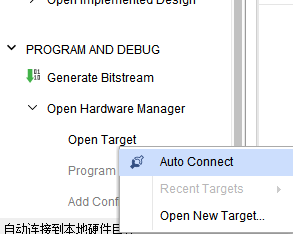

Flow Navigator中,点击 Open Hardware Manager。 - 点击 Open Target -> Auto Connect,连接到你的开发板。

- 选择 Program Device ,选择你的设备(

xc7z010clg400-1),然后加载生成的.bit文件。 - 点击 Program 将比特流下载到开发板。

然后观察现象可以看到红色的灯在每隔1s闪烁: