时钟占空比适用条件

时钟占空比参数,只有在时钟频率为快速模式,即大于100KHZ ,小于等于400KHZ 的情况下才有用。 在小于等于100kHz的标准速度下,占空比是固定的1:1。

那么为什么时钟占空比只有在时钟频率为快速模式时才有用??

我们熟悉的频率,就是周期的倒数。通常频率越大,周期越小,频率越小,周期越大。

在标准模式时,频率范围是0- 100Khz。此时时钟周期较长 ,每个SCL时钟的边沿变化都有足够的时间 来稳定数据 和采样数据。

由于SCL为复用开漏输出 ,它就像一个杆子模型 ,每次我们都用很大的力气将杆子拉低(置低电平),那么它电平的变化就非常快 。但是当我们松手时,杆子是不会立刻回到高电平的,它会有一个缓慢的过程。

当I2C模式为快速模式时,频率较大 ,频率范围是100khz- 400Khz。此时时钟周期较短,又由于杆子回弹的过程很耗时间,就会对波形产生影响。

如果在低电平时没有足够的时间回到高电平,那么高电平就难以稳定,从而数据就难以读取。

时钟占空比的参数

时钟占空比分别有16:9和2两种参数,16:9就是SCL时钟的低电平时间比高电平时间为16:9 。2就是是SCL时钟的低电平时间比高电平时间为2:1。

为什么时钟的占空比表示的是低电平与高电平的比值?

我们通常学习的占空比,比如PWM。都是高电平 占整个周期的比值。但是I2C协议有一个铁律:SCL时钟的低电平时间(tLOW)必须大于 或等于高电平时间。

那么为什么时钟的占空比表示的是SCL的电平时间,而不是SDA的电平时间??

因为SCL代表的是时钟信号,是周期性和稳定性的。负责为整个通信提供节奏,SCL的高低电平的比值对通信节奏非常关键。

而SDA的高低电平取决于需要传输的数据的内容,因此它并不是周期性的,也就没有占空比的概念了。

波形图

下面我给大家看一看来自江科大标准库课程中的波形图

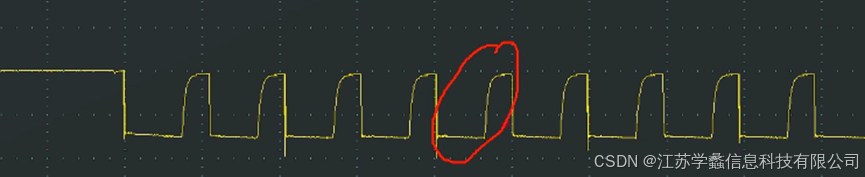

101KHZ

此图为101KHZ的波形,101KHZ已经属于快速状态了,此时时钟占空比参数就会工作。

当我们选择占空比为2:1的参数时,低电平比高电平,就由原来的1:1变为大概2:1 ,增大了低电平时间占整个周期的比例。

因为低电平时数据变化 ,高电平读取数据。尤其是图中可以看出,数据由低电平到高电平时上升比较缓慢。

所以在快速传输的状态下,我们需要给低电平多分配一些时间,要不然低电平数据变化来不及你高电平数据读取也没用。

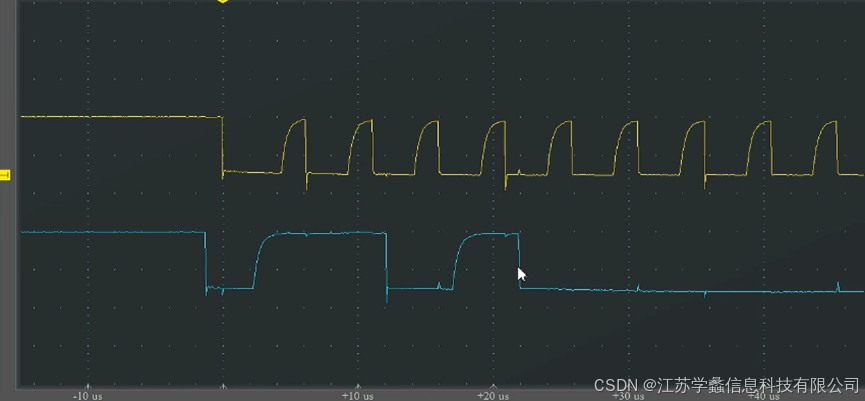

200KHZ

接着继续看时钟频率为200Khz的图

由于时钟频率为200KHZ,此时周期进一步缩小,留给低电平变化的时间也进一步缩小。此时图中弯弯的上升沿 会变得更加明显。

400KHZ

最后我们看一下最快的速度400KHZ的波形图

可以看到SCL还没完全回弹到高电平呢,就又被立刻下拉了。

所以此时这个SCL波形就变成了三角形了。

总结:

标准模式(此时时钟占空比默认为1:1)下由于频率较小 ,导致周期充裕,所以即便不设置时钟占空比,数据在SCL变高前就有足够的时间稳定下来。

而快速模式下由于频率较大 ,导致周期减小,为了保证数据在SCL变高前有足够的时间稳定下来,此时时钟占空比就生效。

由于I2C协议强制要求低电平时间(tLOW)必须不小于高电平时间(tHIGH) 。且时钟占空比主要是为了增加低电平的时间,让低电平回到高电平,从而能够稳定的采样数据。

所以SCL占空比为低电平占总时间的比重。

这是我对时钟占空比的粗略见解,有什么问题欢迎指正或补充,大家共同进步!