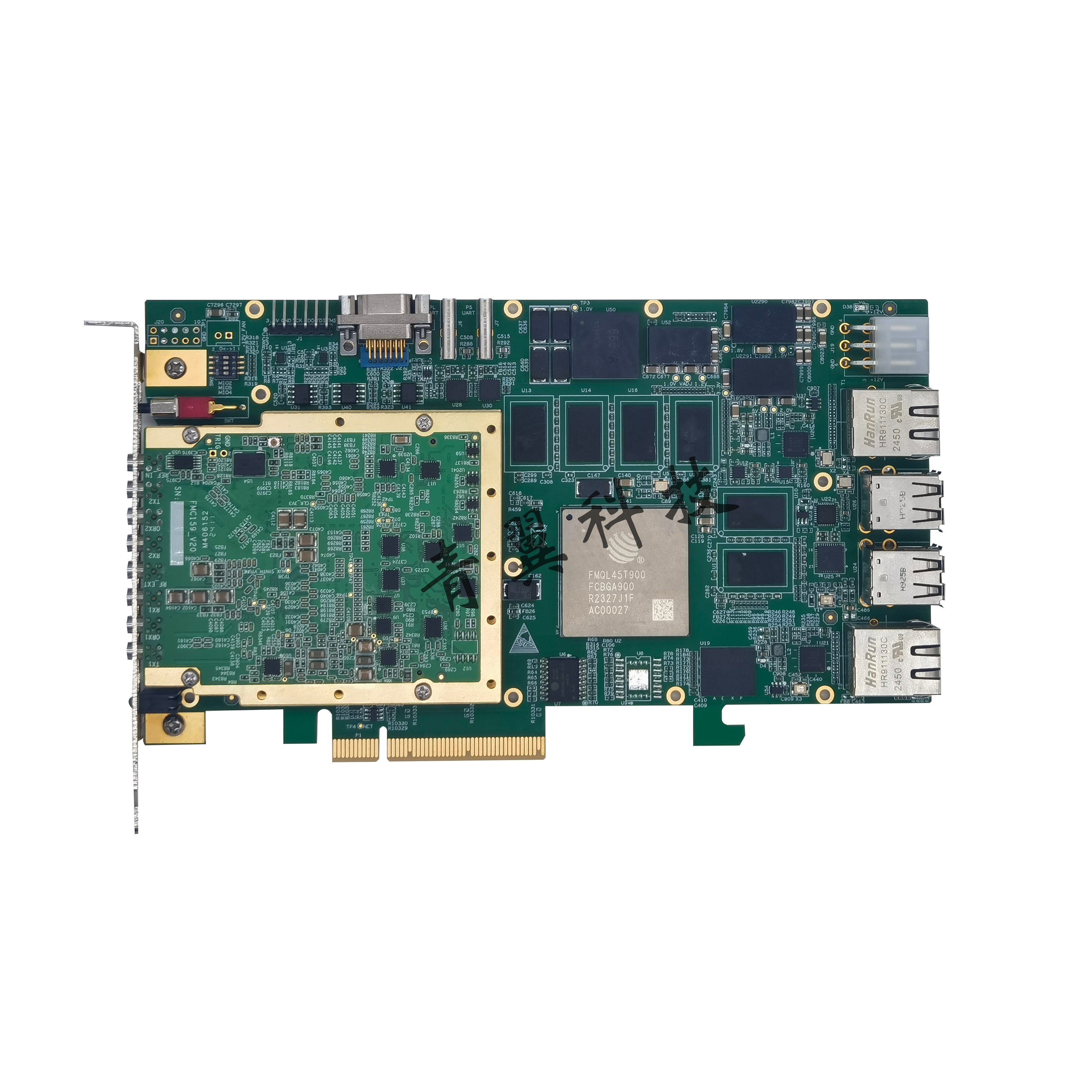

产品概述

PCIE716-159是一款基于PCIe总线架构的国产化双通道射频收发处理平台。该平台基于国产化ADRV9009射频收发器,涵盖了50MHz~6GHz频段,并集成了双通道收发链路,发送最大实时带宽可到450MHz,接收最大带宽可以到200MHz,是一款高度集成的通用软件无线电平台。

该平台采用X8 PCIe总线接口,接收和发送数据可以通过PCIe总线完成与主机端的交互。

该平台主要应用于仿真验证平台、5G微基站等高性能低功耗的射频收发应用场景。

技术指标

- 板载PSOC FPGA实时处理器:JFMQL45T900;

-

4核处理器,最高工作频率可以达到800MHz;

-

可编程逻辑单元:350K;

-

PS端支持1组1GByte DDR3 SDRAM,时钟500MHz;

-

PS端支持2片QSPI Flash,每片容量256Mbit;

-

PS端支持4路USB2.0接口;

-

PS端支持1个TF-Card接口;

-

PS端支持1个RJ45千兆以太网接口;

-

PS端支持1片512Kbit EEPROM存储;

-

PL端支持1组64位DDR3 SDRAM,容量2GByte;

-

PL端支持1个RJ45千兆以太网接口(EMIO);

- 射频收发性能指标:

-

芯片型号:国产ADRV9009;

-

集成2路发射器,支持50MHz~6GHz可调;

-

集成2路接收器,支持50MHz~6GHz可调;

-

发送器最大带宽:450MHz;

-

接收器最大带宽:200MHz;

-

集成接收通路自动增益控制算法;

-

数字端接口:JESD204B,单通道速率最高可达12.888Gbps;

-

集成发射通路PA保护算法 ;

-

接口类型:SMP射频接口;

-

FMC接口:HPC;

-

集成2路高带宽观察通道,实现DPD功能;

-

观察通道最大带宽:450MHz;

- 物理与电气特征

-

板卡尺寸:111.15 x 190mm;

-

产品供电:4A max@+12V;

- 环境特征

-

工作温度:-40°~85°C;

-

贮存温度:-55°~125°C;

-

工作湿度:5%~95%,非凝结;

软件支持

- 底层接口以及驱动程序:

-

射频收发测试程序;

-

PCIe总线通讯测试程序;

-

PS与PL底层接口驱动程序;

- 可根据客户需求提供定制化算法与系统集成:

应用范围

-

3G/4G/5G TDD基站;

-

TDD有源天线系统;

-

相控阵雷达、电子战、MIMO;

-

便携式测试设备。