目标:学习Verilog实现时序逻辑的写法以及计数器的应用

实验现象:当实验程序下载到开发板后,开发板上的D0(即LED0)以1Hz的频率闪烁,即一秒钟之内亮灭各保持500ms或LED的状态每隔500ms翻转一次

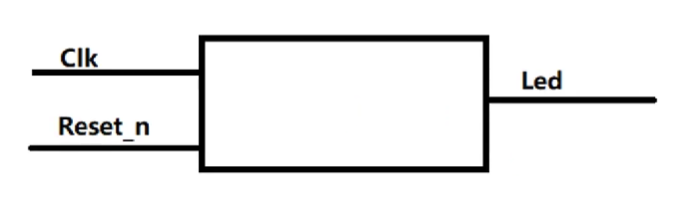

1.设计定义

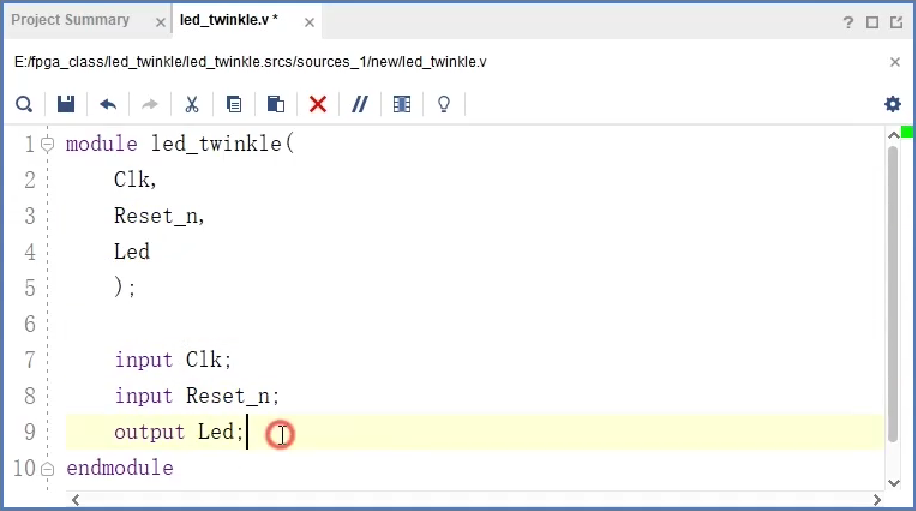

对于该模块,理论上只需要两个端口

一个Clk给D触发器提供时钟信号,一个Led驱动开发板上的Led灯亮灭

Reset_n 是低电平复位信号 ,reset代表复位,_n代表低电平有效

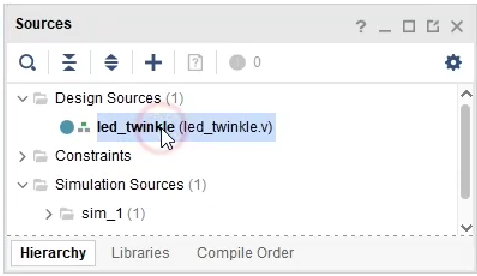

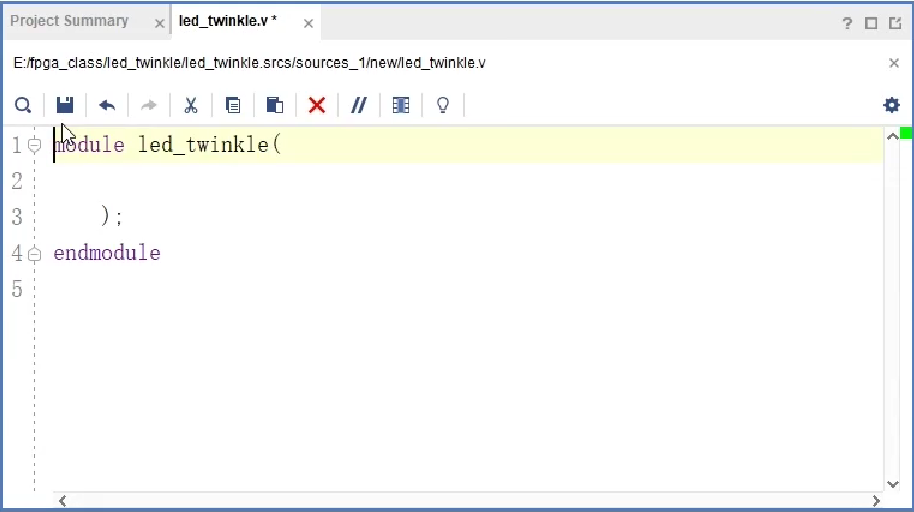

2.建立工程

工程名称为led_twinkle

创建与工程同源的Verilog源文件

3.程序编写

写基本框架

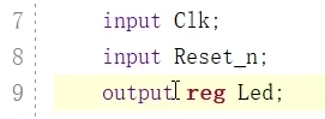

端口列表和端口定义

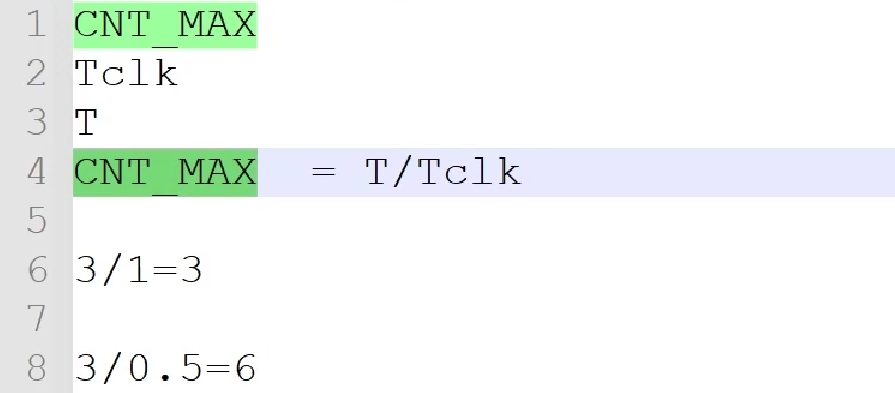

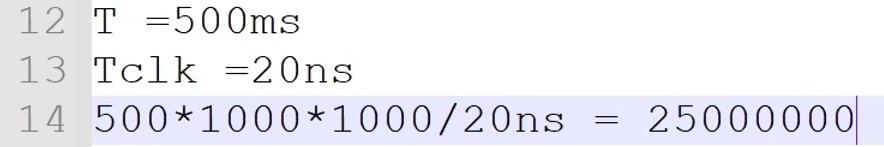

计数器的计数最大值称为CNT_MAX

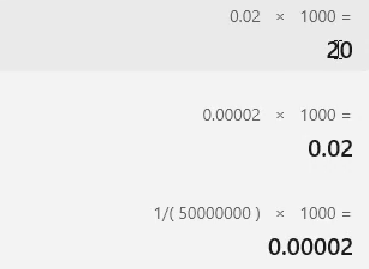

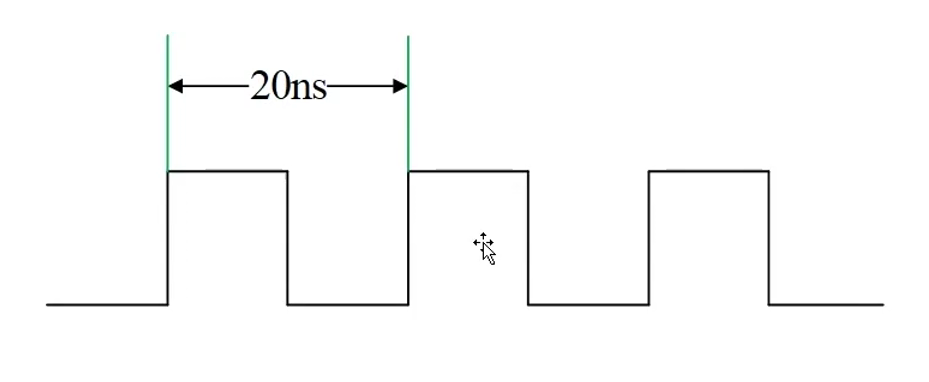

D触发器的工作时钟周期为Tclk

需要定时的时间长度为T

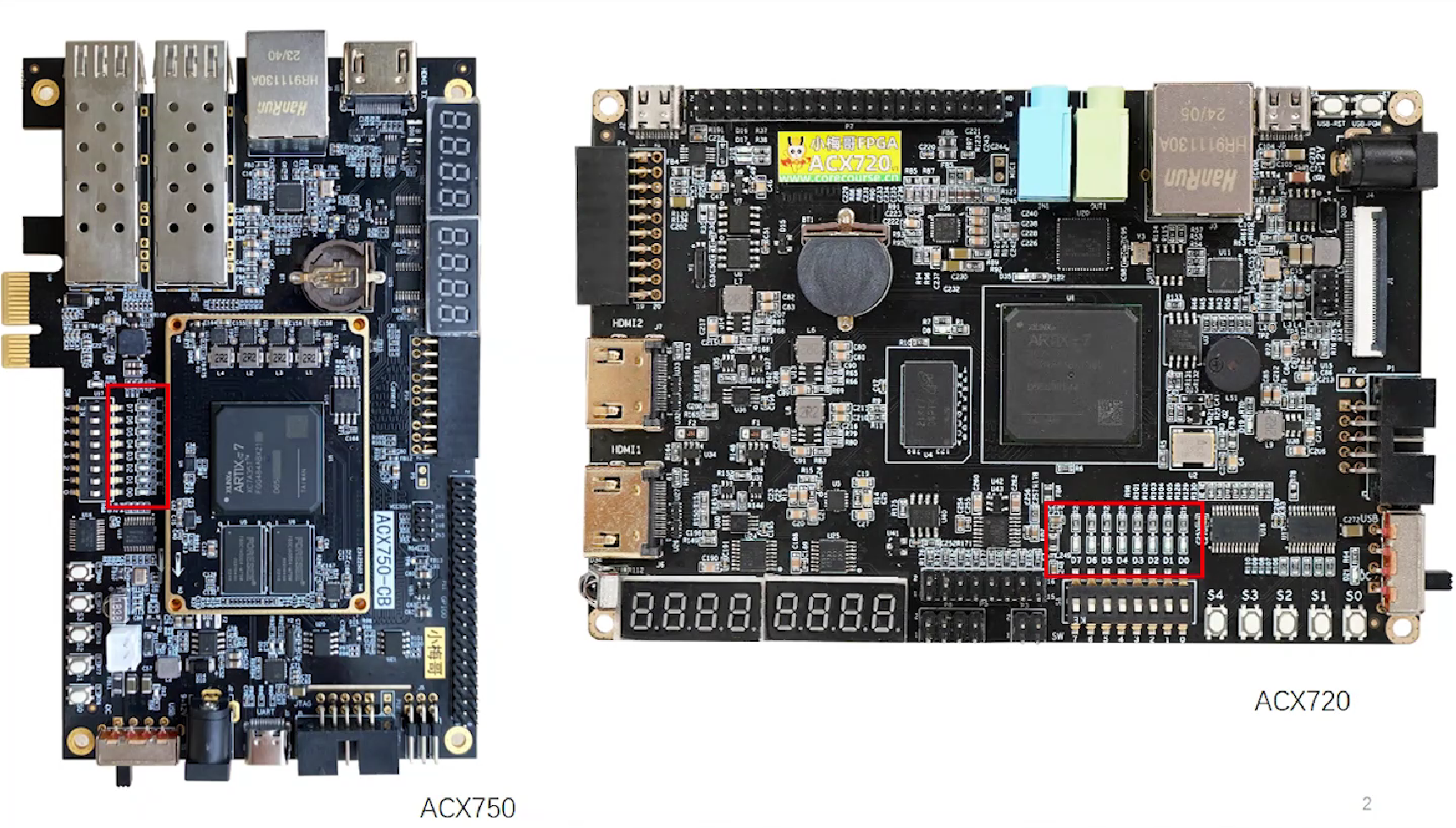

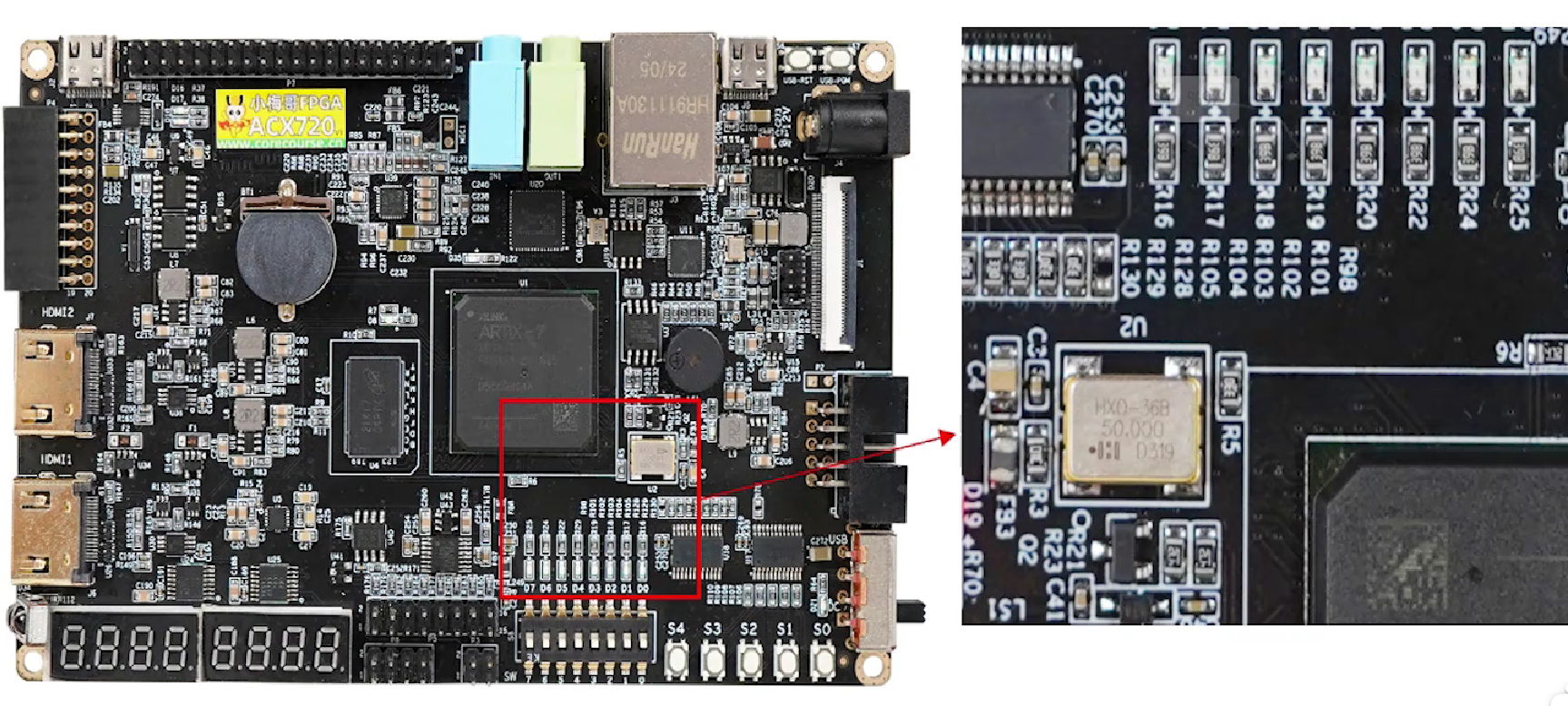

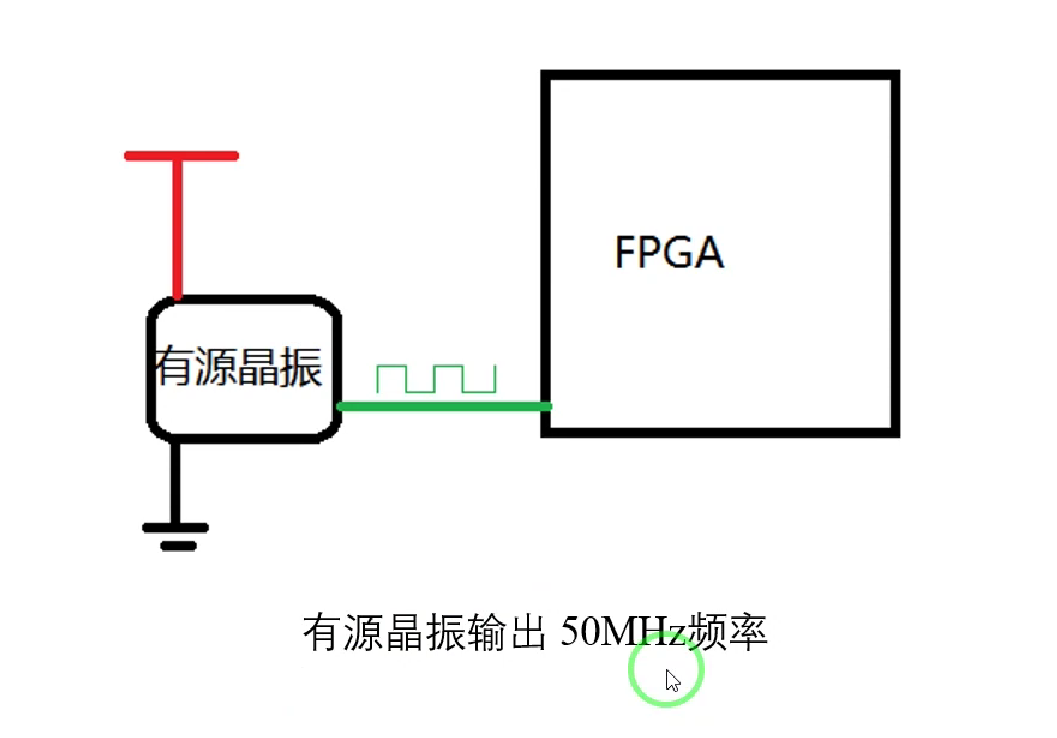

在FPGA系统中,时钟信号通常由电路板上的一个能够主动生成周期性的时钟信号的元件产生,也就是俗称的有源晶振。

有源晶振在加电的情况下能够输出频率非常稳定的方波信号,将这个方波信号连接到FPGA的一个管脚,就可以在程序中使用这个信号了。

ACX720开发板上的有源晶振输出固定的50MHz的频率

该晶振输出的时钟信号的周期是20ns

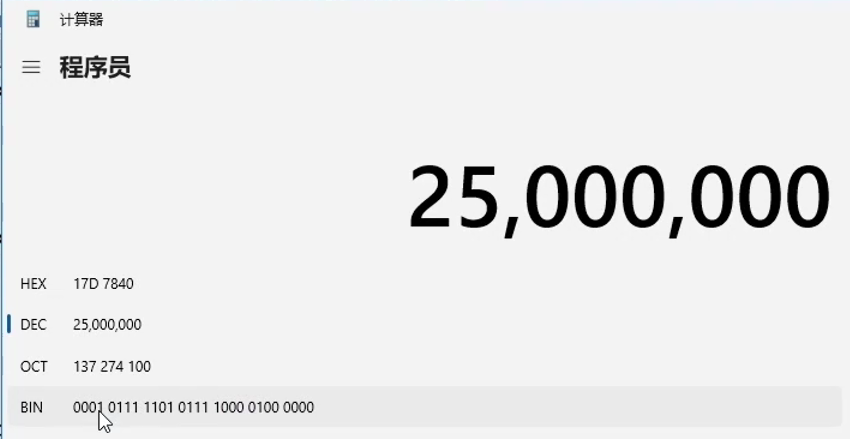

通过计算器的二进制可以看到位宽至少是25位

只要定义的位宽能够表示需要表示的数即可

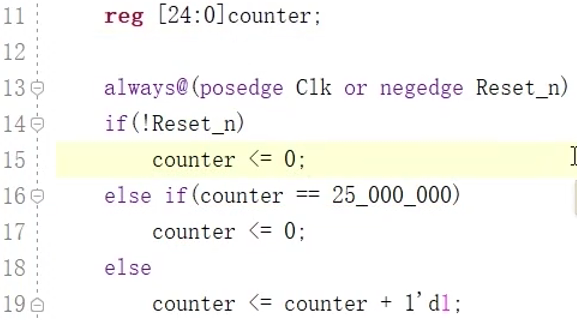

计数器的核心代码

第13行代码是过程赋值语句,是描述时序逻辑的标准格式,or negedge Reset_n 可以省略不写

posedge表示上升沿 negedge表示下降沿

Reset_n为低电平0,取非为1,if条件为真,满足则执行第15行代码,把counter的值设置为零

如果Reset_n为1,取非为0,不满足则不执行第15行代码

第14和15行代码是描述一个信号的复位逻辑 的典型语句

复位:通过设置让D触发器的值作为一个确定的预设值

else if 后的内容是计数器正常工作、正常计数时的逻辑代码

25_000_000前面没有加格式限定符和位宽限定符,默认是十进制

这里的 <= 代表非阻塞赋值

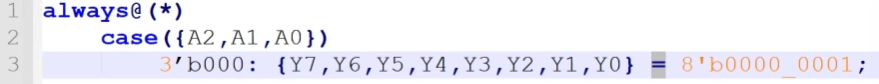

三八译码器里的 = 代表阻塞赋值

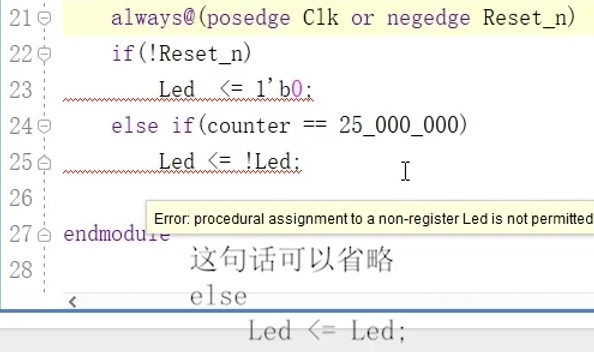

Led翻转代码

这里报错的原因是LED在过程语句中被赋值,但是Led又不是寄存器或reg类型的信号,这在语法中是不允许的,解决办法是在Led前面加上reg

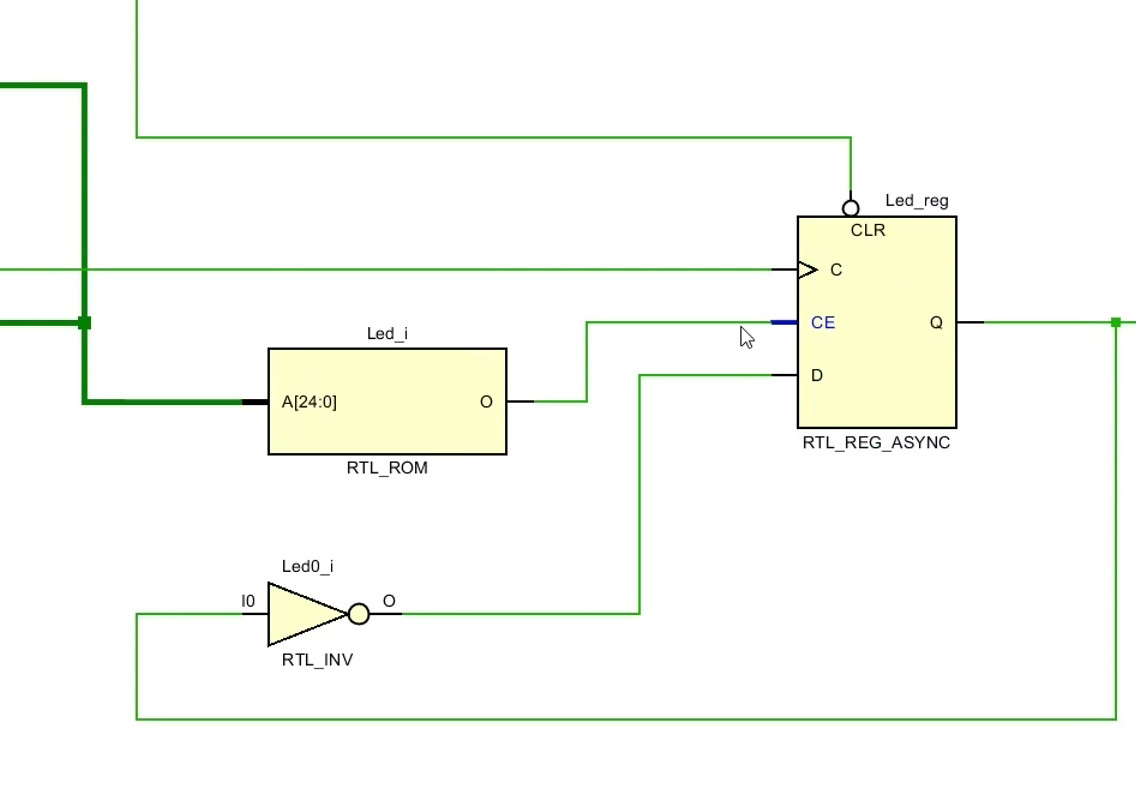

4.图纸分析

打开设计的原理图图纸

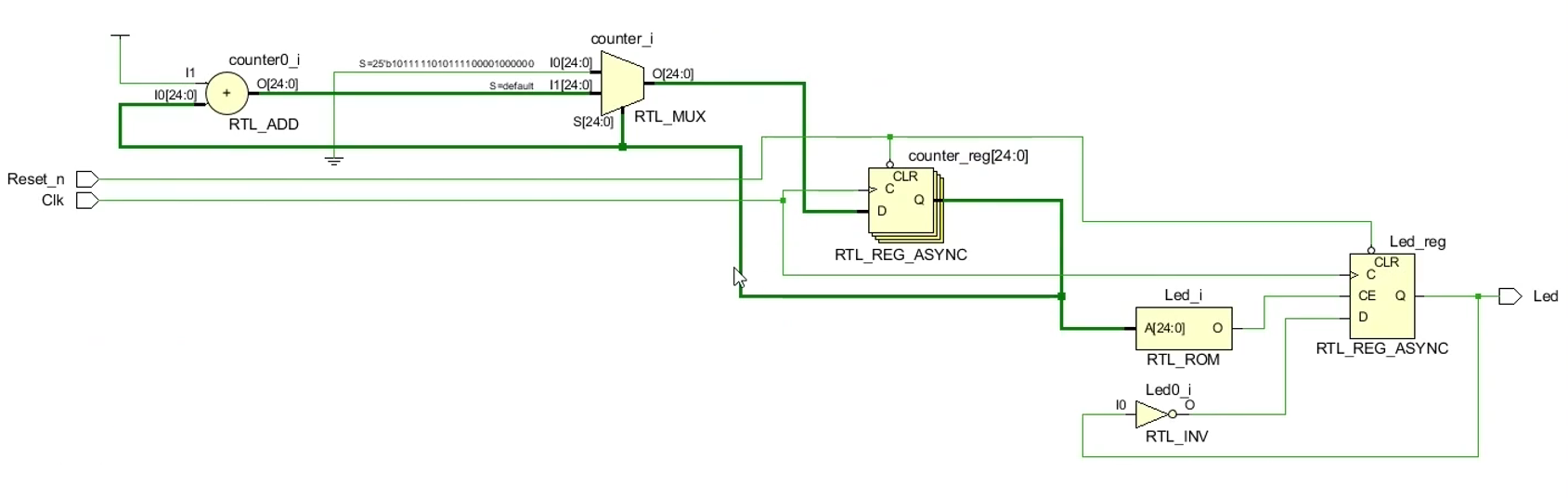

图纸中有加法器、二选一多路器、D触发器、反相器

加法器的两个输入,一个来源于VCC,一个来源于counter的输出值

加法器的输出端到D触发器的输入端之间多了一个二选一多路器

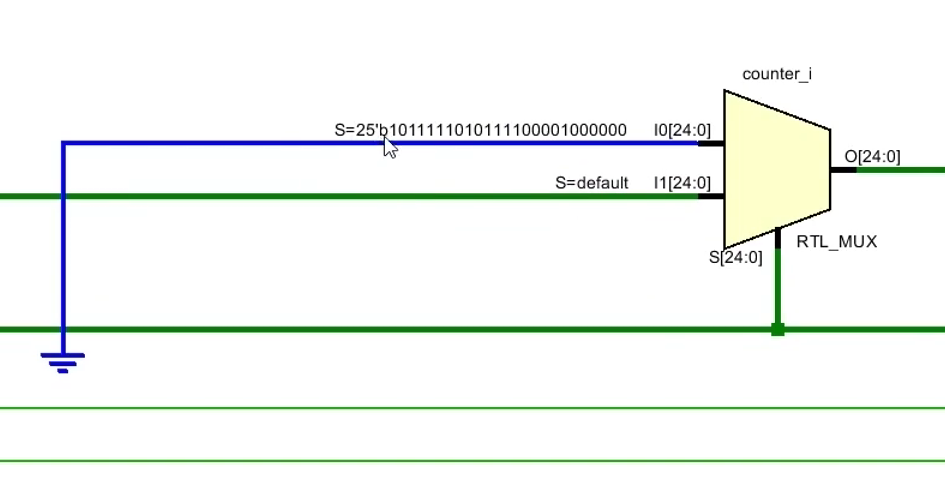

二选一多路器会根据counter的值来决定输出给D触发器的值是加法器的结果还是

I0口的数据转换为十进制就是25_000_000,二十五位的多路选择器的选择位宽也是二十五位,当它的S端口为25_000_000时,多路器输出上面一路的值,否则输出下面一路的值

Led的输出也是通过D触发器输出,输出经过反相器绕回D触发器的输入端口

CE端口代表时钟使能,该端口的作用是,只有当CE信号为高电平的时候,CLK的信号才能进入D触发器的CK端口,才能驱动D触发器储存D端口上的数据,否则CLK的信号不会进入D触发器

这样只有能实现CE信号每25_000_000个时钟出现一次高电平,就能够让D触发器每25_000_000个时钟周期,只更新一次数据,从而实现每25_000_000个时钟Led翻转一次

CE信号由RTL_ROM产生,它根据counter的输出值进行判断,仅当counter的输出值为25_000_000时,O输出高电平从而控制Led触发器更新数据的节奏