LVDS数据仿真:

本设计,是基于外部LVDS电路是处于理想情况下进行的,也就是在ADC芯片输出端口和PCB板上,硬件设计者通过等长布线确保了 DCLK的边沿正好对准数据眼的中心(90°相位差)。此时,如果用这个比特时钟直接采样数据,时序最佳,但是这只是FPGA端口处的情况,离FPGA内部逻辑实现还有一段距离;

在进入FPGA后,情况就比较复杂了:

对于数据路径和FCLK帧时钟路径,LVDS数据进入FPGA引脚后,经过IBUFDS,直接连接到ISERDESE2原语的D输入端口,这条路径是专用的比较直接的硬件连线,也就是说,帧时钟和数据通道,到需要FPGA内部采样时,还能保持,相对于FPGA端口处理想时序来说比较好的时序关系;

但是对于时钟路径,比特时钟进入FPGA引脚后,FPGA为了使用该时钟去采样去驱动ISERDESE2,不能直接连接到ISERDESE2的CLK端口,比特时钟需要经过以下路径:先进入时钟专用引脚,经过IBUFGDS或IBUFIO,经过BUFIO或BUFR,最后通过FPGA的全局或区域时钟树,布线到各个CLK或CLKDIV端口,可以看到,时钟路径会和数据路径完全不一致,且时钟路径延时会长的多,且无法去确定其延时,如果直接使用其去采集,采样结果将完全无法预测;

所以本次设计,主要目的,就是使用FPGA端口处,时序良好的比特时钟,去派生出一个FPGA内部使用的采样时钟和分频时钟,然后用IDEAYE2去把内部的采样时钟,和FPGA端口处的采样时钟去对齐,因为端口处采样时钟和数据路径关系比较理想,所以把内部采样时钟和端口处采样时钟,两者对齐后,内部采样时钟也能尽量对齐数据路径的数据眼中心;

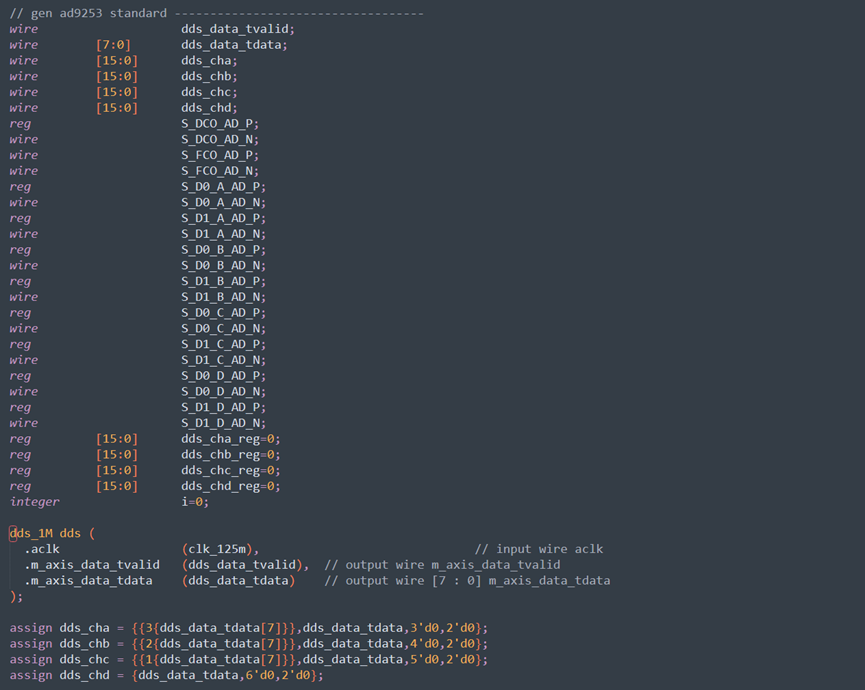

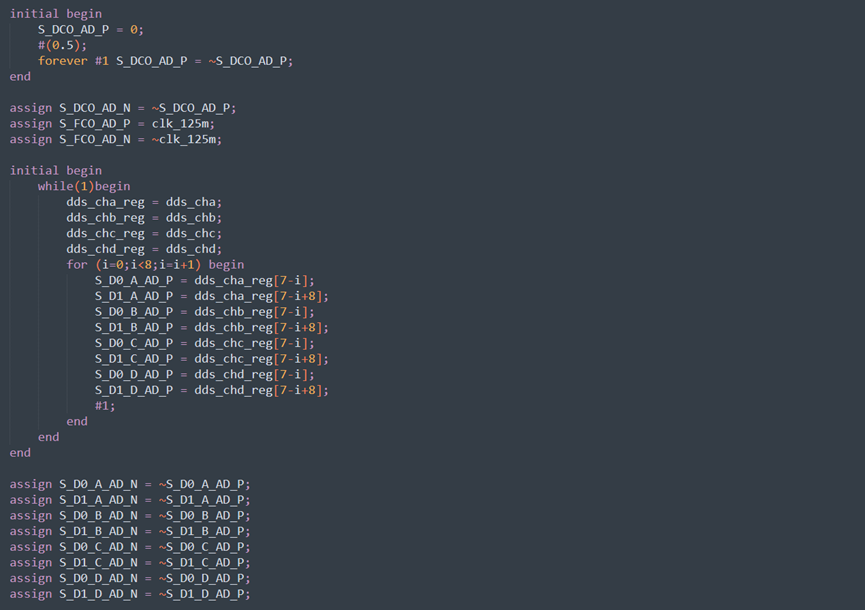

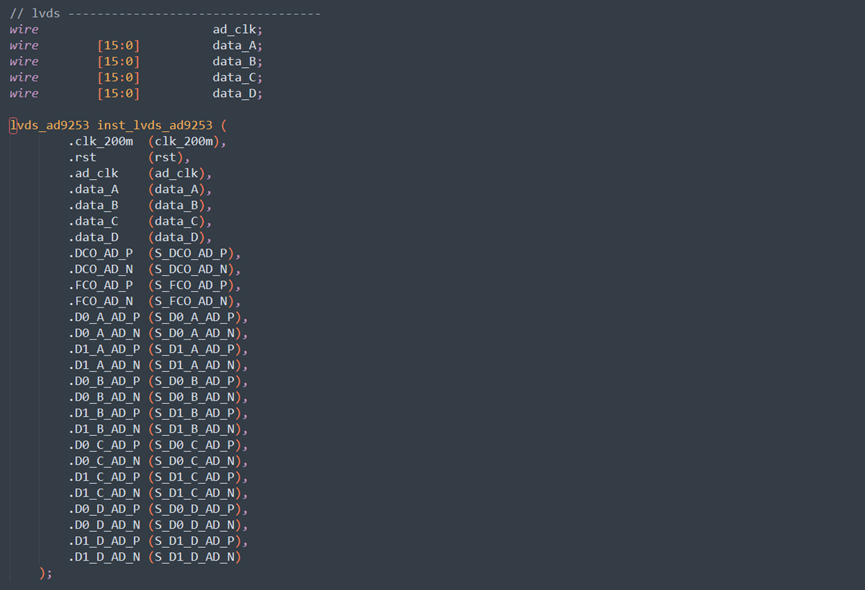

本次仿真,是tb中产生标准的ad9253的时序输入,用模块进行处理,tb模拟产生的,模拟FPGA输入端点处理想的输入时序,

Testbench:

仿真结果:

dds产生1M的正弦波,4个通道修改不同的幅度,模拟LVDS时序输入模块进行处理;

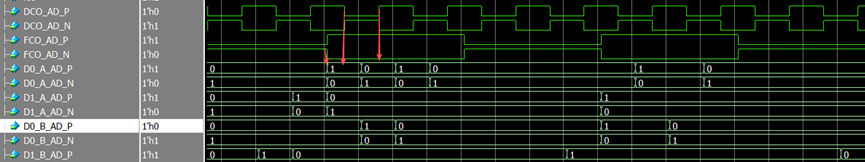

输入的lvds时序:

比特时钟对齐数据眼中心,数据边沿和帧时钟边沿对齐,和ad9253的时序一致;

可以看到下图中,是采样出来输出的数据波形,其中分成3个时间段,下面图中红字标准,时间段1,是还没有做对齐操作,时间段2,是对齐过程中,时间段3,是对齐稳定后,

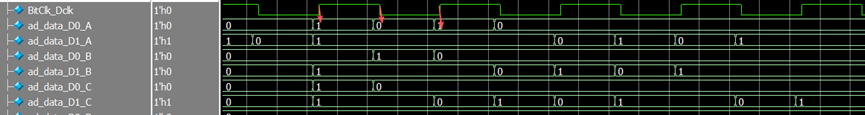

下面看看处理流程中信号时序的变化,这里只看通道0数据,模块中使用BitClk_Dclk采样,单端化后的ad_data_D0_A、ad_data_D1_A,

时间段1:

可以看到,虽然也能采样出正常的正弦波,但是此时的采样点比较危险,十分靠近数据眼边沿,在实际上板过程中,这种采样时刻,采样输出肯定会出错;

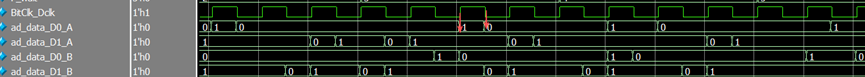

时间段2:

这个时间段,时序在变化,采样点在数据眼上移动变化,

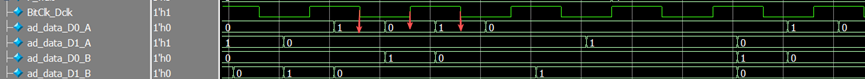

时间段3:

可以看到,对齐稳定后,采样时钟边沿对齐到数据眼中心,采样时钟恢复到输入端点处的最佳采样点附近了;

本文章由威三学社出品

对课程感兴趣可以私信联系