要闻概览

- FPGA催眠术漏洞 "Chynopsis"

研究人员通过欠压 (undervolting) 的方式,使 FPGA 进入一种"受控睡眠"状态,而安全机制未能察觉,从而可能泄露存储的数据(如密钥等)。这一漏洞在 OpenTitan 的 FPGA 实例上已被验证。

- IBM 在 AMD FPGA 上跑量子纠错算法,比需求快 10 倍

IBM 的团队使用标准 AMD FPGA 实现了一种量子纠错算法(疑为 Relay-BP / LDPC 类型),实现速度大幅超出原计划。这推动其 Starling 项目取得进展,并可能提前部署时间。

- Lattice 推出 MachXO5-NX TDQ 系列 FPGA,支持后量子密码算法

Lattice 宣布其 MachXO5-NX TDQ 芯片具备 全套 CNSA 2.0 / NIST 批准的后量子密码算法 支持(如 LMS、XMSS、ML-KEM/DSA、AES256-GCM 等)。这类 "PQC-ready 安全控制 FPGA" 被定位为面向量子攻击时代的安全器件。

- SEGGER 推出 Flasher BitStreamer,使其 Flasher 系列编程器支持 FPGA 编程

SEGGER 的 Flasher 设备(之前用于编程 MCU / 闪存等)通过新增 BitStreamer 功能,现在也能对 FPGA / CPLD 进行 bitstream 配置(通过 SVF / STAPL 格式),简化了嵌入式系统中 FPGA 的编程流程。

- AMD Spartan™ UltraScale+™ SCU35 Tile 相关内容发布

围绕AMD Spartan UltraScale+ SCU35 开发板构建 "Tile 模块 / 硬件模块设计" 的硬件说明文章。

研究人员发现FPGA芯片中存在新的安全漏洞

🧠 FPGA"催眠术":研究人员发现可绕过安全机制的新漏洞

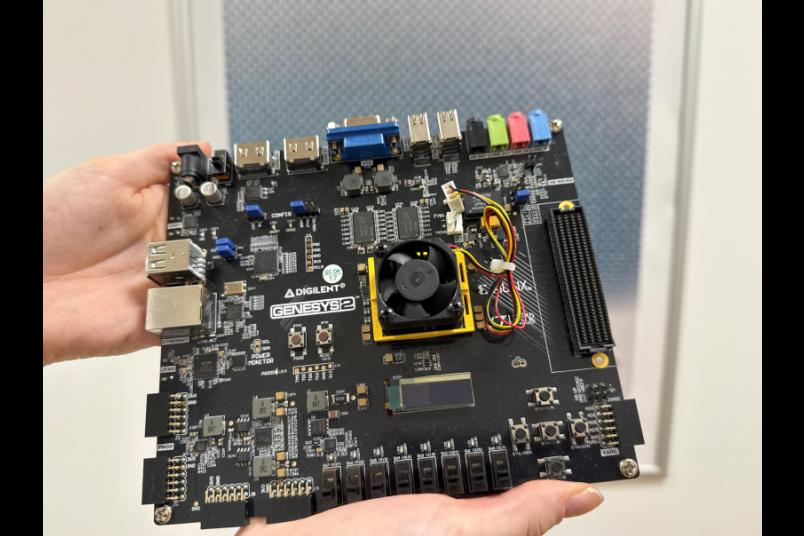

在我们这个日益数字化的世界中,硬件安全正在成为新的攻防焦点。除了传统处理器外,可编程逻辑器件 FPGA(Field Programmable Gate Array)如今被广泛应用于 5G 通信、汽车电子以及加密安全处理 等关键领域。而最近,一项来自 德国波鸿鲁尔大学(Ruhr University Bochum) 与 美国伍斯特理工学院(WPI) 的联合研究,再次让 FPGA 的安全性问题被推上风口浪尖。

他们提出了一种名为 "Chynopsis" 的新型攻击方法,能够让 FPGA 芯片进入一种"受控睡眠状态",从而绕过内置的安全防护机制,使敏感数据(包括加密密钥)在未被清除的情况下仍然保留在芯片中。 这项研究成果已于 2025 年 9 月 30 日发布在 ArXiv.org 上,并将于 2026 年 IEEE 安全与隐私研讨会(IEEE S&P) 上正式发表。

⚙️ "催眠"原理:电压瞬降,让芯片睡着但不忘

FPGA 在运行过程中会产生诸如功耗波动、时序抖动等"副信息",这些信息往往是侧信道攻击的突破口。 研究团队发现,通过一种精准的 欠压(Undervolting) 手段,可以在极短时间内降低 FPGA 的供电电压,使芯片的时钟逻辑暂停,而存储的数据依然保留。

研究负责人 Yuval Yarom 教授 将这种状态比喻为"让芯片进入催眠状态"(Chynopsis 一词正是 "chip" + "hypnosis" 的组合)。 由于电压变化太快,芯片内部用于监控的电压/时钟传感器无法及时反应,导致防护机制(如 Alert Handler)无法启动。

在这段"睡眠窗口"内,攻击者可以利用 激光逻辑态成像(LLSI) 或 电阻抗分析 等技术,提取芯片上仍留存的加密密钥等敏感数据。

🔓 攻击验证与防御建议

研究人员在基于 OpenTitan 的 FPGA 实现上验证了该攻击,并成功绕过了安全响应模块 Alert Handler。 漏洞已通过"负责任披露"流程报告给两家主要 FPGA 厂商:AMD(原 Xilinx) 和 Microchip。 同时,研究团队也提出并验证了改进方案,旨在提升现有和未来 FPGA 的安全韧性。

论文链接(可直接下载)

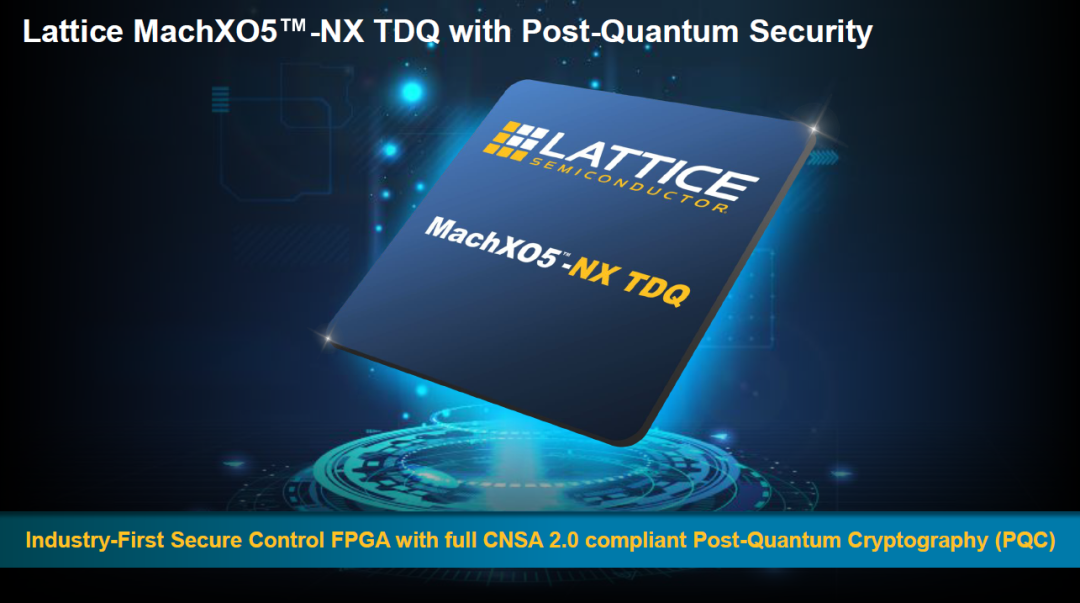

Lattice 推出全球首款「后量子密码」安全控制 FPGA:MachXO5-NX TDQ 家族

在量子计算的阴影下,传统加密算法的"寿命"正在被倒计时。 而 Lattice Semiconductor(莱迪思半导体) 率先给出了硬件级的答案------推出全球首款支持后量子密码(PQC) 的安全控制 FPGA:MachXO5-NX TDQ 系列。

这也是业界首款完全符合 CNSA 2.0 标准 的安全控制 FPGA,为未来十年的加密安全树立了新标杆。

🔐 面向后量子时代的安全防线

量子计算带来的强大算力,可能在短时间内破解现有的公钥体系(如RSA、ECC)。

Lattice 的 MachXO5-NX TDQ FPGA 就是为此而生------它不仅是"安全的FPGA",更是为量子威胁做好准备的FPGA。

该系列基于 Lattice Nexus 平台,专为计算、通信、工业控制与汽车电子等高安全场景设计。

Lattice 官方称其为:

"业界首款支持 CNSA 2.0 与 NIST 后量子算法的完整安全控制 FPGA。"

🧮 支持多种后量子算法

MachXO5-NX TDQ 内置的算法支持极其丰富,覆盖了所有 NIST 批准或推荐的 PQC 方案,包括:

基于哈希的签名算法:LMS、XMSS

基于格的签名与密钥交换算法:ML-DSA、ML-KEM

经典加密算法:AES256-GCM、SHA2、SHA3、SHAKE

配合 加密/认证的 Bitstream 机制,可以有效防止未经授权的访问与篡改。

其内建的反回滚保护与算法更新能力(Crypto-Agility)确保设备在标准演进时仍能持续安全运行。

🧱 硬件级 Root of Trust(信任根)

MachXO5-NX TDQ 不仅仅是"能加密"的FPGA,它在硬件层面构建了完整的信任体系:

✅ 单芯片可信启动(Trusted Boot)

✅ 唯一设备密钥(Unique Device Secret)

✅ 内置安全闪存与用户区加密隔离

✅ SPI/JTAG 接口锁定与抗旁路攻击设计

✅ 支持 NIST CAVP 认证的算法集

同时,搭配 Lattice 自家的 SupplyGuard 供应链保护机制,可在生产、分发、部署全生命周期内验证器件身份,防止供应链攻击。

💡 延展:安全控制 FPGA 的新方向

MachXO 系列一向以"控制与安全"见长,而 TDQ 系列的发布,标志着 FPGA 正在从**"可编程逻辑"走向"可编程信任"**。

FPGA 不仅仅是算力的提供者,更成为了:

🔒 "安全系统的核心信任锚点(Root of Trust)。"

这也意味着未来,FPGA 将在数据中心安全启动、AI 加密推理、汽车安全网关等领域发挥更关键的作用。

新闻来源:

https://www.edn.com/lattice-sets-new-standard-for-secure-control-fpgas/

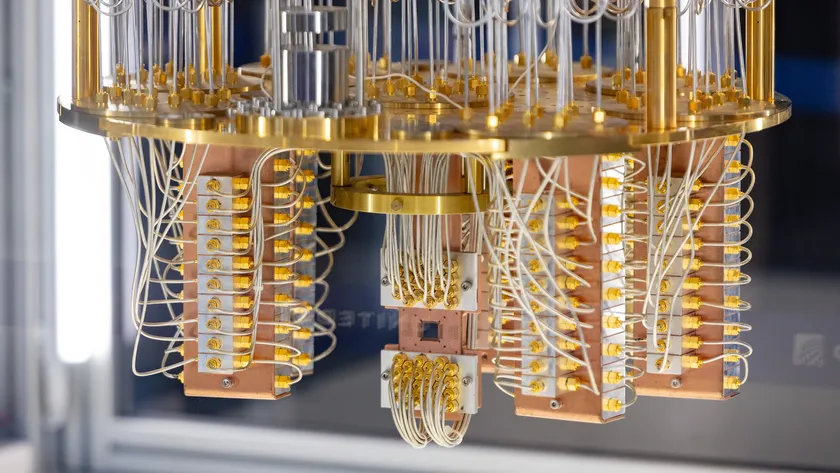

IBM 用 AMD FPGA 跑量子纠错,比预期快 10 倍!Starling 计划再加速

在量子计算的世界里,"算得准" 比 "算得快" 更重要。 最近,IBM 的研究团队用一块 标准 AMD FPGA 芯片,跑出了一个震撼业界的结果------他们成功实现了量子纠错算法的实时运行,速度竟然快了 10 倍。

这项突破性的研究,将为 IBM 的 Starling 大规模量子计算机项目 提前一年打开新篇章。

🧩 FPGA 加持的量子"稳态"

量子计算机的最大难题之一,是结果的精确性。 量子比特(Qubit)可以同时表示 0 和 1,这种并行特性虽然赋予了惊人的计算能力,但也意味着它极其脆弱------一丁点环境噪声都可能导致计算结果失真。

这正是 量子纠错算法(Quantum Error Correction, QEC) 的用武之地。

IBM 的团队选择了一条不同寻常的路径:他们没有依赖昂贵的专用量子硬件,而是在 AMD 的标准 FPGA 上,实现了一个可重构、实时的量子纠错引擎。

FPGA(现场可编程门阵列)以可重构、并行处理著称,非常适合高效运行这类纠错算法。

⚙️ Relay-BP:更快、更准的量子纠错核心

IBM 团队使用的正是此前在 6 月份论文中首次提出的 Relay-BP(Relay Belief Propagation)算法。 该算法基于 LDPC(低密度奇偶校验)码 架构,被 IBM 称为目前"最灵活、最紧凑、同时也是最快、最精确的量子纠错算法"。

通过 FPGA 并行逻辑的硬件加速,IBM 团队实现了:

✅ 实时运行量子纠错(无延迟反馈)

⚡ 性能超出算法需求的 10 倍

🔒 能在标准 AMD FPGA 上稳定运行

IBM 研究负责人 Jay Gambetta 博士 表示,该算法的硬件实现"比原计划提前一年完成",这也意味着 Starling 量子计算项目 的进展将被大幅提前。

🚀 量子计算的"可编程化"未来

从 Google 到 IBM,再到国内外的科研团队,FPGA 正逐渐成为量子计算实验平台的关键角色。

它们在纯量子芯片尚未完全成熟的阶段,为算法验证和逻辑优化提供了强大的"过渡载体"。

FPGA 的可编程特性,使得研究者可以:

模拟量子态演化;

实现经典与量子混合控制;

验证不同量子纠错架构的可行性。

这意味着未来,我们可能在一块 FPGA 上先"演练"一台量子计算机,再将成果迁移到真正的量子硬件中。

新闻来源

SEGGER 推出 Flasher BitStreamer:让一台编程器搞定 MCU + FPGA!

近日,SEGGER 宣布推出全新的嵌入式软件解决方案 ------ Flasher BitStreamer,为其 Flasher 系列在线系统编程器(ISP)带来了 FPGA 与 CPLD 编程能力。

这意味着,从此 SEGGER 的 Flasher 不仅能烧录 MCU 和 SPI Flash,还能直接给 FPGA 下载 bitstream!

🚀 一站式编程,无需多套工具

过去,FPGA 配置通常需要使用独立的编程工具(如 Vivado、Quartus Programmer 等),操作复杂、设备分散。 而 Flasher BitStreamer 通过内置软件,将整个流程统一在一台 Flasher 上完成。

它可以将 SVF(Serial Vector Format) 或 STAPL(Standard Test and Programming Language) 文件转换成自包含的可执行包, 用户只需将其拷贝到 Flasher 上,或者导出为可直接使用的 ZIP 包,就能在数秒内完成烧录。

🧩 支持广泛,无额外授权费用

BitStreamer 支持所有 SEGGER Flasher 型号, 并兼容所有支持 JTAG 编程(SVF/STAPL 文件格式)的 FPGA 与 CPLD, 无任何后续授权费或订阅费用。

SEGGER 技术市场负责人 Dirk Akemann 表示:

"Flasher BitStreamer 让 FPGA 的系统内编程变得更简单。现在,我们的 Flasher 真正成为通用的嵌入式编程解决方案,一台设备即可搞定 SoC、MCU、外部 Flash,甚至 FPGA。"

🔌 Flasher 家族简介

SEGGER Flasher 系列是广泛应用于:

-

生产测试环境

-

原型烧录

-

大批量编程的专业 ISP 工具

它支持对 MCU/SoC 内部非易失存储器、外部 SPI/QSPI Flash 及 其他类型存储器 进行烧录, 并提供高度灵活的目标接口: 支持 JTAG、SWD、(Q)SPI、I²C、UART 等多种协议, 同时可扩展至自定义通信接口。

Flasher 附带的控制与配置软件可在 Linux、macOS、Windows 上运行, SEGGER 还承诺软件与固件更新 永久免费,用户可在不同芯片型号间自由切换,无需额外费用。

新闻来源

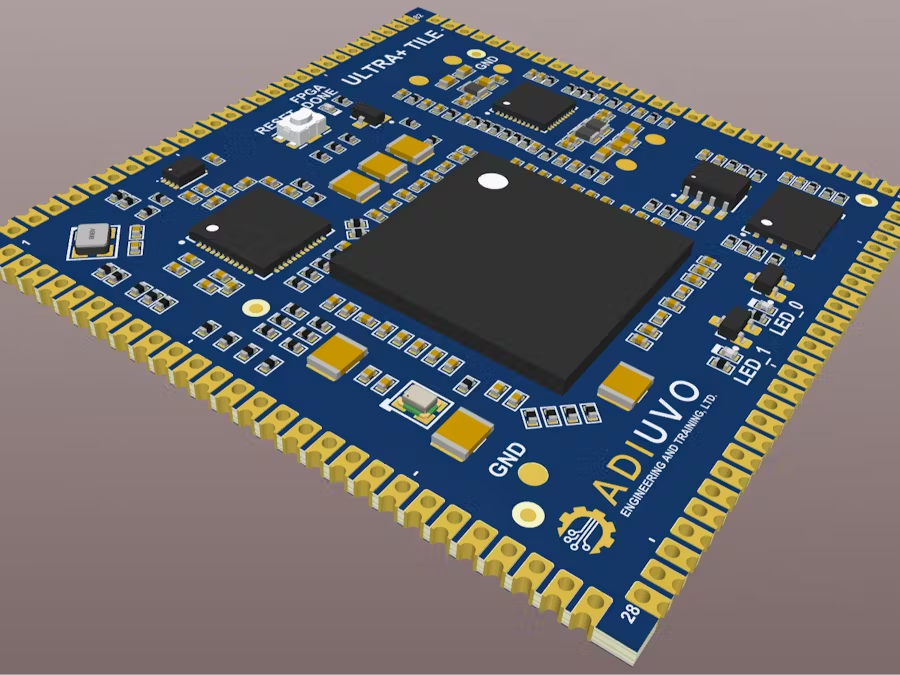

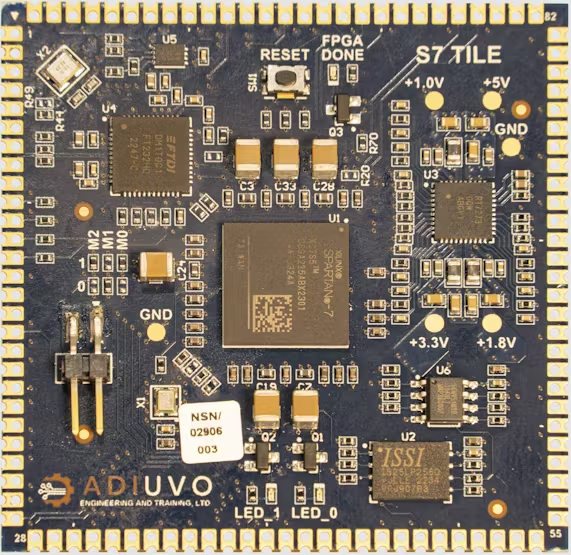

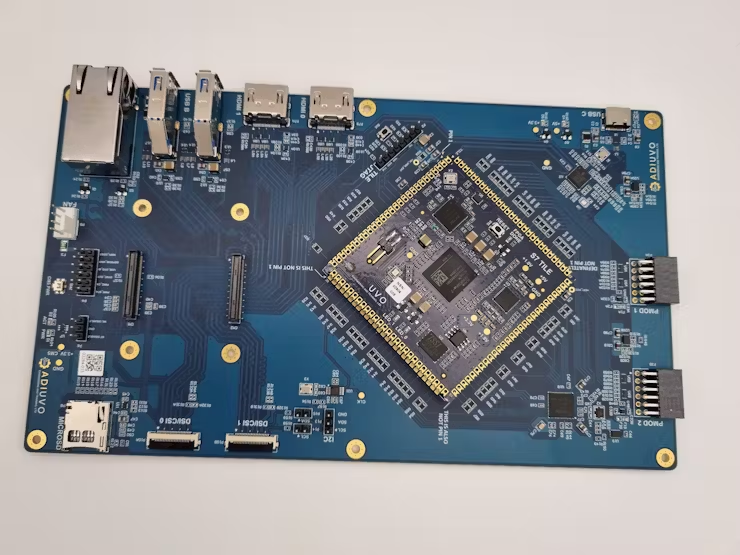

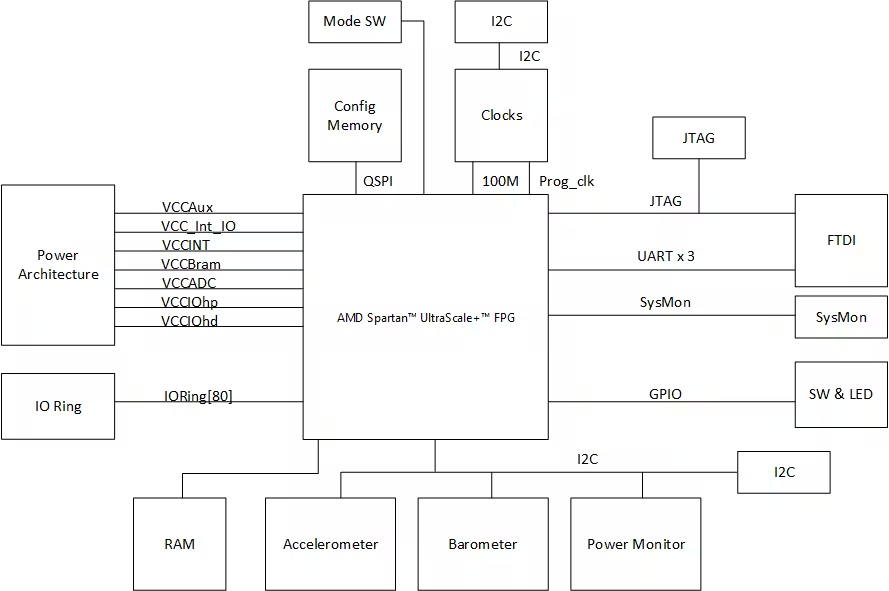

AMD Spartan™ UltraScale+™ SCU35邮票孔核心板

Adam Taylor大神继去年推出开源AMD Spartan™ 7 FPGA 邮票孔核心板和底板后(链接在后面)今年又开始了Spartan™ UltraScale+™ 核心板设计:

目前大神放出来核心参数计算步骤,适合硬件及相关人员参考,包括电源等设计。

AMD Spartan™ 7 FPGA 相关链接

https://www.hackster.io/adam-taylor/amd-spartan-7-fpga-stamp-design-ee03ab

https://www.hackster.io/adam-taylor/amd-spartan-7-fpga-stamp-design-ee03ab

https://www.hackster.io/adam-taylor/raspberry-pi-based-fpga-test-system-part-one-410854

AMD Spartan™ UltraScale+™ FPGA相关链接

https://www.hackster.io/adam-taylor/creating-an-amd-spartan-ultrascale-scu35-tile-dfdee1

https://www.hackster.io/adam-taylor/creating-an-amd-spartan-ultrascale-scu35-tile-dfdee1