相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

有一类信号由于其自身高扇出的特性,需要使用树形结构来满足其DRC/时序约束的要求,比如时钟(复位、扫描使能等),本文就将讨论时钟树在综合时的特性。

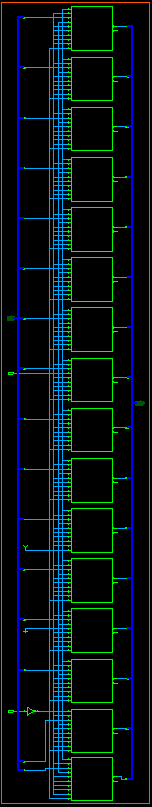

由于综合工具不进行时钟树综合(Clock Tree Synthesis, CTS),在使用物理实现工具进行时钟树综合前,设计中所有的时钟都是理想时钟,其时钟偏移、时钟抖动、时钟延迟、时钟转换时间由set_clock_uncertainty、set_clock_latency、set_clock_transition命令直接设置,与触发器时钟引脚直接相连的时钟路径上的DRC约束不会被检查,下面展示了一个简单的例子。

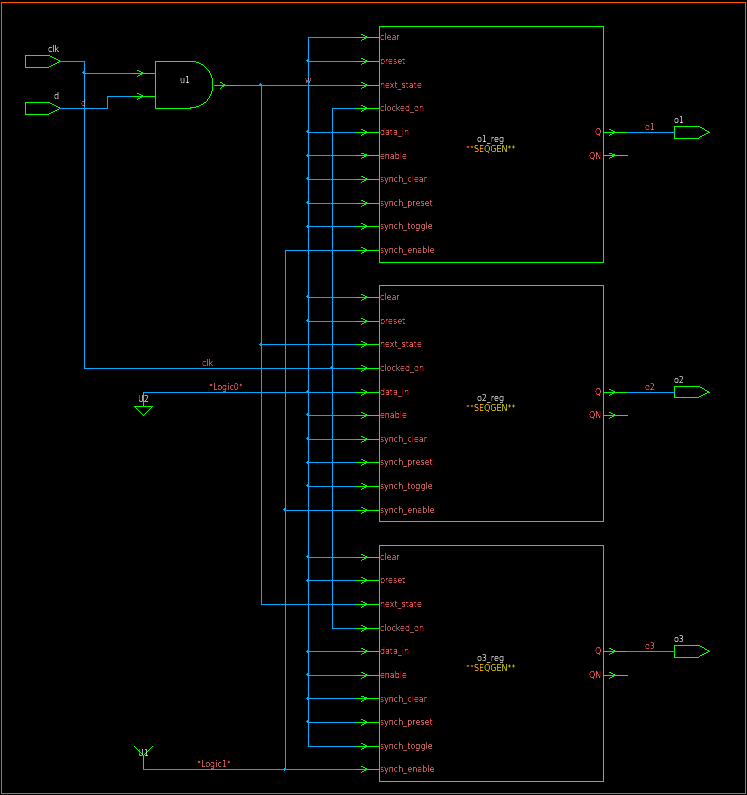

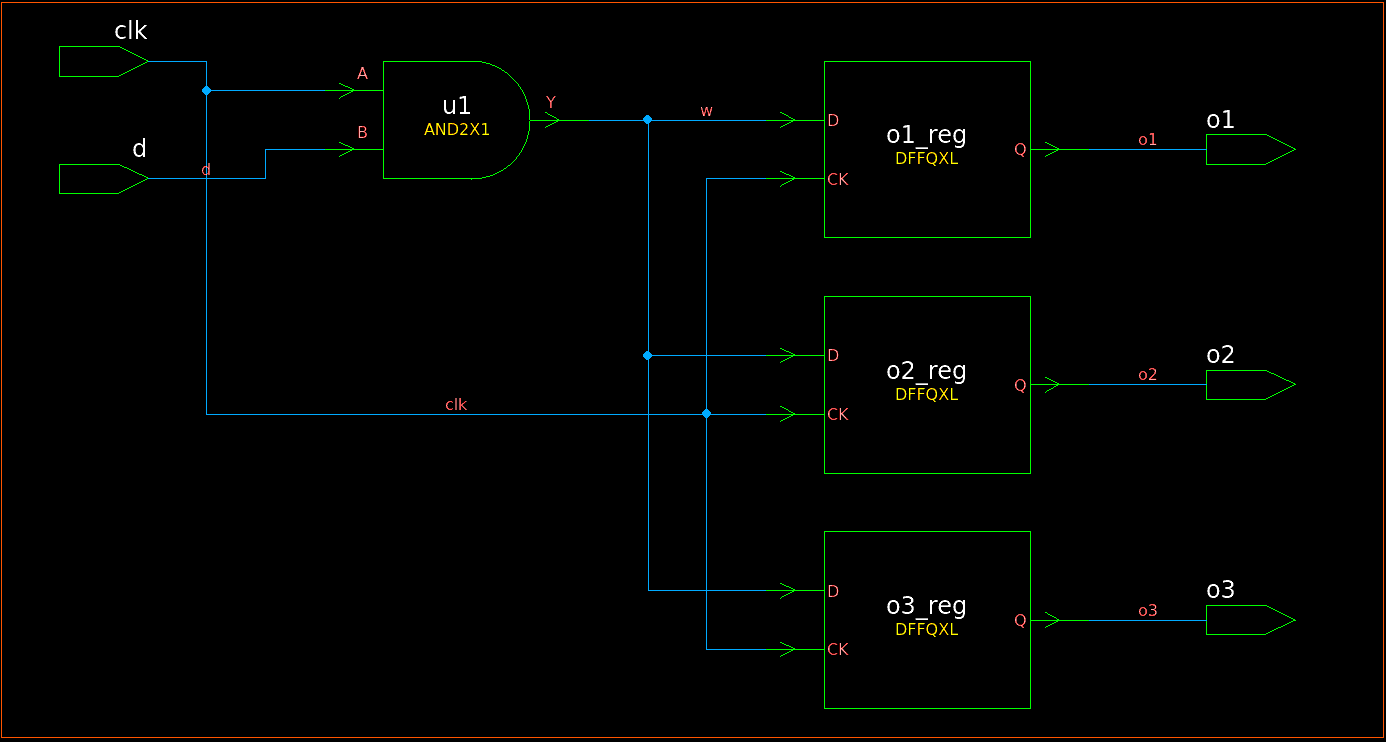

图1 简单的例子(综合前)

dc_shell> set_max_capacitance 0.0000001 [get_ports clk]

dc_shell> create_clock -period 10 [get_ports clk] // 必须定义时钟,否则无法识别时钟路径

dc_shell> compile

dc_shell> report_net [get_nets clk]

****************************************

Report : net

Design : dff

Version: W-2024.09-SP2

Date : Thu Nov 6 16:46:58 2025

****************************************

Operating Conditions: fast Library: fast

Wire Load Model Mode: top

Attributes:

dr - drc disabled

Net Fanout Fanin Load Resistance Pins Attributes

--------------------------------------------------------------------------------

clk 16 1 0.03 0.00 17 dr

--------------------------------------------------------------------------------

Total 1 nets 16 1 0.03 0.00 17

Maximum 16 1 0.03 0.00 17

Average 16.00 1.00 0.03 0.00 17.00

dc_shell> report_constraint -max_capacitance

****************************************

Report : constraint

-max_capacitance

Design : dff

Version: W-2024.09-SP2

Date : Thu Nov 6 16:44:19 2025

****************************************

Constraint Cost

-----------------------------------------------------

max_capacitance 0.00 (MET)

图2 简单的例子(综合后)

从上面的例子中可以看出,即使线网clk不满足DRC约束的要求,综合工具在综合时也并没有插入缓冲器来进行修复,代价函数中也并没有包含DRC违例。

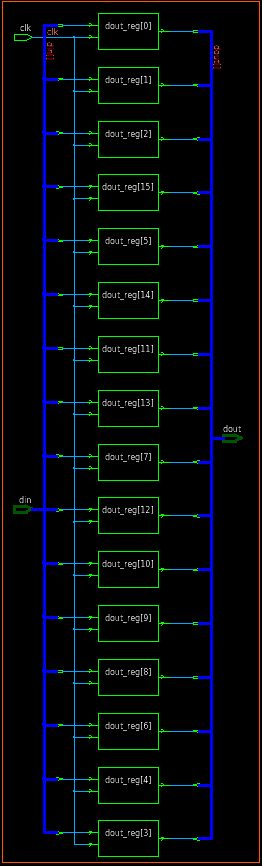

但是在某些情况下,综合工具还是会在时钟路径上插入缓冲器,对于那些与触发器时钟引脚不直接相连的时钟路径就是如此,如图3所示。

图3 时钟路径上的DRC修复

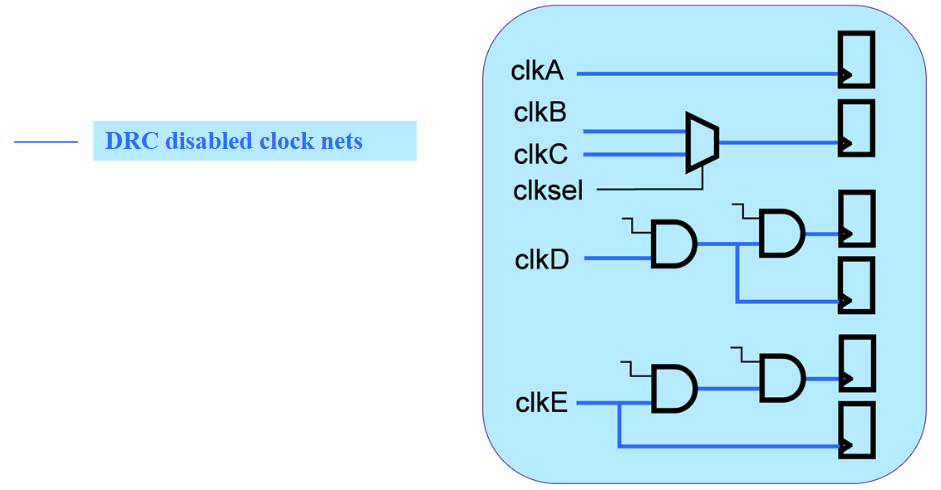

在这种情况下,推荐使用set_auto_disable_drc_nets -on_clock_network true命令进行设置,这样整个时钟路径都会被禁止DRC约束检查,如图4所示。

图4 禁止整个时钟路径上的DRC约束检查

除了set_auto_disable_drc_nets命令之外,还有两个命令可以用来禁止缓冲器插入,但它们或多或少存在一些问题,下面将分别讨论。

set_dont_touch_network

有关set_dont_touch_network命令的详细介绍,可见下面这篇博客。

SDC命令详解:使用set_dont_touch_network命令进行约束![]() https://blog.csdn.net/weixin_45791458/article/details/154078168?spm=1001.2014.3001.5501 set_dont_touch_network命令可以将当前设计中的一组端口、引脚或时钟标记为dont_touch网络源(设置端口、引脚或时钟对象的dont_touch_network属性为true),且dont_touch属性会沿着组合逻辑进行传播,这会阻止对整个时钟路径进行逻辑的添加、删除或尺寸调整,从而禁止缓冲器插入。

https://blog.csdn.net/weixin_45791458/article/details/154078168?spm=1001.2014.3001.5501 set_dont_touch_network命令可以将当前设计中的一组端口、引脚或时钟标记为dont_touch网络源(设置端口、引脚或时钟对象的dont_touch_network属性为true),且dont_touch属性会沿着组合逻辑进行传播,这会阻止对整个时钟路径进行逻辑的添加、删除或尺寸调整,从而禁止缓冲器插入。

但是该命令无法禁止整个时钟路径上的DRC约束检查,因此综合工具会报告出现DRC违例。

该命令还有一些副作用,它可能会影响一些数据路径(在时钟作为数据使用的情况下)的优化,详细介绍可见下面这篇博客。

静态时序分析:时钟标记(作为数据使用的时钟)及其分析方式![]() https://chenzhang.blog.csdn.net/article/details/146268285

https://chenzhang.blog.csdn.net/article/details/146268285

set_ideal_network

有关set_ideal_network命令的详细介绍,可见下面这篇博客。

SDC命令详解:使用set_ideal_network命令进行约束![]() https://blog.csdn.net/weixin_45791458/article/details/146082417?spm=1001.2014.3001.5501 set_ideal_network命令可以将当前设计中的一组端口或引脚标记为理想网络源(设置端口或引脚对象的ideal_network_source属性为true),且在一定情况下,理想属性会沿着组合逻辑进行传播,所有理想网络中的单元和线网都会被设置dont_touch属性,这会阻止对整个时钟路径进行逻辑的添加、删除或尺寸调整,从而禁止缓冲器插入,同时理想网络也会被禁止DRC约束检查。

https://blog.csdn.net/weixin_45791458/article/details/146082417?spm=1001.2014.3001.5501 set_ideal_network命令可以将当前设计中的一组端口或引脚标记为理想网络源(设置端口或引脚对象的ideal_network_source属性为true),且在一定情况下,理想属性会沿着组合逻辑进行传播,所有理想网络中的单元和线网都会被设置dont_touch属性,这会阻止对整个时钟路径进行逻辑的添加、删除或尺寸调整,从而禁止缓冲器插入,同时理想网络也会被禁止DRC约束检查。

与set_dont_touch_network命令类似,该命令的副作用也是可能会影响一些数据路径(在时钟作为数据使用的情况下)的优化。

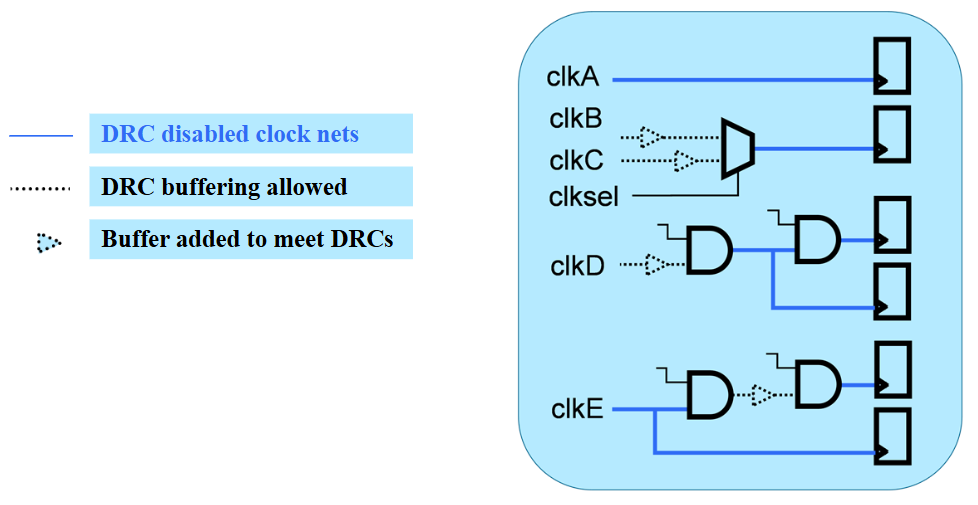

下面针对这个副作用给出一个简单的例子。

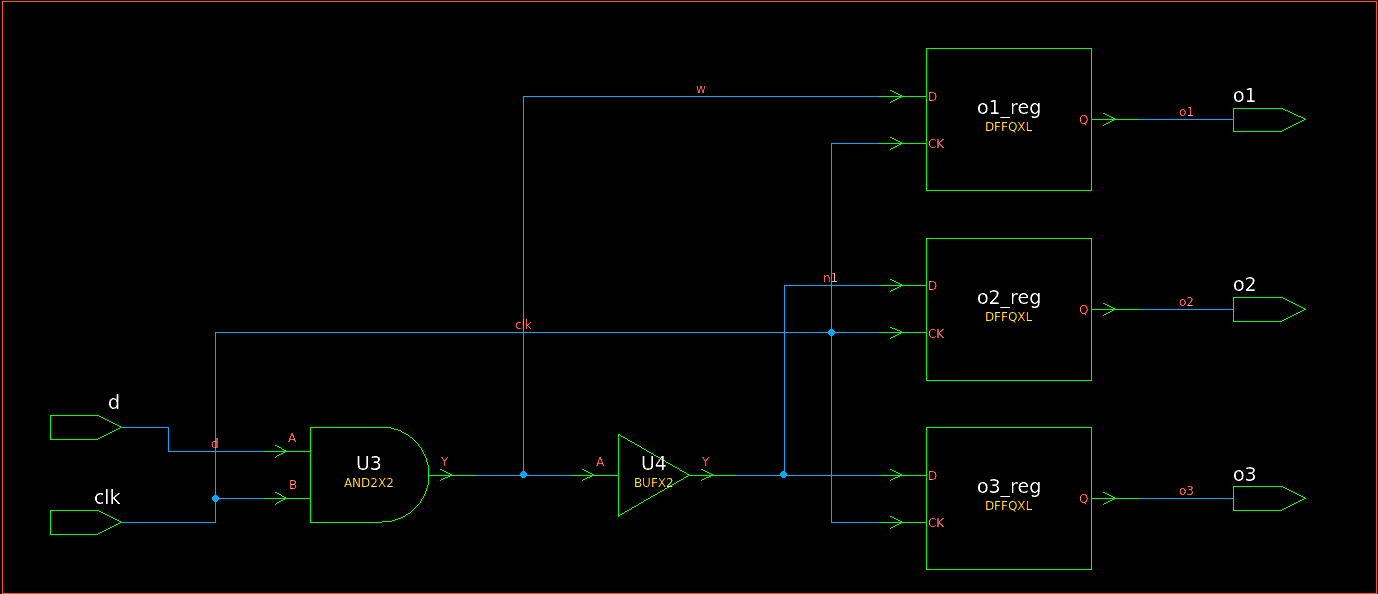

图5 针对副作用的简单例子(综合前)

从上面的例子中可以看出,设计的时钟端口不仅连接到了触发器时钟引脚,还连接到了触发器的数据引脚,因此时钟作为数据使用了。

下面展示了使用set_dont_touch_network命令进行约束的结果,由于数据路径上的扇出过大,综合工具报告出现了DRC违例。

dc_shell> set_max_fanout 2 [current_design]

dc_shell> create_clock -period 10 [get_ports clk] // 必须定义时钟,否则无法识别时钟路径

dc_shell> set_dont_touch_network [get_ports clk]

dc_shell> compile

dc_shell> report_constraint -max_fanout

****************************************

Report : constraint

-max_fanout

Design : simple_register

Version: W-2024.09-SP2

Date : Thu Nov 6 18:53:14 2025

****************************************

Constraint Cost

-----------------------------------------------------

max_fanout 1.00 (VIOLATED)

图6 使用set_dont_touch_network命令约束的综合结果

下面展示了使用set_ideal_network命令进行约束的结果。

dc_shell> set_max_fanout 2 [current_design]

dc_shell> create_clock -period 10 [get_ports clk] // 必须定义时钟,否则无法识别时钟路径

dc_shell> set_ideal_network [get_ports clk]

dc_shell> set_ideal_network [get_ports d] // 为了传播理想属性

dc_shell> compile

dc_shell> report_constraint -max_fanout

****************************************

Report : constraint

-max_fanout

Design : simple_register

Version: W-2024.09-SP2

Date : Thu Nov 6 19:15:12 2025

****************************************

Constraint Cost

-----------------------------------------------------

max_fanout 0.00 (MET)

图7 使用set_ideal_network命令约束的综合结果

下面展示了使用set_auto_disable_drc_nets命令进行约束的结果。

dc_shell> set_max_fanout 2 [current_design]

dc_shell> create_clock -period 10 [get_ports clk] // 必须定义时钟,否则无法识别时钟路径

dc_shell> set_auto_disable_drc_nets -on_clock_network true

dc_shell> compile

dc_shell> report_constraint -max_fanout

图8 使用set_auto_disable_drc_nets命令约束的综合结果