【FPGA+DSP系列】------MATLAB simulink仿真三相桥式全控整流电路

一、理论分析

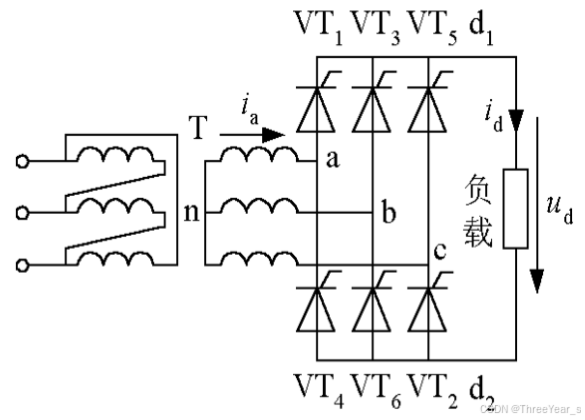

直接上电路图,相比于单相桥式整流的区别,首先是输入变成了3相电压,这个的优势就在于三相相位差都是120°,相比于之前的单相每个周期只有两个触发信号,也只能有2个触发信号,而三相的存在会产生很多换相点,在这些点位生成触发信号会进而提高整流效果以及整流脉冲数,脉波数越多越好,越多就说明纹波越小,越趋近于直线。

导通流程:

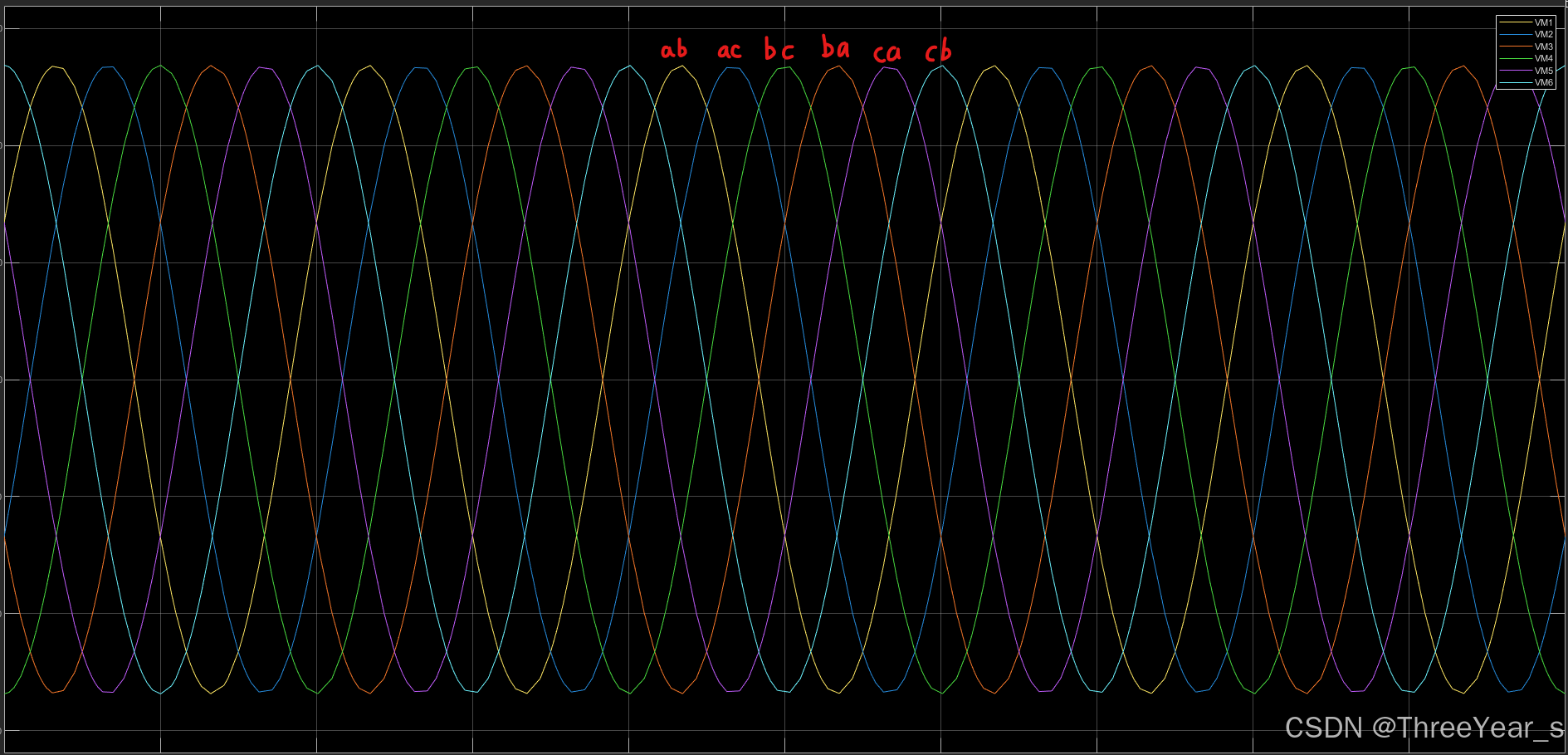

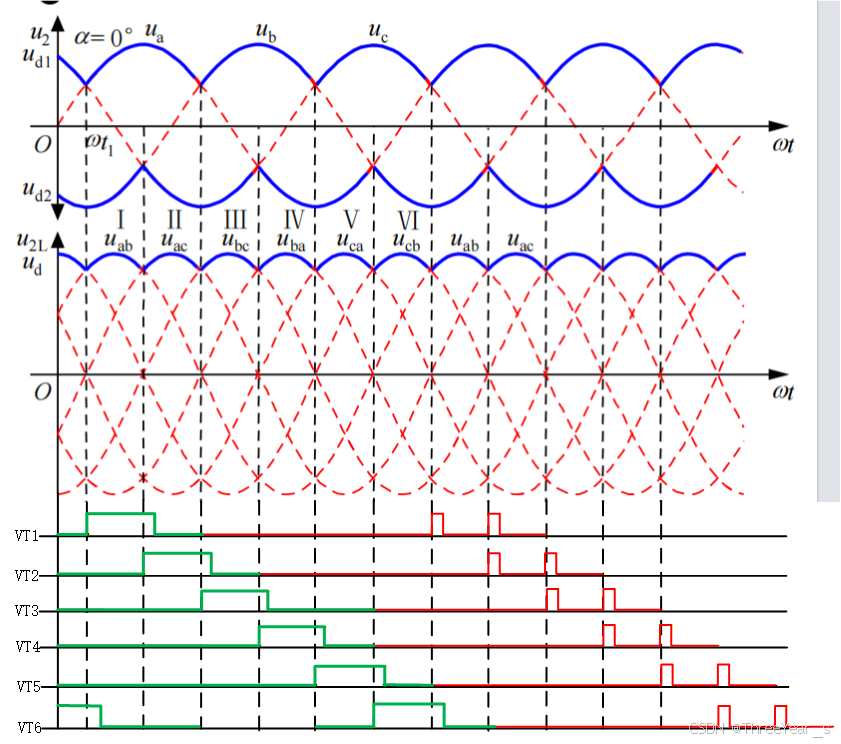

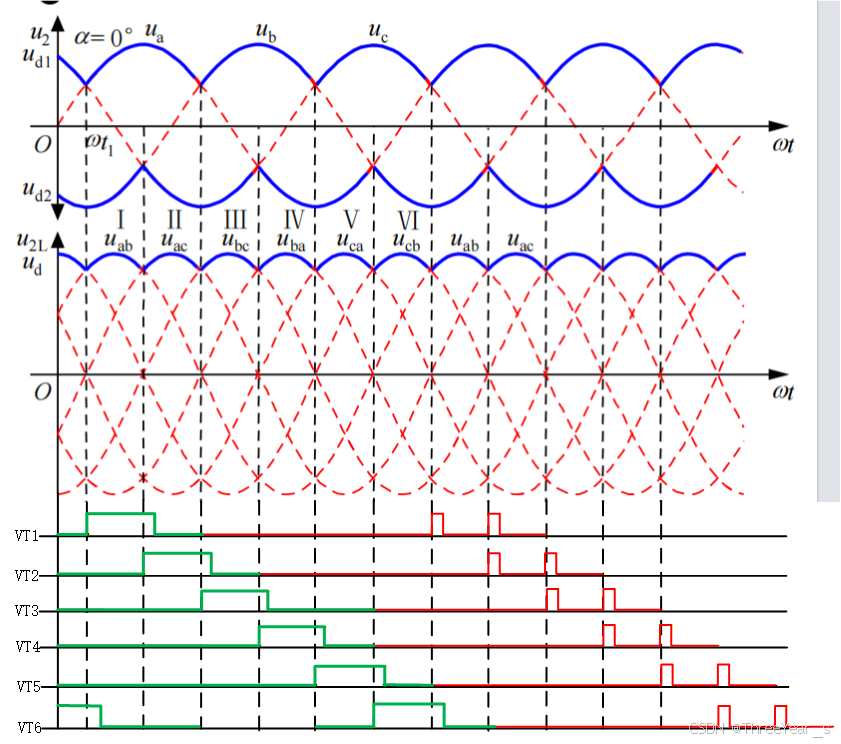

先ab相导通,然后ac相,然后bc相,然后ba相,这个是什么决定的呢?为什么要这样导通,其实有迹可循,当我把Uab/Uac...Uca/Ucb所有的波形放到一起,你就知道为什么要这样触发,为什么是这个顺序了:

这是我将所有的波形放到一个示波器中进行观看, 其中通道顺序与颜色的对应关系如下,这样我们就能标记哪个是哪个了。

通过这个顺序,我们就可以在换相点进行触发,进而完成六脉冲的输出,同时从这个图可以得出我们的导通顺序,ab ac bc ba ca cb。

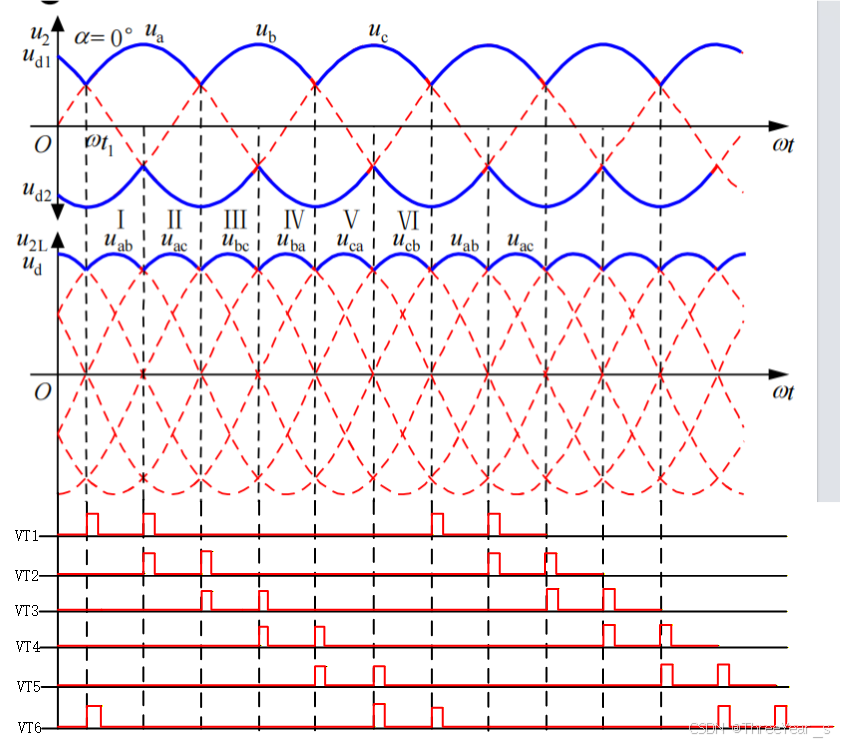

触发流程:

直接画图,每一次导通只能有2个管子,大致顺序如下:

可以发现,其实每一相都有在一个周期内都是触发两次,因此其实我们可以通过一个比较宽的脉冲来覆盖这两个小脉冲,每个宽脉冲之间相差60°,进而就完成了所有晶闸管的触发需求。

修改之后其实就是

二、matlab simulink实验

1.仿真实验

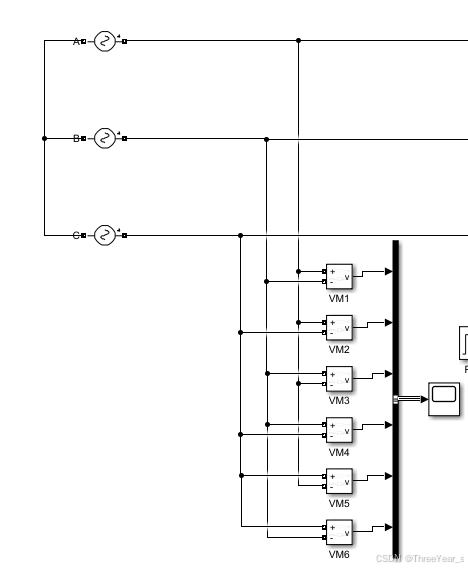

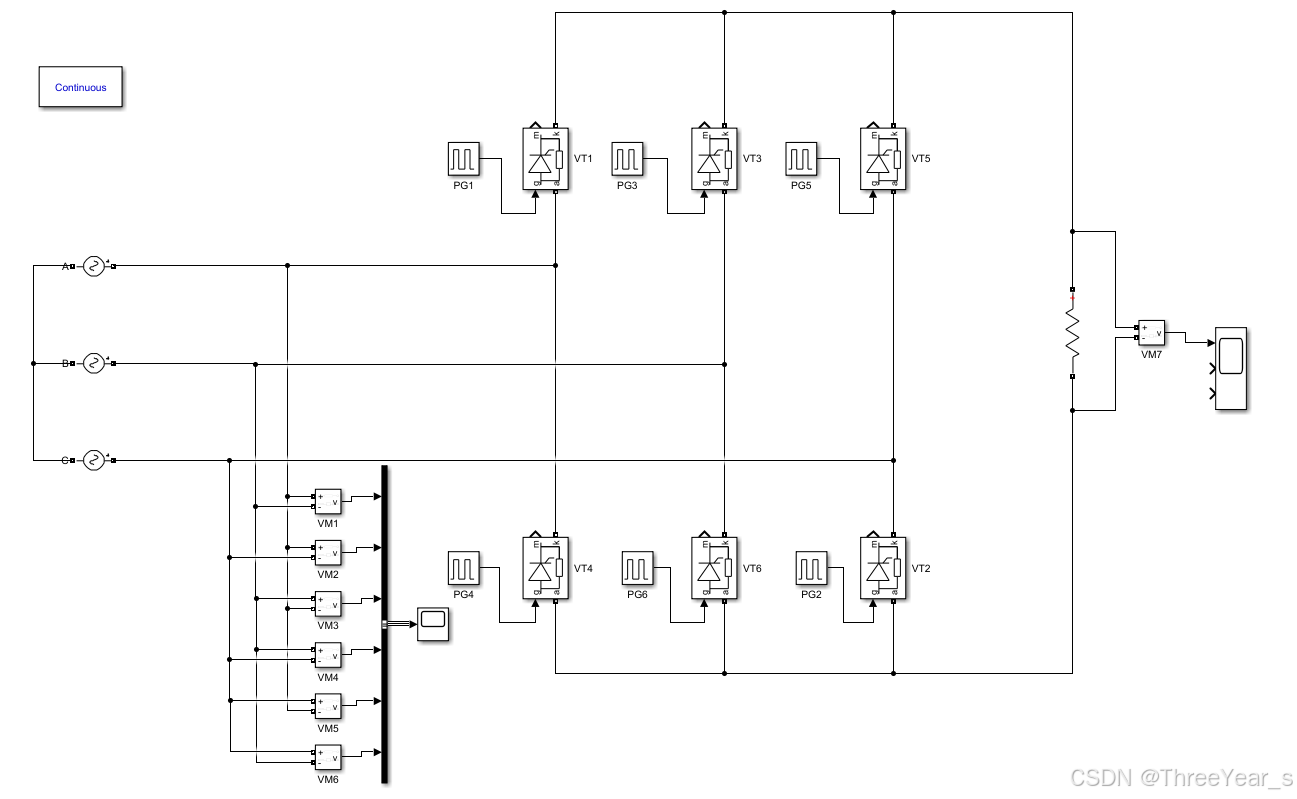

整体框架

咱们对应电路图一部分一部分加

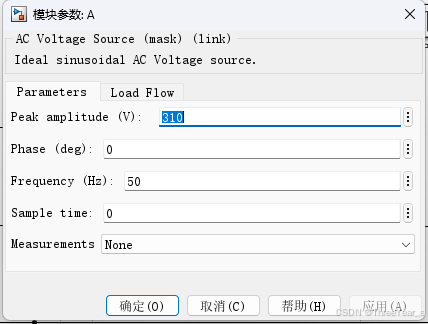

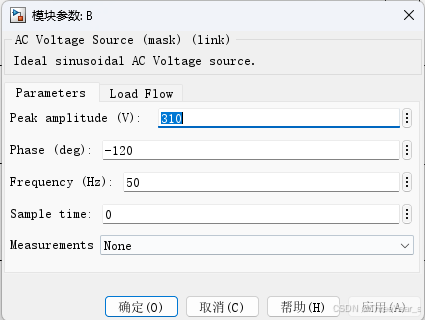

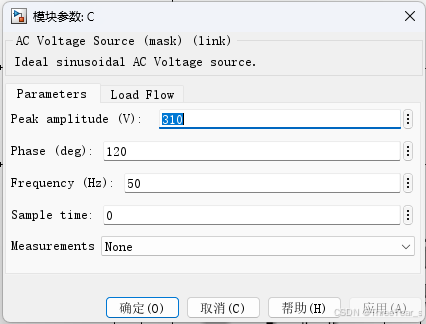

三相电:通过3个交流输出来模拟。ABC相位相差120°,其他都一样。这个相位设置十分关键 ,不然你的管子位置已经决定了你相位设置。

A相设置相位为0:

B相设置相位为-120°

C相设置为120°:

然后就是桥式电路的搭建:

剩下电路不知道怎么搜索的,不知道叫啥的去看我这篇文章:单相桥式整流simulink实验

连起来就行,参数不用修改。

然后就是脉冲信号的设置:

这一部分还是需要啰嗦一下,再看一眼这个图,这个绿色信号就是我们要产生的触发信号。

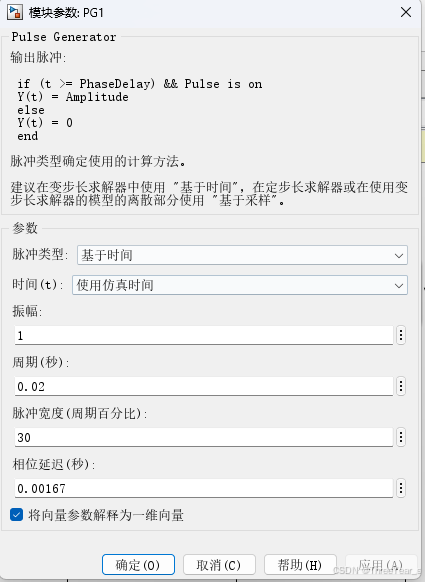

第一周期频率 ,这个毋庸置疑,还是50Hz,也就是0.02s。

第二触发脉冲的宽度 ,由于是仿真,有个5%的触发就能使得晶闸管导通,通过判断图上大致一个周期有六个脉冲也就是100%的宽度,我们触发信号大致是需要持续一个半脉冲的宽度,所以脉冲宽度设置为30%肯定是够够的,你也不能太高,太高的话就会出现同时使得3个管子导通的情况产生。

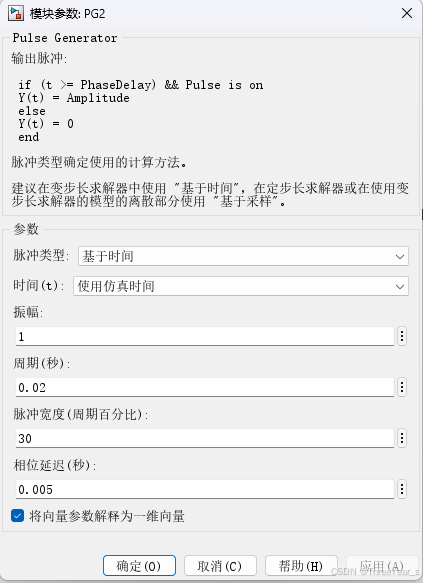

第三就是每个脉冲之间的延迟时间,首先确定的是这六个脉冲每个之间间隔60°,因为总共360°,分成六个脉冲,每一个脉冲占60°。然后就确定第一个脉冲的位置,剩下的逐次增加60°即可。我们看第一个脉冲的位置是30°的时候,但是请注意这个不是触发角,这时候触发角还是0°。所以第一个脉冲延迟为30°,也就是0.00167s。剩下的逐次增加,按照位置顺序增加!

VT1: 0.00167

VT2: 0.005

VT3: 0.00833

VT4: 0.01167

VT5: 0.015

VT6: 0.01833

按照指标依次设置即可。

2.波形分析

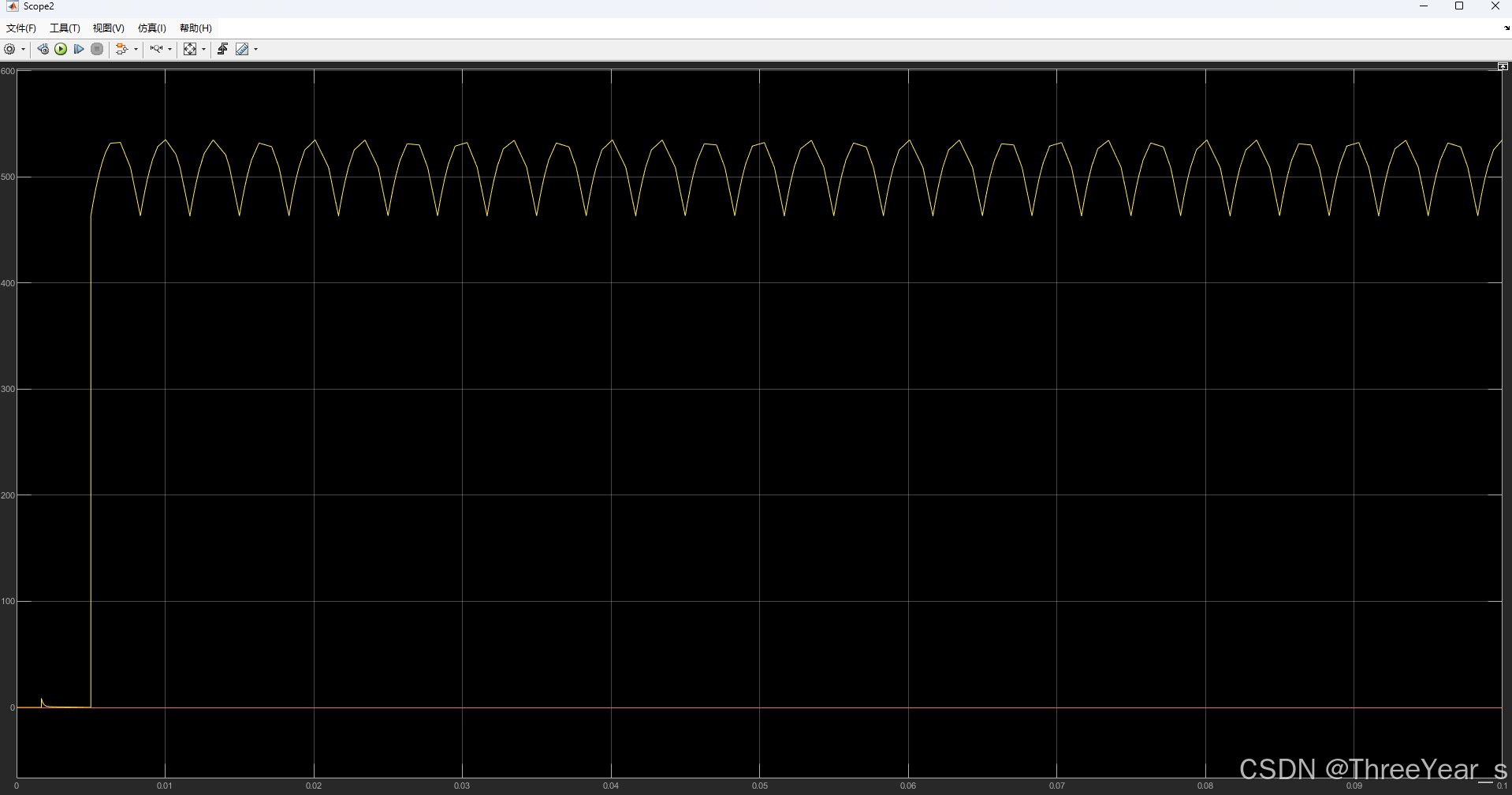

触发角0°

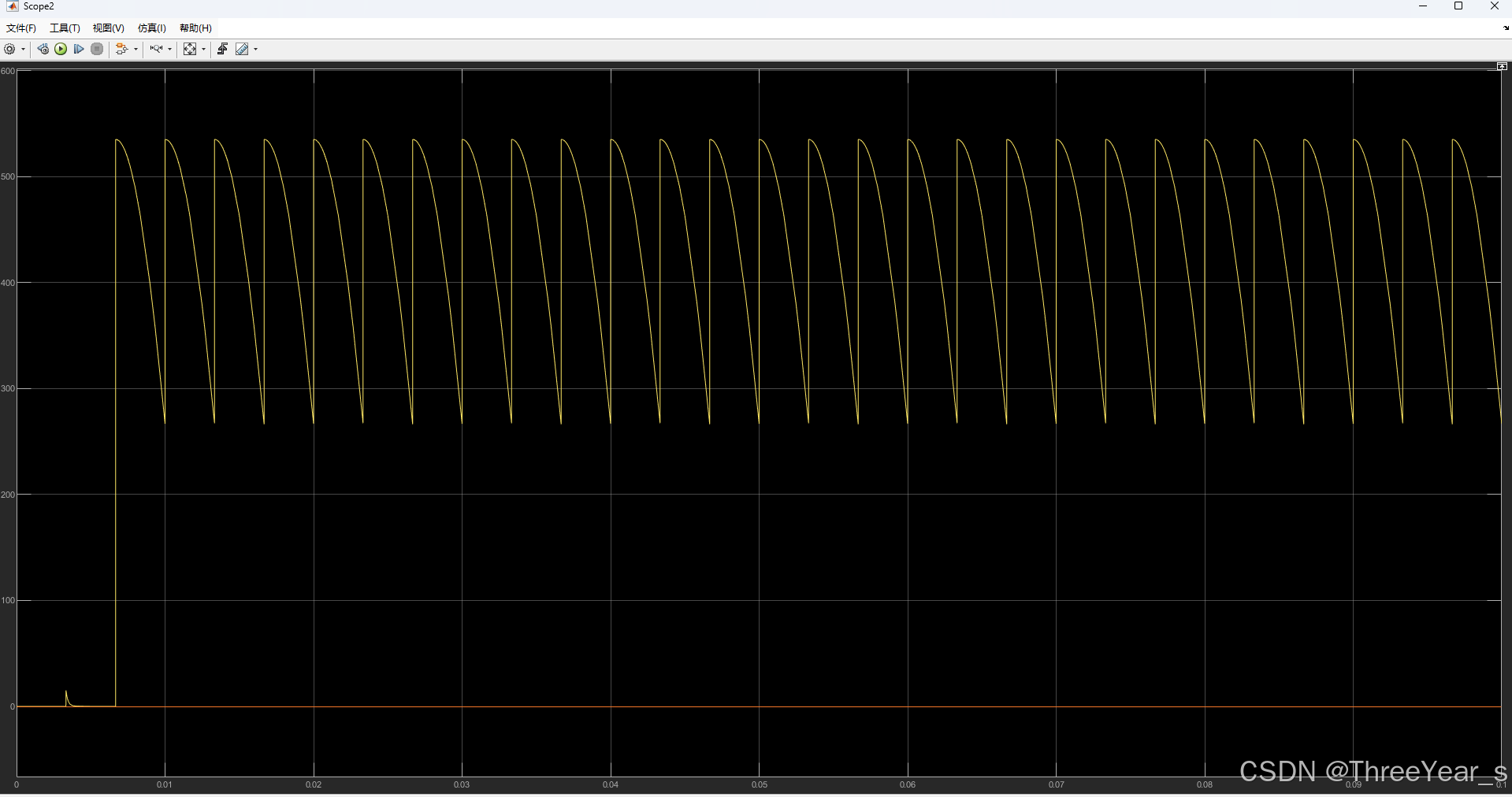

触发角30°

总结

本文介绍了三相桥式全控整流电路的MATLAB/Simulink仿真方法。相比单相整流,三相输入120°相位差提供了更多换相点,通过六脉冲触发可提高整流效果并减小纹波。文章详细分析了导通顺序(ab→ac→bc→ba→ca→cb)及触发脉冲设置要点(50Hz频率、30%脉宽、60°间隔)。在Simulink中搭建了三相电源(相位差120°)和整流桥模型,重点说明了脉冲发生器参数配置方法。仿真结果显示,不同触发角(0°和30°)下的整流波形验证了理论分析的正确性。该仿真为理解三相全控整流电路提供了直观的研究手段。