目录

[3.1 217卷积编码/维特比译码](#3.1 217卷积编码/维特比译码)

[3.2 16QAM映射/逆映射](#3.2 16QAM映射/逆映射)

[3.3 上变频/下变频](#3.3 上变频/下变频)

[3.4 基于PN导频和cordic的频偏锁定](#3.4 基于PN导频和cordic的频偏锁定)

[3.5 基于相关峰的定时点提取](#3.5 基于相关峰的定时点提取)

[3.6 帧同步](#3.6 帧同步)

[3.7 采样判决](#3.7 采样判决)

1.引言

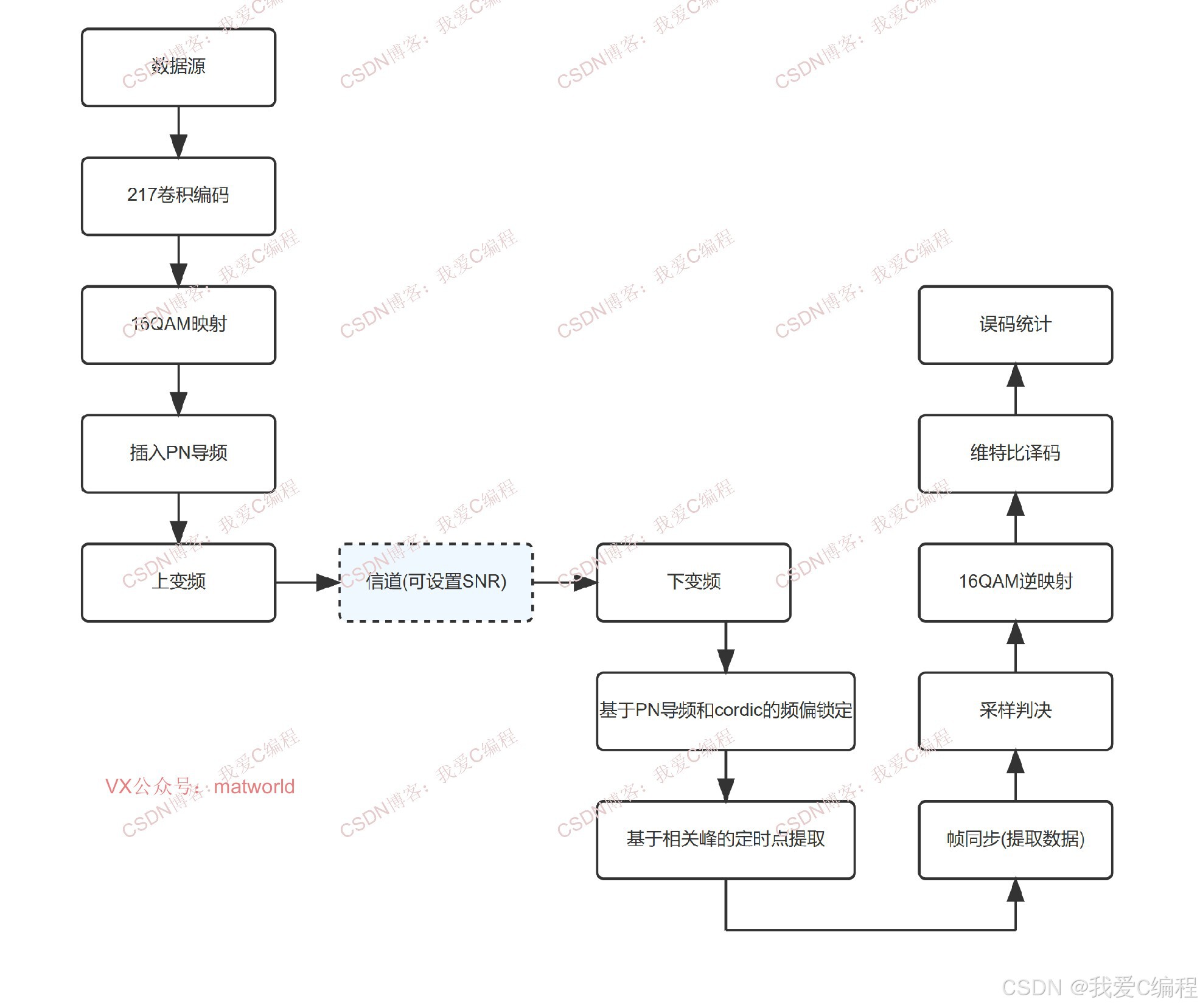

基于FPGA的完整16QAM通信链路实现,含频偏锁定,帧同步,定时点,Viterbi译码,信道,误码统计。系统包括16QAM调制模块,16QAM解调模块,217卷积编码模块,维特比译码模块,AWGN信道模块,误码统计模块,数据源模块,基于PN序列和cordic算法的频偏估计和补偿模块,基于PN相关峰提取的帧同步和定时点提取模块等。

2.算法仿真效果

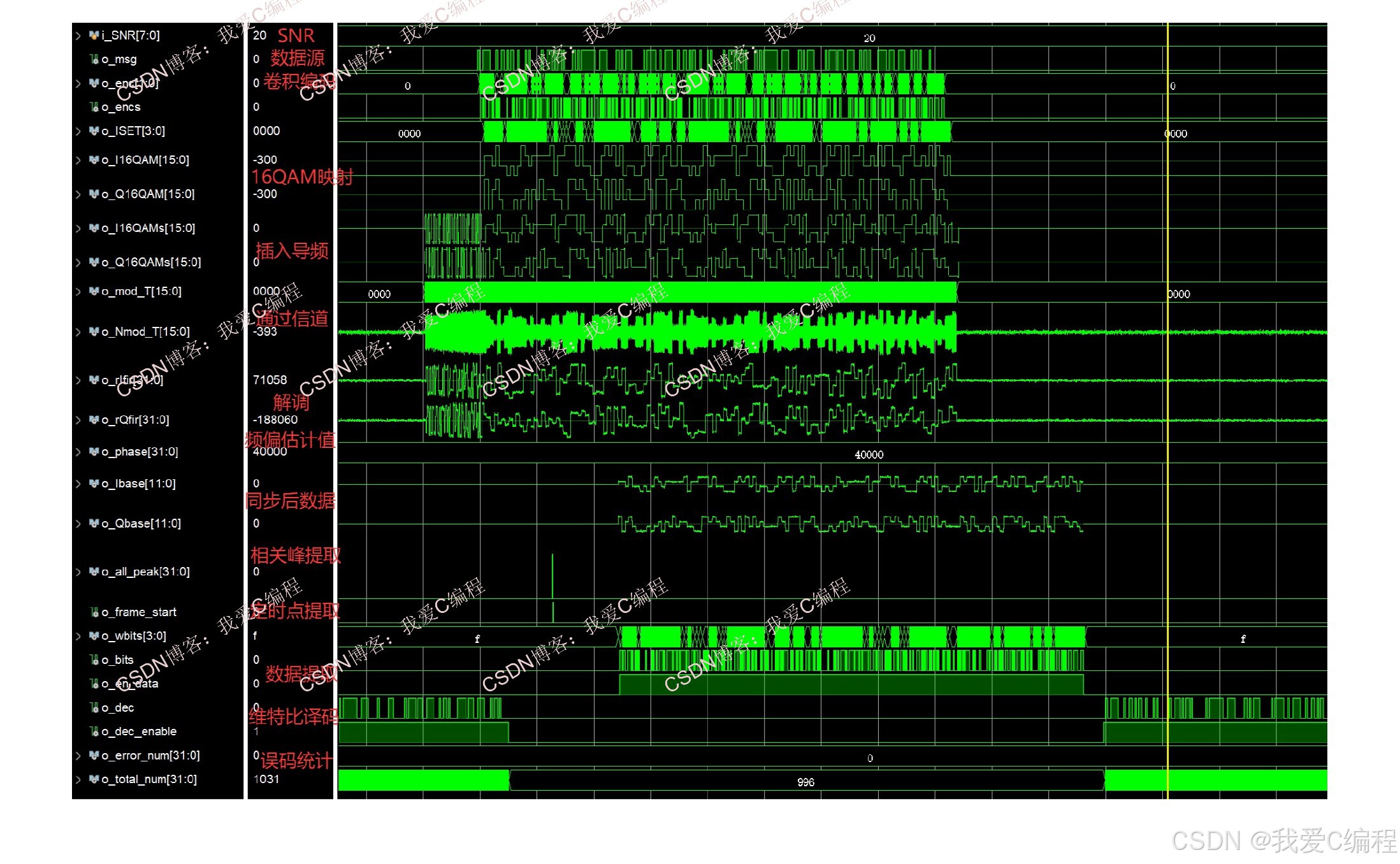

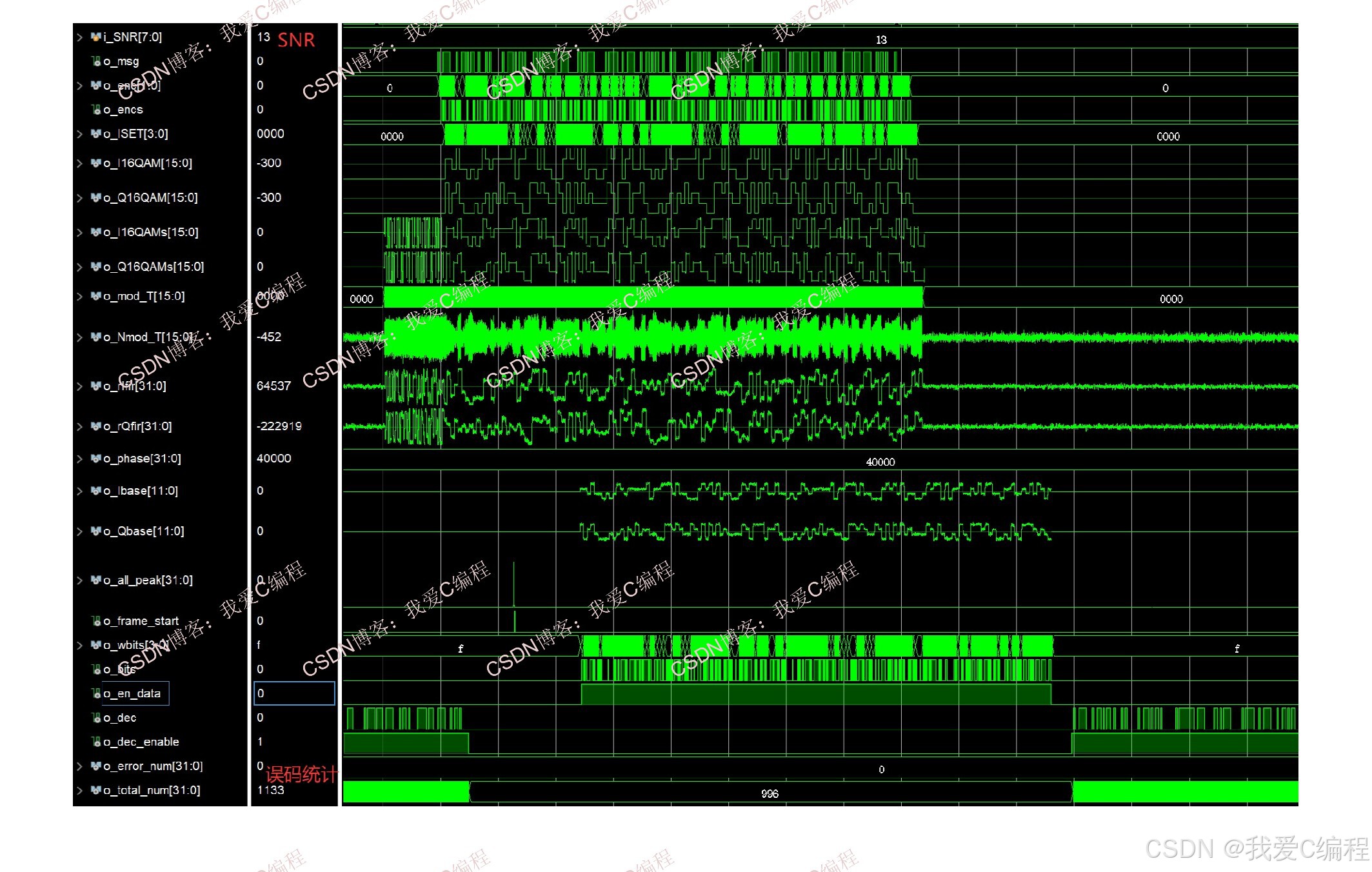

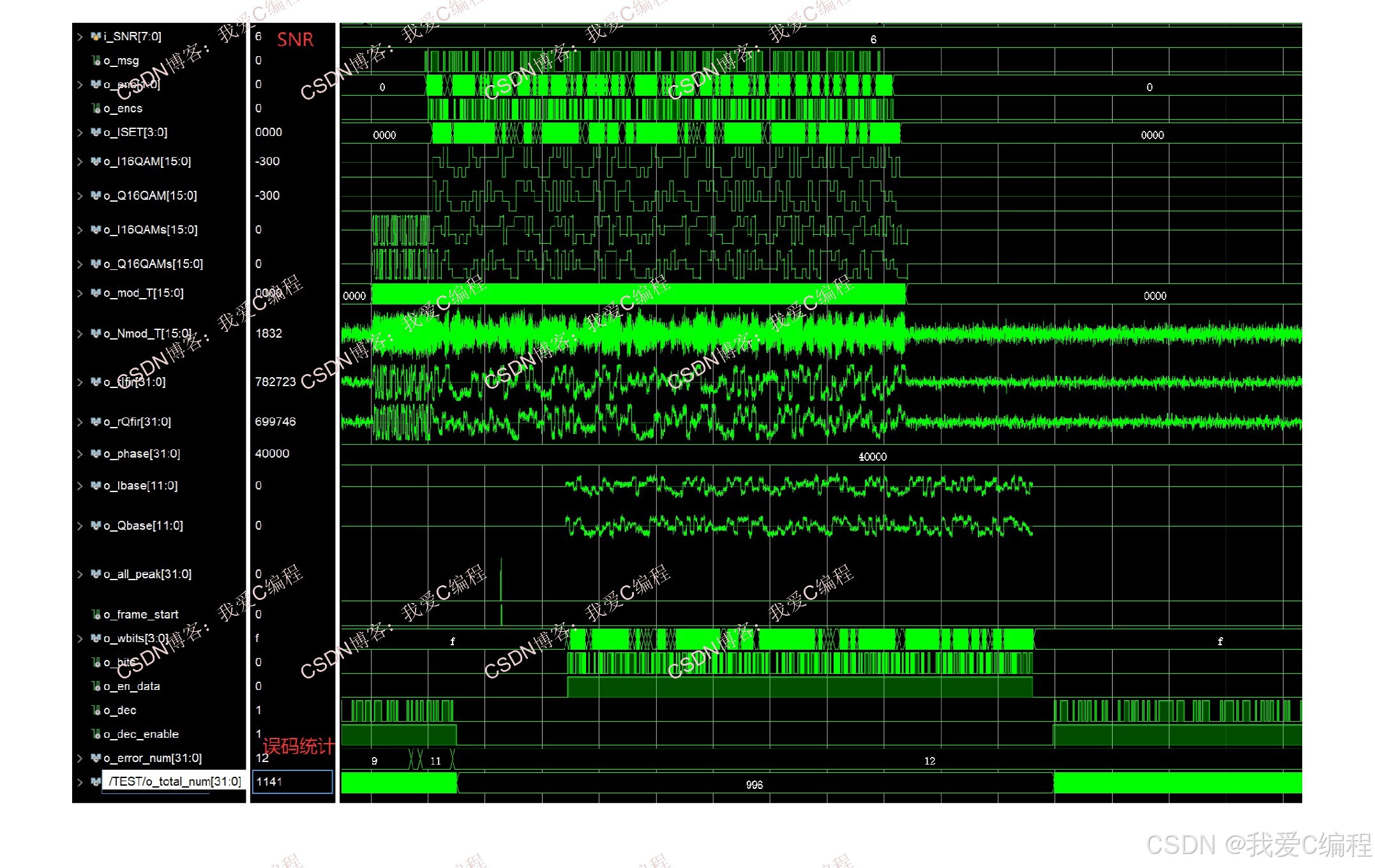

vivado2022.2测试

设置SNR=20db

设置SNR=13db

设置SNR=6db

3.算法涉及理论知识概要

整体系统结构如下所示:

3.1 217卷积编码/维特比译码

217卷积码由生成多项式定义,常见的生成多项式为G1 = 111,G2 = 101,这里的数字表示二进制形式的多项式系数。

卷积编码器:编码过程通过卷积编码器完成,它包含多个滞后寄存器和可编程加法器。输入数据依次通过滞后寄存器,然后按照生成多项式的规则,与滞后数据进行模 2 加法运算,从而生成编码输出。

编码率:217卷积码通常以"2/7"编码率工作,即每2个输入比特会产生7个编码比特,增加了数据的冗余度,使接收端能够检测和纠正传输过程中出现的错误。

维特比译码是一种针对卷积码的最大似然译码算法。它根据接收信号和已知的卷积码生成多项式,在所有可能的发送序列中,通过计算路径度量(如汉明距离等),选择一条最有可能的发送序列作为译码结果,从而纠正传输过程中由于噪声等因素引起的错误,恢复出原始的输入数据。

3.2 16QAM映射/逆映射

16QAM是用两路独立的正交4ASK信号叠加而成,4ASK是用多电平信号去键控载波而得到的信号。它是2ASK调制的推广,和2ASK相比,这种调制的优点在于信息传输速率高。正交幅度调制是利用多进制振幅键控(MASK)和正交载波调制相结合产生的。16进制的正交振幅调制是一种振幅相位联合键控信号。16QAM的产生有2种方法:

(1)正交调幅法,它是有2路正交的四电平振幅键控信号叠加而成;

(2)复合相移法:它是用2路独立的四相位移相键控信号叠加而成。

这里采用正交调幅法。

数字信号是通过FPGA的输出端口生成的。在16QAM调制中,每个符号包含4个比特,因此需要一个4位二进制计数器来生成数字信号。计数器的输出被映射到星座图上的一个点,然后通过数字到模拟转换器(DAC)转换为模拟信号。串/并变换器将速率为Rb的二进制码元序列分为两路,速率为Rb/2.2-4电平变换为Rb/2的二进制码元序列变成速率为RS=Rb/log216的4个电平信号,4电平信号与正交载波相乘,完成正交调制,两路信号叠加后产生 16QAM信号.在两路速率为Rb/2 的二进制码元序列中,经 2-4电平变换器输出为4电平信号,即M=16.经4电平正交幅度调制和叠加后,输出16个信号状态,即16QAM.

16QAM信号采取正交相干解调的方法解调,解调器首先对收到的16QAM 信号进行正交相干解调,一路与cosωct 相乘,一路与sinωct相乘。然后经过低通滤波器,低通滤波器LPF滤除乘法器产生的高频分量,获得有用信号,低通滤波器LPF输出经抽样判决可恢复出电平信号。

3.3 上变频/下变频

将基带信号的频谱频移到所需要的较高载波频率上的过程。原理是把要变频的信号和一个固定频率的本振信号送入一个非线性器件(混频器),得到两个频率相加和相减的频率,然后通过滤波器取出上边带信号,完成上变频,实现将基带信号调制到高频载波上进行传输。

下变频是上变频的逆过程,即将接收到的高频信号的频谱下移到较低的频率上,通常是中频或基带频率。同样通过与本地振荡器产生的正弦信号进行混频,然后取混频之后的下边带信号(或经过进一步处理得到基带信号),以便后续进行信号的解调等处理。

3.4 基于PN导频和cordic的频偏锁定

发送端在发送数据帧时附加已知的伪随机(PN)导频序列,接收端利用PN导频序列来估计信号的频偏。接收端将接收到的导频数据做延迟和共轭相乘,然后根据其实部和虚部使用CORDIC 算法进行迭代旋转操作,从而估计出信号的相位偏移,进而得到频偏值。最后通过将接收信号与一个相反的复数指数函数相乘,实现对接收信号的频偏补偿,将频偏锁定到零。

3.5 基于相关峰的定时点提取

在接收信号中,通过寻找与本地已知序列(如训练序列或导频序列)的相关峰来确定定时点。具体来说,将接收信号与本地序列进行相关运算,当两者的相位和时间对齐时,相关值会出现峰值,这个峰值点对应的位置就是最佳的定时点,用于确定信号的采样时刻,以保证后续信号处理的准确性。

3.6 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.7 采样判决

在确定了定时点后,对接收信号进行采样,将采样值与预设的判决门限进行比较,根据比较结果确定接收信号的电平值,从而恢复出原始的二进制比特流。

4.Verilog核心接口

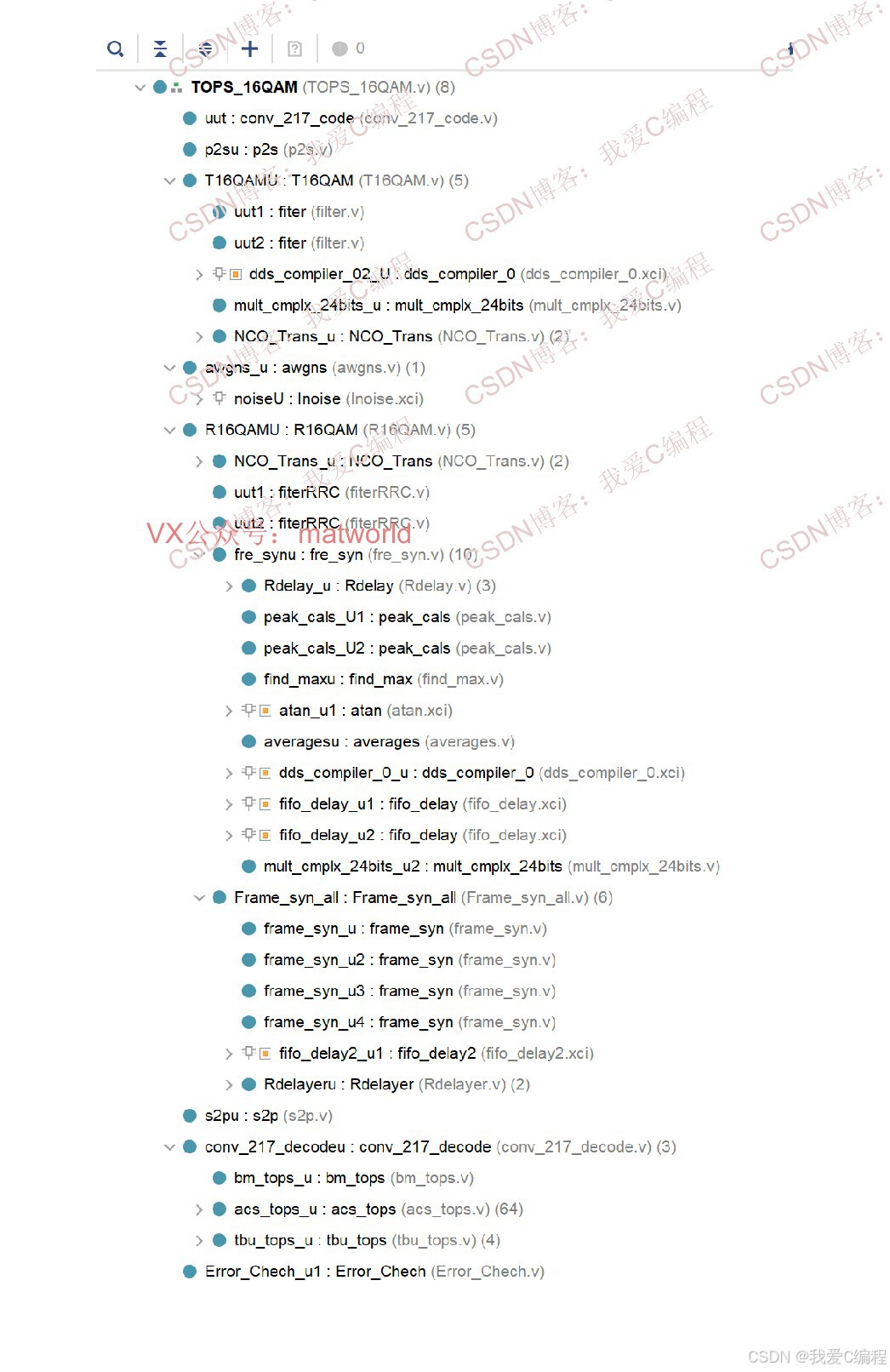

整个程序构架如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/08/05 03:30:02

// Design Name:

// Module Name: TOPS_8PSK

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module TOPS_16QAM(

input i_clk,

input i_clkdx,

input i_clkd2x,

input i_rst,

input signed[7:0]i_SNR,

input[1:0]i_en,

input i_dat,

//卷积编码

output [1:0]o_enc,

output o_encs,

output [3:0]o_ISET,

output signed[15:0]o_I16QAM,

output signed[15:0]o_Q16QAM,

output signed[15:0]o_I16QAMs,

output signed[15:0]o_Q16QAMs,

output signed[15:0]o_mod_T,

output signed[15:0]o_Nmod_T,

output signed[31:0]o_rIfir,

output signed[31:0]o_rQfir,

output signed[31:0]o_phase,

// 解调后I路基带信号(11位有符号)(Demodulated I-channel baseband signal, 11-bit signed)

output signed[11:0]o_Ibase,

output signed[11:0]o_Qbase,

// 信号峰值检测结果(31位有符号)(Signal peak detection result, 31-bit signed)

output signed[31:0]o_all_peak,

// 帧起始标志(高有效)(Frame start flag, active high)

output o_frame_start,

output[3:0]o_wbits,

// 解调后I路数据比特(Demodulated I-channel data bit)

output o_bits,

// 解调数据使能信号(Demodulated data enable signal)

output o_en_data,

// 维特比译码输出(Viterbi decoding output)

output o_dec,

// 译码使能信号(Decoding enable signal)

output o_dec_enable,

output signed[31:0]o_error_num,// 误码计数(31位有符号)(Error bit count, 31-bit signed)

output signed[31:0]o_total_num // 总数据比特计数(31位有符号)(Total data bit count, 31-bit signed)

);0sj4_001m5.参考文献

1\]王建军,徐力,安鹏.基于CORDIC的频偏估计幅角计算算法\[J\].微型机与应用, 2014, 33(7):3.DOI:10.3969/j.issn.1674-7720.2014.07.025. \[2\]向劲松,陈怀柔.QAM调制下基于[卷积码](https://so.csdn.net/so/search?q=%E5%8D%B7%E7%A7%AF%E7%A0%81&spm=1001.2101.3001.7020 "卷积码")与累加编码调制级联的纠错码性能研究\[J\].半导体光电, 2023(6):924-930. ## 5.完整算法代码文件获得 **完整程序见博客首页左侧或者打开本文底部** **V** **(V关注后回复码:X102)**