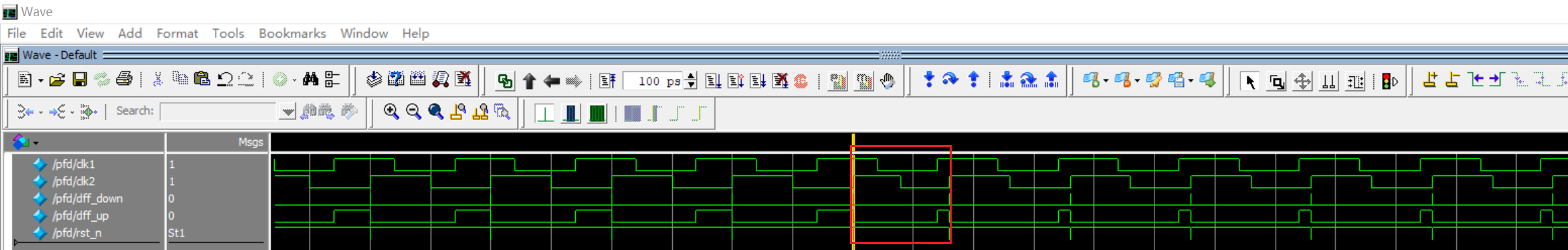

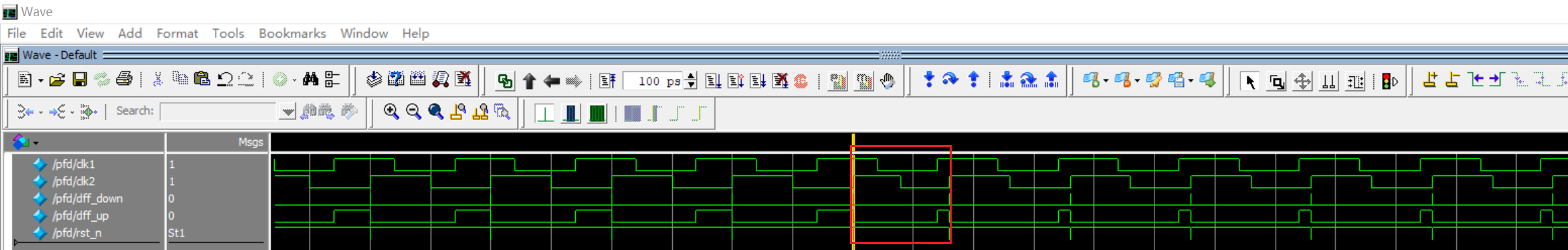

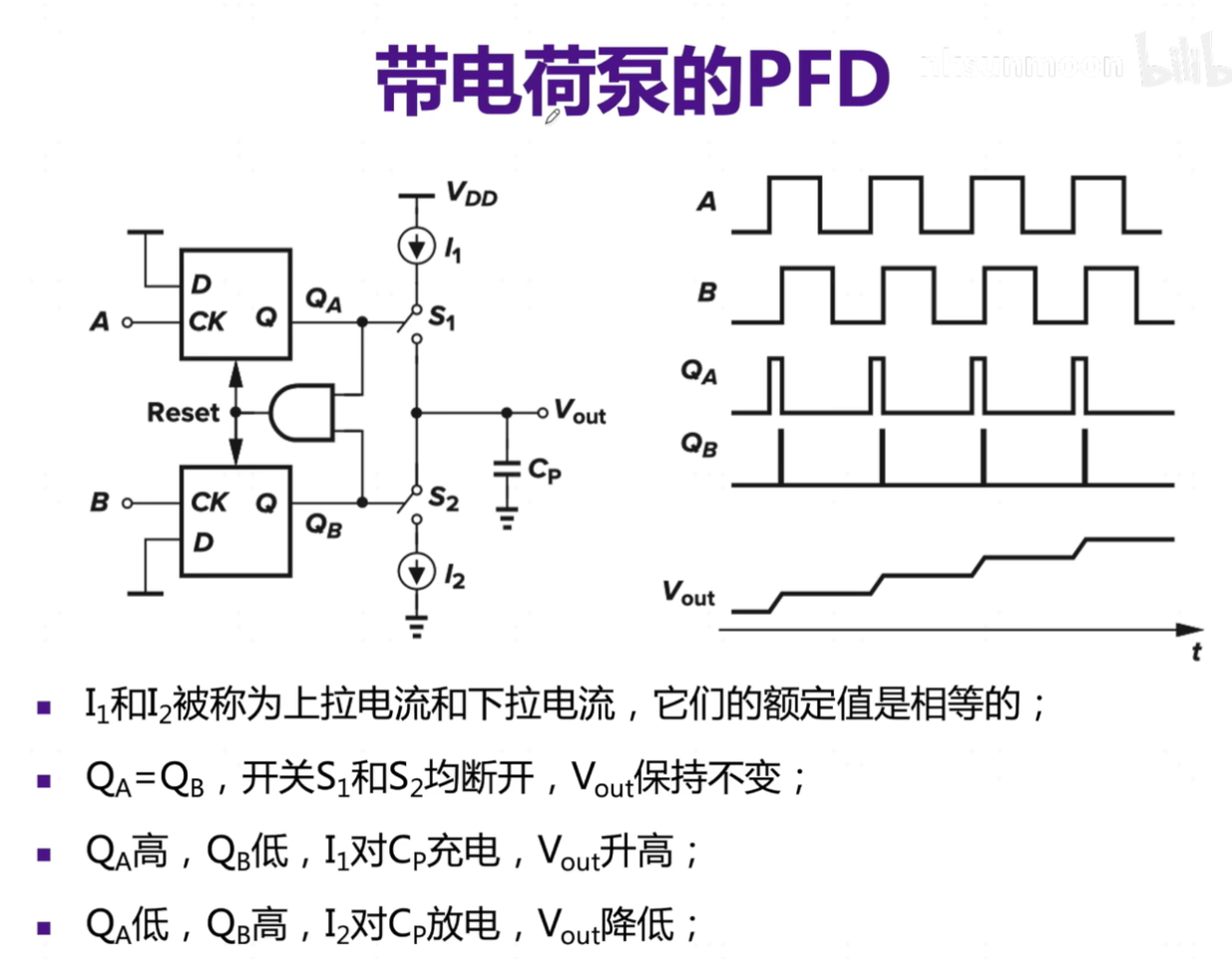

当参考时钟和输出时钟的频率相同,相位不同时。PFD会根据输出时钟的相位的关系决定该增加频率还是减小频率,以下图为例,clk1是参考时钟,clk2是输出时钟。可以看出clk2相位滞后于clk1,由于相位是频率的积分,要想增加clk2的相位,则clk2需要增加频率。可以看出 clk2的频率增加后,此时相位差减小了。

当参考时钟和输出时钟的频率相同,相位不同时。PFD会根据输出时钟的相位的关系决定该增加频率还是减小频率,以下图为例,clk1是参考时钟,clk2是输出时钟。可以看出clk2相位滞后于clk1,由于相位是频率的积分,要想增加clk2的相位,则clk2需要增加频率。可以看出 clk2的频率增加后,此时相位差减小了。