相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

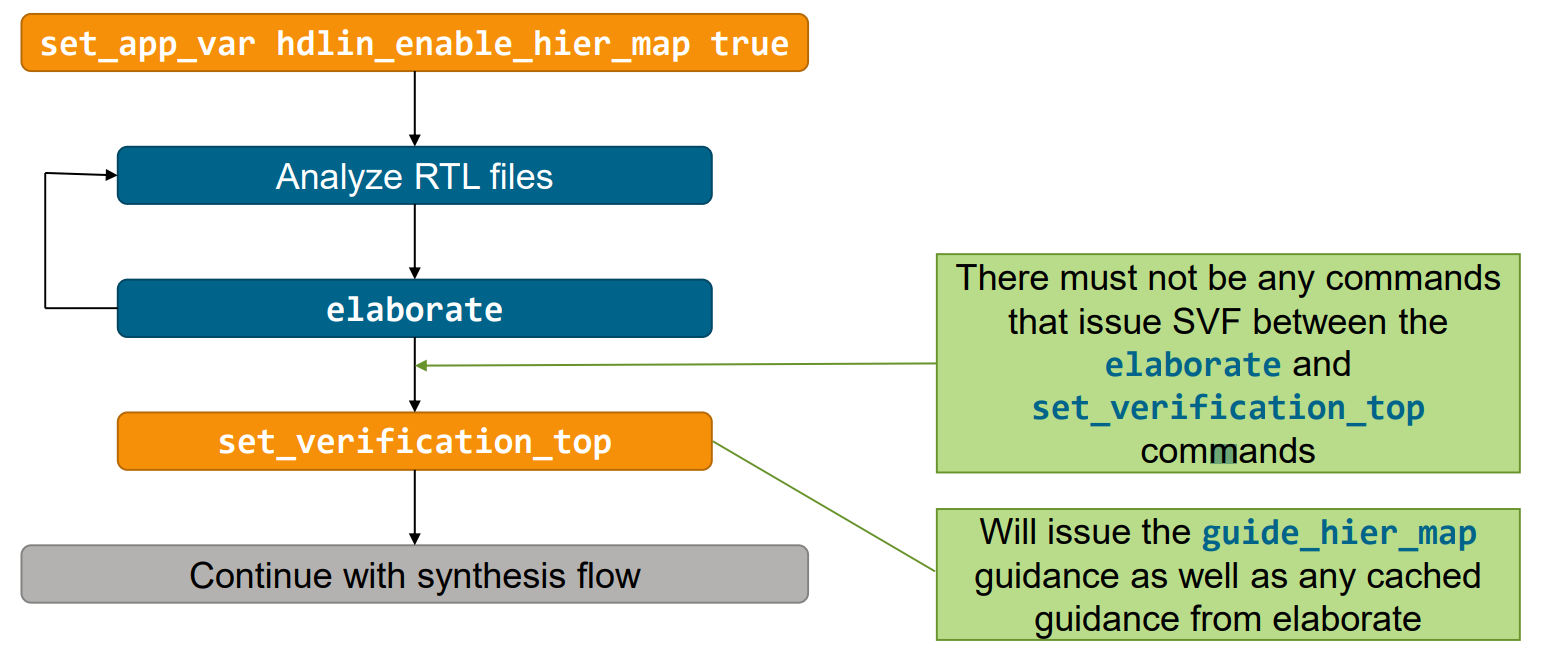

当Design Compiler与Formality在逻辑层次推断(包括多级展开、参数化展开等)上存在差异时,可能导致SVF文件中的guide命令被错误应用,从而造成验证失败。为了解决这个问题,Design Compiler在2018版本推出了Guide Hierarchical Map(GHM) Flow,并新增了hdlin_enable_hier_map变量和set_verification_top命令。

下面给出了Flow示意图和参考脚本。

图1 Guide Hierarchical Map Flow

# specify SVF output file

set_svf ./guidance/top.svf

# read design files

set_app_var hdlin_enable_hier_map true

analyze -format sverilog {sub.sv top.sv}

elaborate top

# issue this command after reading last RTL file

# (and before other commands that can modify hierarchy)

set_verification_top

# apply SDC, UPF, hierarchy manipulation, perform synthesis...hdlin_enable_hier_map变量需要在任何设计读取命令(如analyze、elaborate、read_file等)前设置,以表示开启GHM Flow,此时读取设计过程中HDL Compiler将不会生成通常的guide_instance_map命令。

set_verification_top命令需要在最后一条读取命令后,且任何会引起设计变更的命令(如ungroup、group、uniquify、compile_ultra命令)以及停止SVF记录前执行,否则会出现以下这些错误。

Error: Design modification detected prior to set_verification_top command. (GHM-003)

Error: You must run the set_verification_top command first. (GHM-004)

Error: The SVF guidance information written so far is incomplete and should not be used. (GHM-007)当使用set_verification_top命令时,将会把展开过程中产生的guide_hier_map命令记录在SVF文件中,并作为逻辑层次结构的基线,而后续逻辑层次结构的变化将会以常规的guide_instance_map命令记录。

hdlin_enable_hier_map变量的默认值为false是为了向后兼容,建议在新设计中始终使用GHM Flow。

下面将以一个例子,说明GHM Flow的使用过程。

module bottom #(

parameter WIDTH = 8

)(

input wire clk,

input wire rst_n,

input wire [WIDTH-1:0] d,

input wire we,

output reg [WIDTH-1:0] q

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

q <= {WIDTH{1'b0}};

else if (we)

q <= d;

end

endmodule

module middle #(

parameter WIDTH = 8,

parameter STEP = 1

)(

input wire clk,

input wire rst_n,

input wire en,

output wire [WIDTH-1:0] count

);

wire [WIDTH-1:0] count_next;

wire [WIDTH-1:0] count_q;

assign count_next = en ? (count_q + STEP[WIDTH-1:0]) : count_q;

bottom #(

.WIDTH (WIDTH)

) u_bottom (

.clk (clk),

.rst_n (rst_n),

.d (count_next),

.we (1'b1),

.q (count_q)

);

assign count = count_q;

endmodule

module top (

input wire clk,

input wire rst_n,

input wire en8,

input wire en16,

output wire [7:0] count8,

output wire [15:0] count16

);

middle #(

.WIDTH (8),

.STEP (1)

) u_middle_8 (

.clk (clk),

.rst_n (rst_n),

.en (en8),

.count (count8)

);

middle #(

.WIDTH (16),

.STEP (4)

) u_middle_16 (

.clk (clk),

.rst_n (rst_n),

.en (en16),

.count (count16)

);

endmodule如果不使用GHM Flow进行设计读取,此时对应的SVF文件内容如下所示。

set_svf normal.svf

analyze -format verilog top.v

elaborate top

set_svf -off

##################################################################################

# Copyright 2002-2025 Synopsys, Inc. All rights reserved.

# This Synopsys product and all associated documentation and files are

# proprietary to Synopsys, Inc. and may only be used pursuant to the terms

# and conditions of a written license agreement with Synopsys, Inc. All other

# use, reproduction, modification, or distribution of the Synopsys product or

# the associated documentation or files is strictly prohibited.

##################################################################################

## SVF file read: /home/zhangchen/GHM/normal.svf

guide \

-tool { Design Compiler } \

-version { W-2024.09-SP2 built Nov 28, 2024 } \

-SVF { 21.230 } \

-timestamp { Tue Dec 2 21:17:52 2025 }

## Operation Id: 1

guide_environment \

{ { dc_product_version W-2024.09-SP2 } \

{ dc_product_build_date { Nov 28, 2024 } } \

{ bus_dimension_separator_style ][ } \

{ bus_extraction_style %s\[%d:%d\] } \

{ bus_multiple_separator_style , } \

{ bus_naming_style %s[%d] } \

{ bus_range_separator_style : } \

{ dc_allow_rtl_pg false } \

{ hdlin_allow_4state_parameters TRUE } \

{ hdlin_unified_rtl_read FALSE } \

{ hdlin_enable_hier_naming FALSE } \

{ hdlin_enable_upf_compatible_naming FALSE } \

{ hdlin_vhdl_preserve_case FALSE } \

{ hdlin_generate_naming_style %s_%d } \

{ hdlin_generate_separator_style _ } \

{ hdlin_infer_enumerated_types FALSE } \

{ hdlin_interface_port_downto FALSE } \

{ hdlin_optimize_enum_types FALSE } \

{ hdlin_preserve_sequential none } \

{ hdlin_sverilog_std 2017 } \

{ hdlin_sv_packages dont_chain } \

{ hdlin_sv_union_member_naming FALSE } \

{ hdlin_vhdl_std 2008 } \

{ hdlin_vrlg_std 2005 } \

{ hdlin_v2005_replication_semantics TRUE } \

{ hdlin_while_loop_iterations 4096 } \

{ hdlin_enable_verilog_configurations_canonical TRUE } \

{ hdlin_enable_verilog_configurations_array_n_block TRUE } \

{ hdlin_enable_persistent_macros FALSE } \

{ hdlin_persistent_macros_filename syn_auto_generated_macro_file.sv } \

{ link_portname_allow_period_to_match_underscore false } \

{ link_portname_allow_square_bracket_to_match_underscore false } \

{ port_complement_naming_style %s_BAR } \

{ simplified_verification_mode FALSE } \

{ template_naming_style %s_%p } \

{ template_parameter_style %s%d } \

{ template_separator_style _ } \

{ upf_iso_filter_elements_with_applies_to ENABLE } \

{ upf_isols_allow_instances_in_elements true } \

{ link_library { * your_library.db } } \

{ target_library your_library.db } \

{ search_path { . /opt/Synopsys/syn/W-2024.09-SP2/libraries/syn /opt/Synopsys/syn/W-2024.09-SP2/dw/syn_ver /opt/Synopsys/syn/W-2024.09-SP2/dw/sim_ver } } \

{ hdlin_fmsvf_enable_div_by_pow2 true } \

{ synopsys_root /opt/Synopsys/syn/W-2024.09-SP2 } \

{ cwd /home/zhangchen/GHM } \

{ analyze { -format verilog -library WORK top.v } } \

{ compile_seqmap_propagate_high_effort true } }

## Operation Id: 2

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 3

guide_file_info \

-file { ./top.v } \

-cksum_file { Svf1/checksums/25669_9b0654e05f9f6592a5b167ac15eee5d9.cksum } \

-language { svfFileInfoLangVerilog } \

-nameID { 25669 } \

-cksum { 9b0654e05f9f6592a5b167ac15eee5d9 } \

-version { 21.230 }

## Operation Id: 4

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 5

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 6

guide_instance_map \

-design { top } \

-instance { u_middle_8 } \

-linked { middle_WIDTH8_STEP1 }

## Operation Id: 7

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 8

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 9

guide_instance_map \

-design { top } \

-instance { u_middle_16 } \

-linked { middle_WIDTH16_STEP4 }

## Operation Id: 10

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 11

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 12

guide_instance_map \

-design { middle_WIDTH8_STEP1 } \

-instance { u_bottom } \

-linked { bottom_WIDTH8 }

## Operation Id: 13

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 14

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 15

guide_instance_map \

-design { middle_WIDTH16_STEP4 } \

-instance { u_bottom } \

-linked { bottom_WIDTH16 }

## Operation Id: 16

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 17

guide_environment \

{ { elaborate { -library WORK top } } \

{ current_design top } \

{ compile_seqmap_propagate_high_effort true } }

setup如果使用GHM Flow进行设计读取,此时对应的SVF文件内容如下所示。

set_svf GHM.svf

set_app_var hdlin_enable_hier_map true

analyze -format verilog top.v

elaborate top

set_verification_top

set_svf -off

##################################################################################

# Copyright 2002-2025 Synopsys, Inc. All rights reserved.

# This Synopsys product and all associated documentation and files are

# proprietary to Synopsys, Inc. and may only be used pursuant to the terms

# and conditions of a written license agreement with Synopsys, Inc. All other

# use, reproduction, modification, or distribution of the Synopsys product or

# the associated documentation or files is strictly prohibited.

##################################################################################

## SVF file read: /home/zhangchen/GHM/GHM.svf

guide \

-tool { Design Compiler } \

-version { W-2024.09-SP2 built Nov 28, 2024 } \

-SVF { 21.230 } \

-timestamp { Tue Dec 2 21:23:55 2025 }

## Operation Id: 1

guide_environment \

{ { dc_product_version W-2024.09-SP2 } \

{ dc_product_build_date { Nov 28, 2024 } } \

{ bus_dimension_separator_style ][ } \

{ bus_extraction_style %s\[%d:%d\] } \

{ bus_multiple_separator_style , } \

{ bus_naming_style %s[%d] } \

{ bus_range_separator_style : } \

{ dc_allow_rtl_pg false } \

{ hdlin_allow_4state_parameters TRUE } \

{ hdlin_unified_rtl_read FALSE } \

{ hdlin_enable_hier_naming FALSE } \

{ hdlin_enable_upf_compatible_naming FALSE } \

{ hdlin_vhdl_preserve_case FALSE } \

{ hdlin_generate_naming_style %s_%d } \

{ hdlin_generate_separator_style _ } \

{ hdlin_infer_enumerated_types FALSE } \

{ hdlin_interface_port_downto FALSE } \

{ hdlin_optimize_enum_types FALSE } \

{ hdlin_preserve_sequential none } \

{ hdlin_sverilog_std 2017 } \

{ hdlin_sv_packages dont_chain } \

{ hdlin_sv_union_member_naming FALSE } \

{ hdlin_vhdl_std 2008 } \

{ hdlin_vrlg_std 2005 } \

{ hdlin_v2005_replication_semantics TRUE } \

{ hdlin_while_loop_iterations 4096 } \

{ hdlin_enable_verilog_configurations_canonical TRUE } \

{ hdlin_enable_verilog_configurations_array_n_block TRUE } \

{ hdlin_enable_persistent_macros FALSE } \

{ hdlin_persistent_macros_filename syn_auto_generated_macro_file.sv } \

{ link_portname_allow_period_to_match_underscore false } \

{ link_portname_allow_square_bracket_to_match_underscore false } \

{ port_complement_naming_style %s_BAR } \

{ simplified_verification_mode FALSE } \

{ template_naming_style %s_%p } \

{ template_parameter_style %s%d } \

{ template_separator_style _ } \

{ upf_iso_filter_elements_with_applies_to ENABLE } \

{ upf_isols_allow_instances_in_elements true } \

{ link_library { * your_library.db } } \

{ target_library your_library.db } \

{ search_path { . /opt/Synopsys/syn/W-2024.09-SP2/libraries/syn /opt/Synopsys/syn/W-2024.09-SP2/dw/syn_ver /opt/Synopsys/syn/W-2024.09-SP2/dw/sim_ver } } \

{ hdlin_fmsvf_enable_div_by_pow2 true } \

{ synopsys_root /opt/Synopsys/syn/W-2024.09-SP2 } \

{ cwd /home/zhangchen/GHM } \

{ analyze { -format verilog -library WORK top.v } } \

{ elaborate { -library WORK top } } \

{ current_design top } \

{ compile_seqmap_propagate_high_effort true } }

## Operation Id: 2

guide_hier_map \

-design { top } \

-cells { u_middle_16 } \

-linked { middle_WIDTH16_STEP4 }

## Operation Id: 3

guide_hier_map \

-design { top } \

-cells { u_middle_8 } \

-linked { middle_WIDTH8_STEP1 }

## Operation Id: 4

guide_hier_map \

-design { middle_WIDTH16_STEP4 } \

-cells { u_bottom } \

-linked { bottom_WIDTH16 }

## Operation Id: 5

guide_hier_map \

-design { middle_WIDTH8_STEP1 } \

-cells { u_bottom } \

-linked { bottom_WIDTH8 }

## Operation Id: 6

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 7

guide_file_info \

-file { ./top.v } \

-cksum_file { Svf1/checksums/25669_9b0654e05f9f6592a5b167ac15eee5d9.cksum } \

-language { svfFileInfoLangVerilog } \

-nameID { 25669 } \

-cksum { 9b0654e05f9f6592a5b167ac15eee5d9 } \

-version { 21.230 }

## Operation Id: 8

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 9

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 10

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 11

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 12

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 13

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 14

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

## Operation Id: 15

guide_mark \

-type { svfMarkTypeBegin } \

-phase { svfMarkPhasePresto }

## Operation Id: 16

guide_mark \

-type { svfMarkTypeEnd } \

-phase { svfMarkPhasePresto }

setup