在芯片设计的浩瀚流程中,后端物理设计犹如一座桥梁,将逻辑电路转化为实实在在的硅片结构。而Routing(布线)作为后端设计的核心环节,承担着将数以亿计的晶体管连接成完整电路的重任。它不仅仅是简单的"画线",更是一门平衡时序、功耗、可靠性的精密艺术。本文将带您深入浅出地了解Routing的步骤、重要性及其在先进工艺下的挑战。

一、什么是Routing?从逻辑到物理的蜕变

简单来说,Routing是在芯片布局完成后,通过生成金属线路(wires)和通孔(vias),将同一信号相关的引脚(pins)物理连接起来的过程。在布局阶段,单元(cells)已被放置好,但它们之间的连接还只是逻辑网表(netlist)中的虚拟关系。Routing则通过实际布线,实现这些连接,同时遵守制造设计规则(DRC),确保芯片可生产且性能达标。

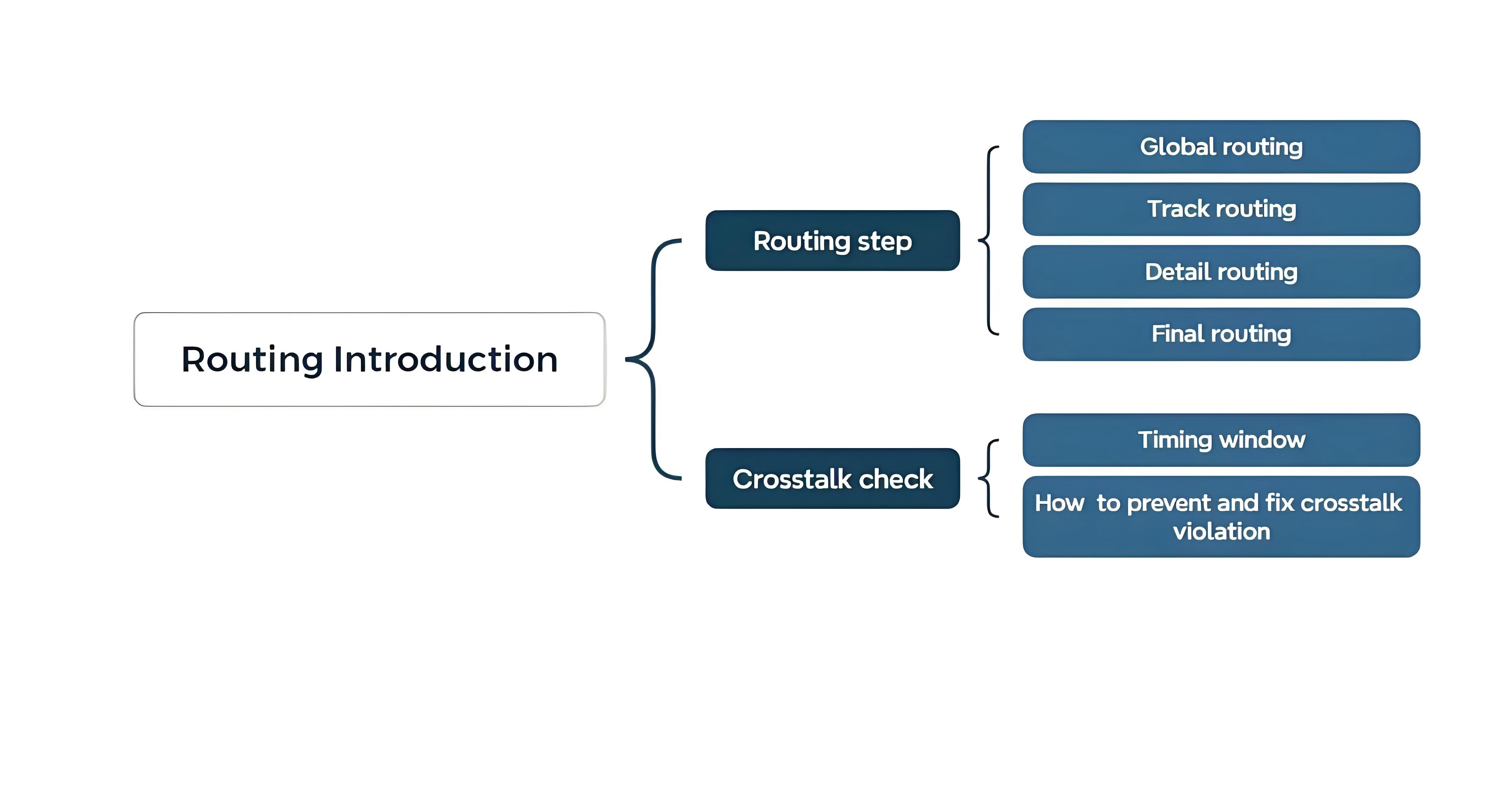

如上图所示,Routing通常分步进行:先通过全局布线(Global Routing)规划大致路径,再通过详细布线(Detail Routing)实现精确连接。这一过程确保了连线的正确性,并直接影响芯片的时序、功耗和信号完整性。

二、Routing的详细步骤:全局与精细的完美结合

Routing过程可细分为多个阶段,层层递进,以确保高效和准确。

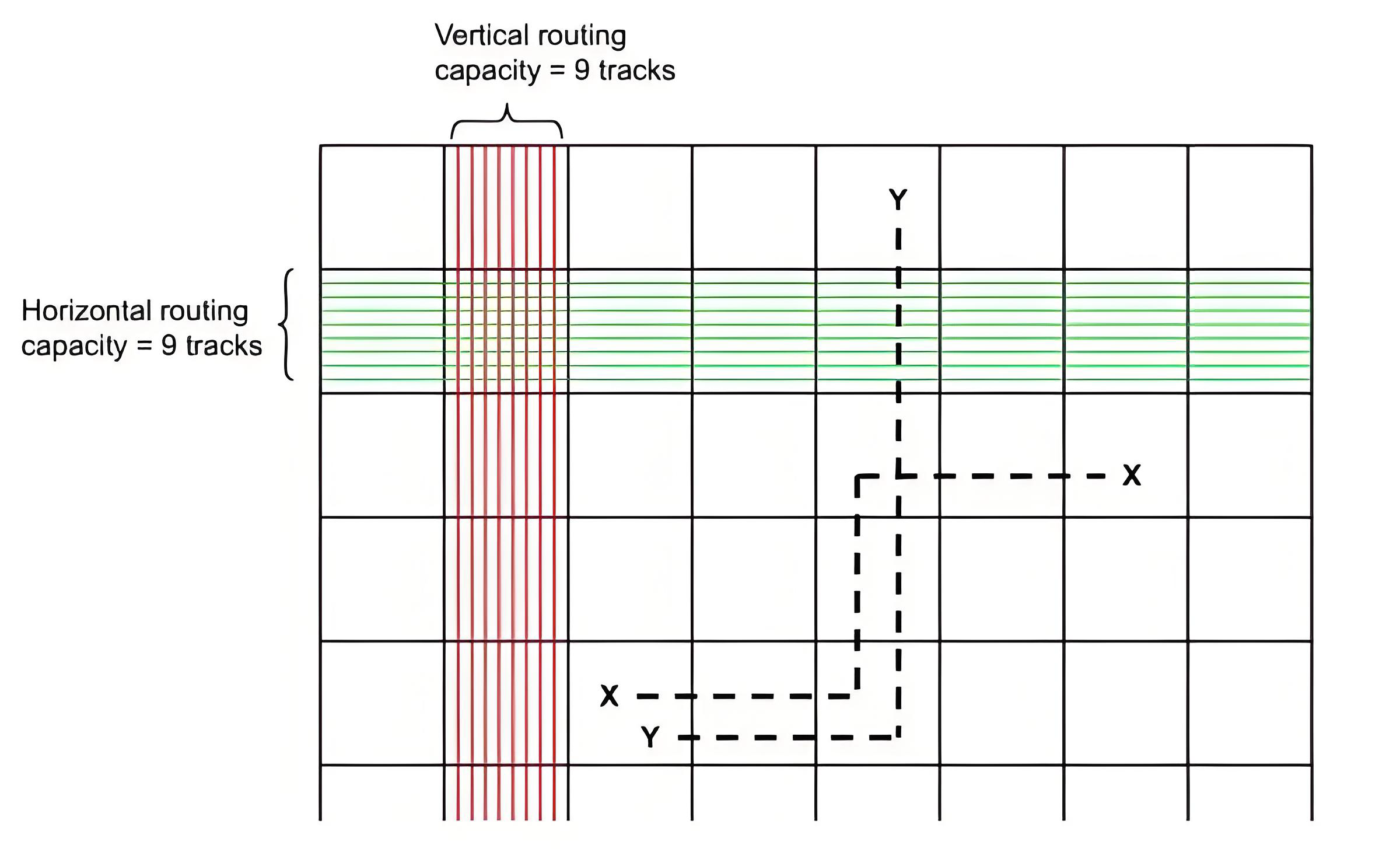

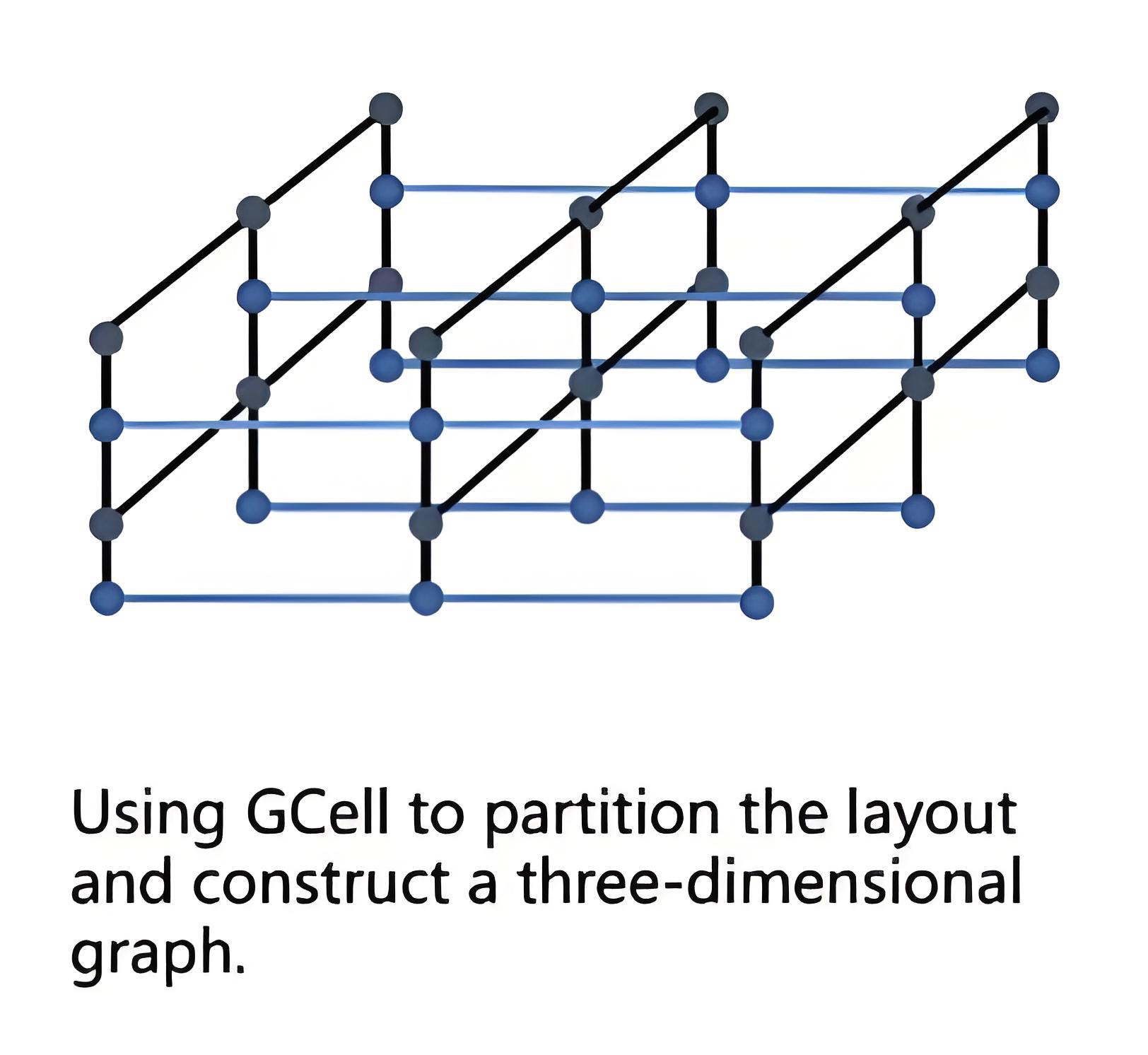

1.全局布线(Global Routing):宏观规划,避免拥堵

全局布线是第一步,它将芯片划分成网格状的全局布线单元(GCell),每个GCell代表一个小的布线区域。工具会快速估算每个信号网络的大致路径,平衡布线资源的需求与供应。关键目标包括:

最小化线长:减少信号延迟。

避免拥堵:防止局部区域布线资源不足,导致短路或绕远。

时序优化:为关键路径预留资源。

以7nm工艺为例,典型参数包括网格尺寸为4μm x 4μm,最大金属层数达12-15层。工具如Innovus通过命令(如set_global_routing_layer_adjustment)调整各层资源分配,确保全局规划合理。

2.轨道布线(Track Assignment):分配具体轨道

在全局布线定义的通道内,轨道布线将每个网络分配到具体的布线轨道上。它遵循全局路径,但不会检查详细DRC,主要目标是生成长而直的 traces,减少通孔数量,提升可靠性。这一阶段需考虑设计规则,如最小线宽和间距(例如Metal3层最小线宽18nm,间距20nm)。

3.详细布线(Detail Routing):精确实现,杜绝违规

详细布线是最终步骤,它在小区域(如sbox)内进行精确布线,确保每条金属线满足所有DRC规则,无短路(short)或开路(open)。工具会实际生成金属图形,并计算电阻、电容和线长,以验证时序。如果发现问题,还会进行搜索修复(Search and Repair),迭代优化。

芯片布线面临巨大挑战:成千上万的宏模块、数亿门电路、数百万条连线,总长度可达公里级。详细布线必须高效处理这些复杂性,同时保证100%连接。

4.最终布线(Final Routing):收尾工作,提升可靠性

包括金属填充(Metal Fill)以平衡密度(目标20-30%覆盖率),修复天线效应(如插入二极管),以及串扰防护。最终输出GDS文件,用于制造。

三、Routing的重要性:为什么它关乎芯片成败

Routing绝非简单的连接工作,其重要性体现在多个方面:

性能保障:布线质量直接决定信号时序。通过时序驱动布线(Timing Driven Routing),工具会优先满足关键路径的时序预算,避免setup/hold违规。Routing的目标是"满足setup和hold时间要求",否则芯片可能无法运行在目标频率。

可靠性提升:良好的布线最小化串扰(crosstalk)和噪声。串扰可能导致信号重叠超过时钟周期的10%,引发故障。Routing阶段通过间距调整、屏蔽线(shield nets)等方式防护,如在7nm节点,耦合电容占比高达40%,需引入ML预测模型优化。

可制造性:遵守DRC规则是底线。Routing工具需确保线宽、间距、通孔密度等符合工艺要求,避免生产失败。在先进节点,DRC-free布线往往需要多次迭代才能实现。

面积与功耗优化:通过最小化线长和通孔数,Routing能减少芯片面积和动态功耗。网格化布线系统(Grid-based Routing)可以简化实现,提高效率。

四、先进工艺下的挑战与对策

随着工艺节点微缩至7nm、5nm甚至更小,Routing面临新挑战:

串扰加剧:耦合电容占比上升,7nm时需使用屏蔽线;更先进节点如inm,量子隧穿效应要求Air Gap隔离技术。

拥堵问题:高密度设计易导致局部拥堵,全局布线需准确预估congestion,否则详细布线时可能出现绕远(detour)。

时序收敛困难:多高频时钟设计下,完美布线往往需多次增量路由(incremental routing)才能达到时序和DRC平衡。

对策包括分层优化(全局→详细)、三维防护(横向间距+纵向隔离)以及智能算法(如Flute算法快速生成斯坦纳树)。工具如Custom Compiler提供自动功能(如via更新、bus扩展),提升设计效率。

结语:Routing------芯片设计的"最后一公里"

Routing是芯片后端设计中连接逻辑与物理的"最后一公里",其精度和效率直接决定芯片的性能、可靠性和成本。在AI、5G等应用驱动下,先进工艺对Routing提出了更高要求,需要设计师与工具紧密配合,不断优化策略。Routing是一个复杂组合问题,但通过分层方法和智能工具,我们能够驾驭这一艺术,连接起芯片内的每一个"点",最终点亮数字世界。