10bit 100MS/s 流水线Pipelined ADC电路,采用0.18um工艺,直接可以用,直接可以跑仿真,包含实际电路和各模块的测试电路,有效位9.5bit,适合学习。

最近在研究ADC电路相关内容,发现了一个超赞的 10bit 100MS/s 流水线Pipelined ADC电路,基于0.18um工艺设计,简直就是学习ADC的神器,必须来和大家分享分享。

整体架构与优势

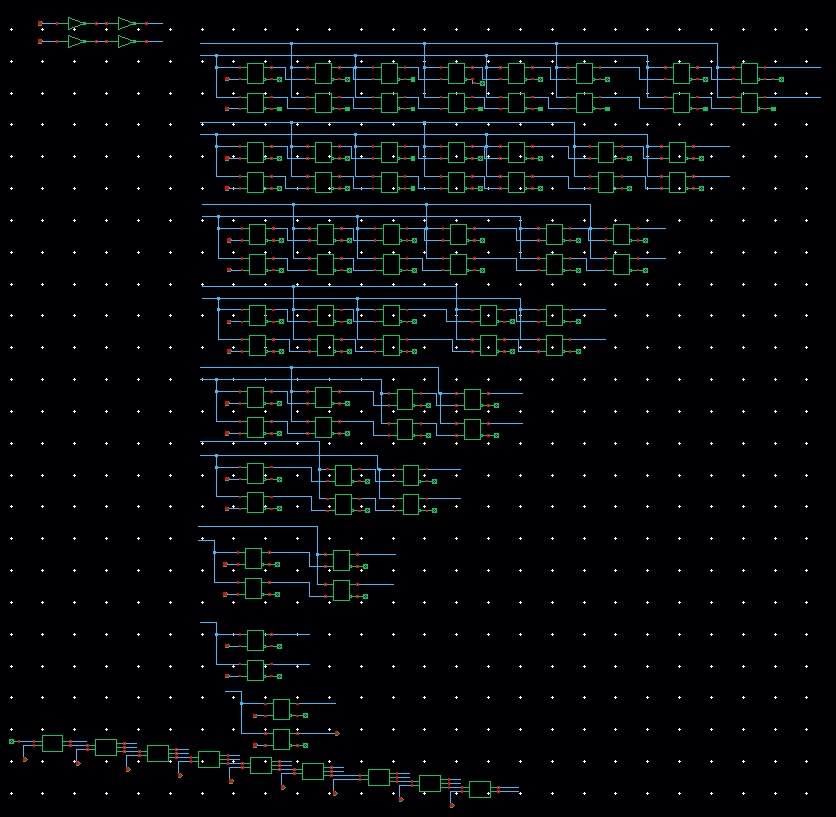

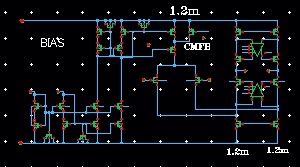

流水线Pipelined ADC是一种常用的模数转换结构,它通过多级流水线的方式,在速度和精度之间取得较好的平衡。这款10bit 100MS/s的ADC,不仅满足了一定的转换精度需求,100MS/s 的采样速率也使其适用于不少高速信号处理场景。而且采用0.18um工艺,这个工艺在集成电路设计学习中较为常见,资料丰富,方便深入研究。

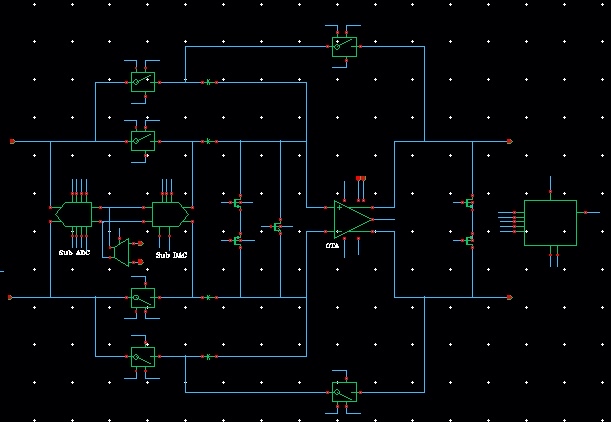

实际电路解析

实际电路部分是整个设计的核心。以其中一级流水线为例(这里为简化示意,实际可能更复杂):

verilog

module pipelined_stage(

input wire clk,

input wire rst,

input wire [10:0] in_signal,

output reg [3:0] sub_code,

output reg [10:0] residue

);

// 采样保持电路部分简化示意

reg [10:0] sampled_signal;

always @(posedge clk or posedge rst) begin

if (rst)

sampled_signal <= 11'b0;

else

sampled_signal <= in_signal;

end

// 闪速ADC模块简化示意,用于生成子代码

always @(*) begin

if (sampled_signal >= 11'd1024)

sub_code = 4'd8;

else if (sampled_signal >= 11'd512)

sub_code = 4'd4;

else if (sampled_signal >= 11'd256)

sub_code = 4'd2;

else if (sampled_signal >= 11'd128)

sub_code = 4'd1;

else

sub_code = 4'd0;

end

// 余量生成部分

always @(*) begin

case (sub_code)

4'd8: residue = sampled_signal - 11'd1024;

4'd4: residue = sampled_signal - 11'd512;

4'd2: residue = sampled_signal - 11'd256;

4'd1: residue = sampled_signal - 11'd128;

default: residue = sampled_signal;

endcase

end

endmodule在这段代码里,pipelinedstage**模块实现了流水线中的一级。clk和rst分别是时钟和复位信号。in signal是输入的模拟信号(这里用11位表示,实际是模拟量的数字等效)。首先通过一个简单的采样保持电路在时钟上升沿对输入信号进行采样。接着,利用一个简化的闪速ADC结构根据采样值生成子代码sub_code,这个子代码反映了输入信号大致的量化值。最后根据子代码计算出余量residue,余量会传递到下一级流水线进一步处理。通过多级这样的流水线级联,就能实现高精度的模数转换。

测试电路的重要性与实现

对于这样一个复杂的电路,测试电路必不可少。它不仅能验证实际电路功能是否正确,还能帮助我们分析电路性能。以测试上述pipelined_stage模块为例:

verilog

module tb_pipelined_stage;

reg clk;

reg rst;

reg [10:0] in_signal;

wire [3:0] sub_code;

wire [10:0] residue;

pipelined_stage uut (

.clk(clk),

.rst(rst),

.in_signal(in_signal),

.sub_code(sub_code),

.residue(residue)

);

initial begin

clk = 0;

forever #5 clk = ~clk; // 10ns周期,模拟100MHz时钟

end

initial begin

rst = 1;

in_signal = 11'd0;

#20;

rst = 0;

in_signal = 11'd600;

#20;

in_signal = 11'd150;

#20;

// 可以继续添加更多测试激励

end

endmodule在测试平台tbpipelinedstage中,首先定义了时钟clk、复位rst和输入信号insignal*,并将它们连接到要测试的模块pipelined* stage(实例名为uut)。通过initial块产生一个周期为10ns的时钟信号,模拟100MHz的工作频率。另一个initial块则提供了测试激励,先将复位信号置高,输入信号清零,一段时间后释放复位,并改变输入信号的值,以此观察subcode**和residue的输出是否符合预期,从而验证pipelined stage模块功能的正确性。

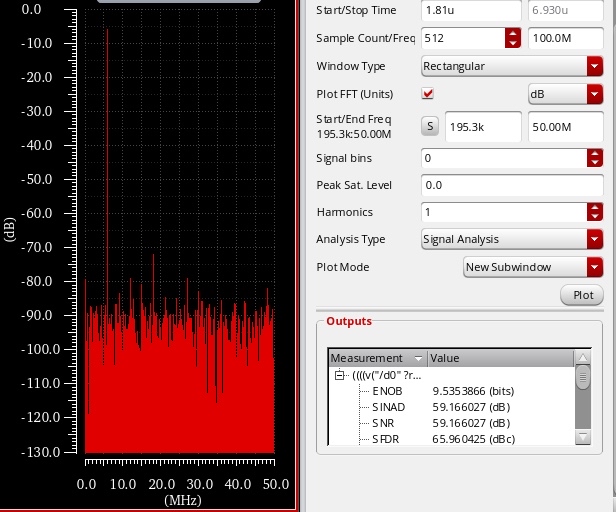

9.5bit有效位的奥秘

这款ADC宣称有效位达到9.5bit,有效位反映了ADC实际能分辨的信号电平数。一般来说,理想的10bit ADC理论上能分辨2\^{10}=1024个不同电平,但由于电路中的各种非理想因素,如噪声、失调等,实际有效位会低于理论值。通过优化电路设计,如采用更好的放大器设计减少噪声,精心布局减少信号干扰等手段,使得这款ADC能达到9.5bit的有效位,在实际应用和学习研究中都有不错的表现。

总的来说,这个10bit 100MS/s 流水线Pipelined ADC电路,从实际电路到测试电路一应俱全,直接可用可仿真,对于想要深入学习ADC电路设计和相关知识的朋友,绝对是不可多得的好资源,强烈推荐大家上手试试!