1.什么是LTR

EP通过LTR机制告知RC,其发送的memory读写请求,需要在多长时间之内返回(latency requirements),以便RC调整最佳的处理策略,帮助系统平衡能耗与性能。但是协议不强制RC一定要满足整个latency requirement。

2. 工作机制解析

- 触发条件 :

- 设备初始化时主动发送

- 运行中延迟需求变化时动态更新-------->及时发送LTR 更新延时

- 系统通过PME(Power Management Event)请求

- 系统响应 :

- 电源管理器根据T_{LTR_MAX}调整设备低功耗状态(L0s/L1/L1.x)

- 调度器依据T_{LTR_MIN}保证关键操作时效性

3.LTR 的好处或者使用LTR的意义?

- 能效优化 :允许系统在满足延迟约束下,将设备置于更深省电状态,如:

P_{\\text{save}} \\propto \\frac{1}{T_{LTR_MAX}} \\quad \\text{(功耗与最大延迟负相关)}

- QoS保障:防止高优先级设备(如GPU/NVMe)因延迟超标丢包[^2]。

4.如何开启LTR

由于LTR功能时可选的,因此开启LTR首先需要确认设备是否支持该功能,此外由于功能是可选的,因此必须在整条链路上全部使能并support LTR时,LTR功能才可以正常,否则一个不支持LTR的Downstream Port收到一个LTR Message,需要当作unsupported request处理。

LTR Support寄存器位于Device Capabilities 2 Register(bit 11)

LTR Enable寄存器位于Device Control 2 Register(bit 10)

5.延时如何确认

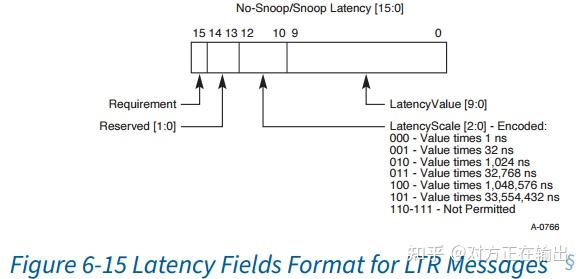

如果Requirement (bit15)置位,则LatencyValue和LatencyScale域段都是有效的;如果Requirement为0,则LatencyValue和LatencyScale域段可以忽略。

当EP发送LTR Message时,允许只有No-Snoop Request或者只有Snoop Request是有效的,当然也可以是两者同时有效。(有点废话的感觉)

Max Snoop Latency Register (Offset 04h)表示了EP最大可接受的snoop latency:

Max No-Snoop Latency Register (Offset 06h)表示了EP最大可接受的no-snoop latency:

LatencyScale与LatencyValue可以确认最终支持的最大返回延时。不同的design 设计可能不同,LatencyValue和LatencyScale同时为0,表示EP需要RC提供best possible service,即尽量短的处理延迟。

6.延时怎么计算

Latency的具体含义如下:

- 对于Non-Posted请求,latency为device发送请求的最后一个symbol,到收到第一个completion的第一个symbol之间的时间间隔;

- 对于Posted请求,latency用于流控信用不足的反压场景,具体为device发送请求的最后一个symbol,到收到返回credits的DLLP的第一个symbol之间的时间间隔(在流控信用不足场景下,device在收到DLLP返回的信用之后才能发一个posted请求)。

7.LRT 发送message 约束

- 协议建议EP在LTR被使能或者EP的service requirement被改变之后,尽快发送LTR Message,但强烈建议在500us时间内不要发送超过两个LTR Messages。DP如果在500us时间收到超过LTR Messages,也不能当作错误处理,必须将所有的LTR Messages都正确处理。

- 对于一个Multi-Function Devices (MFDs),发送的LTR Message中的LatencyValue必须为它所有function中的最小值。

- 对于switch,如果支持LTR,则所有ports都需要支持LTR。

- 其可以被刷新/更新的动作。也就是,在出现Link-down的时候,相关信息必须被清掉;在信息需要刷新的时候,要及时告知DSP。比如,通过PMCSR进入低功耗状态时non-D0,如果device有发过LTR给到RC,那它必须在进入non-D0状态钱,发出requirement clear的消息。当通过PMCSR回到D0状态时,再重新发送有效的LTR消息建立延迟需求。

- 如果一个device(EP)发送LTR Message之后,LTR Mechanism Enable bit被清除(通过RP的ConfigWr或者FLR),则device必须再发送一个将两个requirement bit都置为0的LTR Message。

- Ports that support the L1.2 substate for ASPM L1 must support Latency Tolerance Reporting (LTR).

8.LTR 在RC EP的系统里面的工作过程(个人理解欢迎指正)

通过当前的项目,简单分享一下LTR的整个过程

- EP RC 均处于L0

- EP 发送LTR meassge 给到RC上报自己的latency

- RC读取meassge 信息获取对应该EP的latency capacity

- 在进入L1.2的时候LTSSM需要满足LTR 中的latency以后才可以从L1.1进L1.2