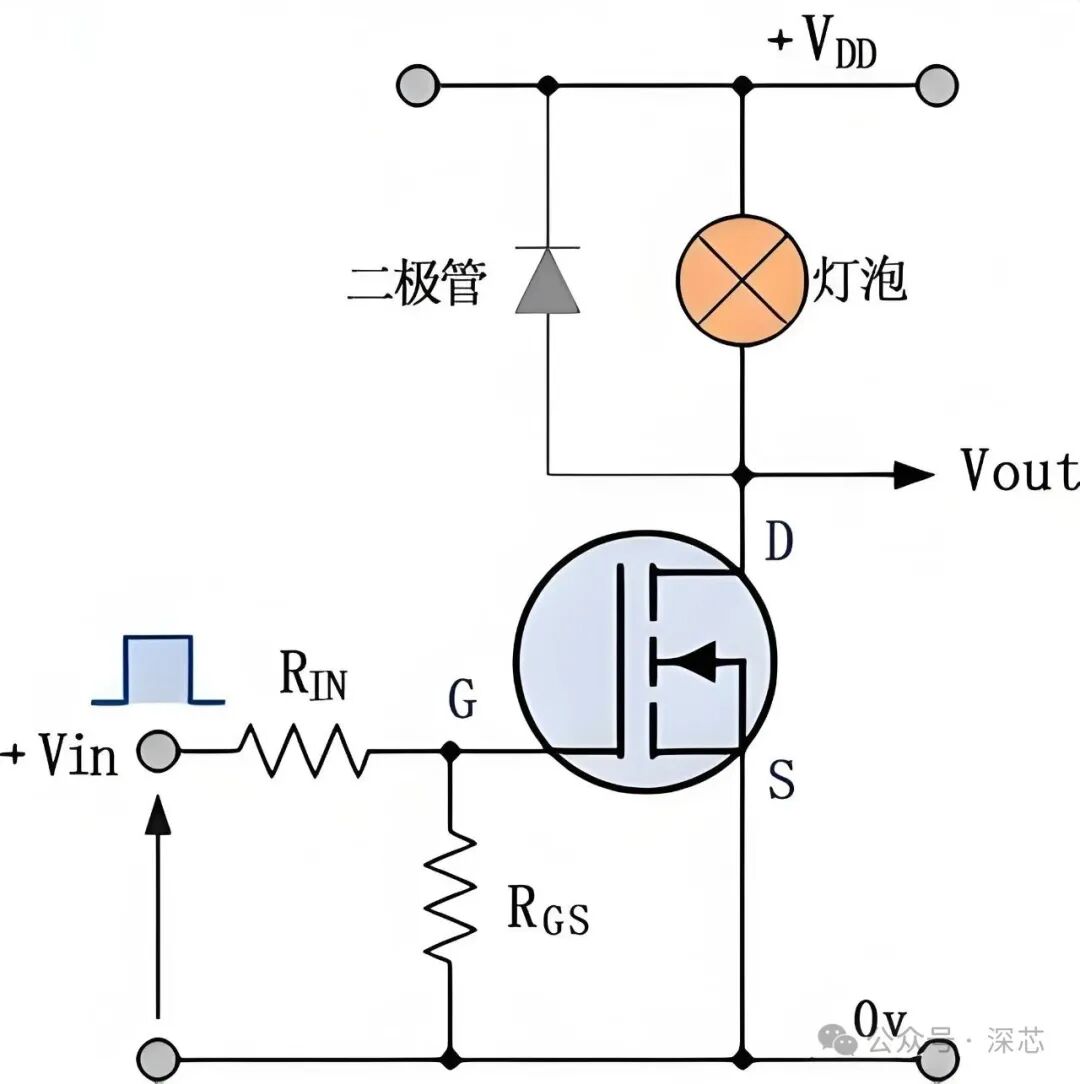

在MOS管的驱动电路里经常会看到Gate和Source两端并联一个几K的电阻,常称下拉电阻或泄放电阻,那么这个电阻有什么作用呢?

- 防止静电击穿(ESD保护)

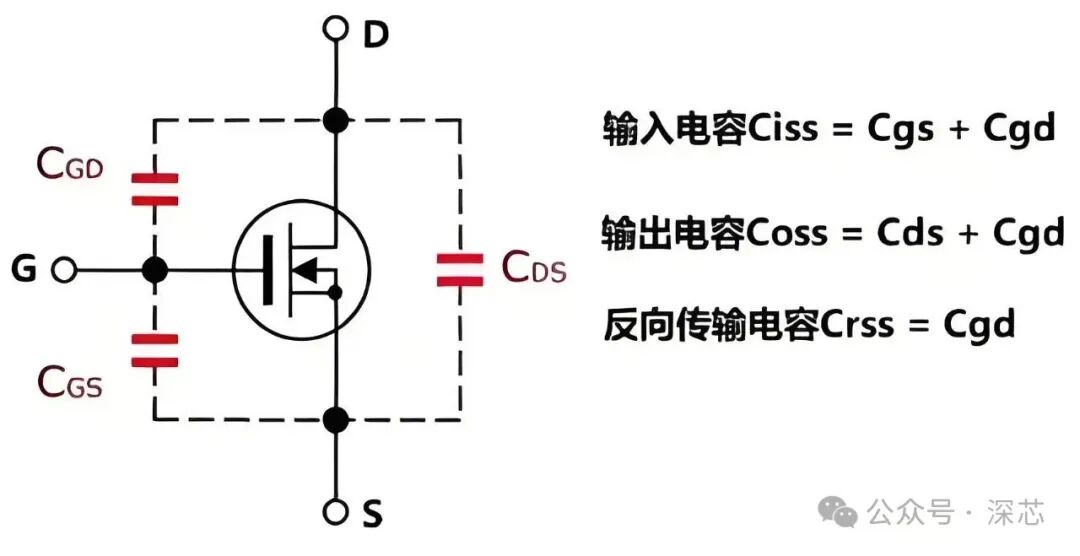

MOS管的栅极输入阻抗极高(约10⁹--10¹²Ω),而G-S间电容极小(pF级)。根据公式 U=Q/C,少量静电电荷即可产生高压,导致栅氧化层击穿。并联电阻(典型值5--20kΩ)为静电电荷提供低阻抗泄放路径,避免电压累积。

- 避免误触发和误导通

-

驱动电路失效时:若驱动芯片未工作或输出高阻态,D-S间电压(VDS)会通过米勒电容(Cgd)向G-S电容(Cgs)充电,抬升栅极电压 Vgs。当 Vgs>Vth(阈值电压)时,MOS管意外导通,可能烧毁器件。

-

dV/dt干扰时:Drain端的快速开关或电压突变(如电源启动)产生的瞬态电流通过寄生电容Cgd耦合至栅极,下拉电阻可钳位 Vgs至低电平,抑制误导通。

- 确保可靠关断

当驱动信号消失(如前级开路),电阻将栅极电位固定为源极电平(Vgs=0),避免因电荷残留导致关断延迟或半导通状态

附加功能与设计考量

-

优化开关损耗与速度

虽然主要功能非调速,但电阻影响关断时间:

-

阻值过小(<1kΩ):驱动电流增大,增加前级功耗,可能损坏驱动芯片

-

阻值过大(>100kΩ):泄放电荷速度慢,关断延迟,导致导通损耗升高

建议范围: 5--20kΩ(常见5kΩ、10kΩ),平衡关断速度与功耗

-

-

配合电容增强抗干扰

部分设计在G-S间并联电容(如2.2nF),与电阻构成RC滤波器,进一步抑制高频噪声和电压尖峰

总结

GS并联电阻的核心价值是提供"被动安全":

-

静电防护 → 避免器件损毁;

-

电荷泄放 → 防止电压累积导致误触发;

-

电位钳位 → 确保关断可靠性。

设计时需权衡阻值对开关速度、功耗的影响,并结合实际场景选择(如高噪声环境需更小阻值)。忽略此电阻可能导致MOS管在未驱动时神秘损坏,尤其在电源、电机控制等高压大电流应用中。