目录

[二、PCB 核心模块详细设计](#二、PCB 核心模块详细设计)

[(六)LED 指示模块(状态显示单元)](#(六)LED 指示模块(状态显示单元))

[三、6 层 PCB 电路板绘制关键技术要点总结](#三、6 层 PCB 电路板绘制关键技术要点总结)

[(二)BGA 器件扇出设计要点(重点难点)](#(二)BGA 器件扇出设计要点(重点难点))

[(六)DRC 检查与优化要点(质量管控要点)](#(六)DRC 检查与优化要点(质量管控要点))

一、项目概述与设计目标

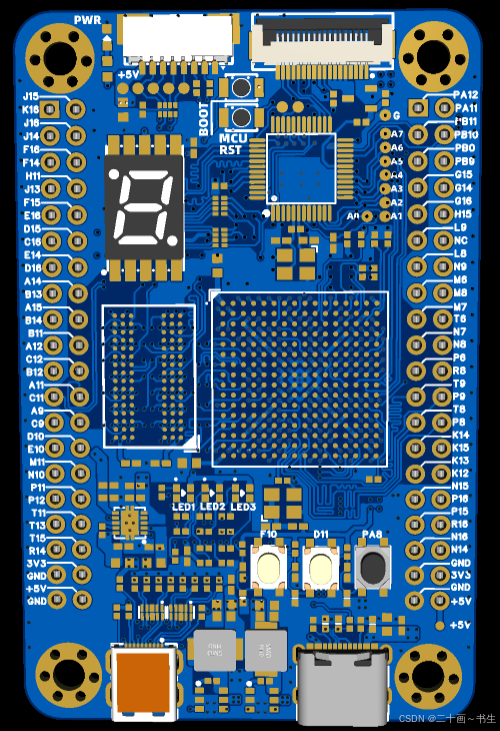

本项目聚焦于立创・逻辑派 FPGA-G1 开发板的 6 层 PCB 全流程设计与优化,核心适配高云 GW2A-LV18 FPGA 为主控芯片、GD32F303 单片机为辅助控制单元的异构硬件架构,旨在打造一款兼具高速传输、稳定供电、多接口扩展能力与高可制造性的入门级 FPGA 开发硬件载体。设计全程采用嘉立创 EDA 专业版作为核心设计工具,严格遵循 PCB 设计领域 SI(信号完整性)、PI(电源完整性)核心规范及 DFM(可制造性设计)原则,完整覆盖原理图核对、层叠结构规划、器件布局、布线优化、DRC 规则检查及生产文件输出等全流程开发工作,最终形成可直接用于投产的 PCB 设计文件、Gerber 生产文件及标准化物料清单(BOM),目前项目已完成全部设计工作,处于待投产状态。

相较于传统 4 层 PCB 设计,本次 6 层 PCB 设计重点攻克了 FPGA 高速信号传输干扰、多电源域合理分割、BGA 高密度封装器件扇出困难三大核心痛点。通过科学的层叠规划、精细化的布线优化及严格的规则管控,显著提升了开发板的信号稳定性、抗干扰能力及供电可靠性,为后续 FPGA 逻辑开发、外设接口调试、数字逻辑验证提供了坚实的硬件支撑,可广泛适配入门级 FPGA 学习、校园课程设计、简易工业控制项目及数字电路原型验证等多种应用场景。

二、PCB 核心模块详细设计

立创・逻辑派 FPGA-G1 开发板 6 层 PCB 依据功能划分,共设计 7 大核心模块,各模块的布局、布线均结合其功能特性、信号类型及性能需求进行针对性设计,兼顾模块独立性与协同性,确保整个开发板稳定高效运行,各模块详细设计如下:

(一)核心控制模块(主控核心单元)

核心控制模块作为整个开发板的"大脑",是实现数字逻辑运算、信号处理及外设控制的核心单元,主要集成高云 GW2A-LV18 FPGA 芯片与 GD32F303 单片机芯片,其中 FPGA 采用 BGA 封装(引脚密度高、集成度高),单片机采用 LQFP 封装(焊接便捷、稳定性强)。功能分工上,FPGA 作为主控制核心,承担数字逻辑运算、高速信号处理、外设接口驱动与控制等核心任务;GD32F303 单片机作为辅助控制单元,负责系统初始化、串口通信中转、电源状态管理及简单 IO 口控制,二者通过 SPI 高速接口实现数据交互与指令协同,确保系统指令传输顺畅、响应及时。

PCB 设计层面,将该模块优先布置在电路板中心区域,远离电路板边缘及大功率器件,最大限度减少外部电磁干扰与机械干扰;针对 BGA 封装器件的扇出难点,优化扇出布线策略,确保每个引脚顺利扇出,同时缩短扇出布线长度,避免信号延迟与串扰;模块周围预留合理接地空间,增强接地可靠性,进一步抑制信号干扰,确保核心芯片稳定工作。

(二)电源供电模块(稳定供电单元)

电源供电模块是开发板稳定运行的"动力源泉",核心目标是为整个开发板各模块提供稳定、纯净、匹配的供电,适配多电源域的供电需求,主要由 5V USB 输入接口、LDO 稳压芯片、滤波电容、电源指示灯及电源保护器件组成。供电流程上,采用 5V USB 接口作为外部供电输入,输入电压经过 LDO 稳压芯片进行多级稳压转换,输出 3.3V、1.8V、1.2V 三种核心电压等级,分别为 FPGA 芯片(核心电压 1.2V、IO 电压 3.3V)、单片机(3.3V)、扩展接口(3.3V)及其他辅助器件提供精准供电,满足不同器件的供电需求。

PCB 设计过程中,采用独立电源层与地层的设计方式,实现不同电压域的电源分割,清晰划分各电源区域,避免不同电压域之间的干扰;在电源芯片输出端、各器件电源引脚附近,均布置高频滤波电容(10nF)与去耦电容(0.1μF),且电容尽量靠近引脚与接地过孔,有效抑制电源噪声,滤除杂波,为器件提供瞬时稳定电流;优化电源布线设计,增大电源线线宽(匹配对应电流需求),减少线损与电压跌落,确保大电流供电时(如 FPGA 核心供电)无发热、电压不稳定等问题;同时设计电源指示灯,直观显示供电状态,便于后期调试与故障排查。

(三)下载与调试模块(程序下载与调试单元)

下载与调试模块主要承担 FPGA 程序下载、单片机程序下载及系统调试三大核心功能,是开发板开发、调试与维护的关键模块,主要由 USB 转串口芯片、JTAG 下载接口、复位按键及调试指示灯组成。具体功能上,USB 转串口芯片实现电脑与开发板之间的串口通信,既用于程序下载(单片机程序、FPGA 辅助程序),也用于调试信息输出,便于开发人员查看系统运行状态与故障信息;JTAG 下载接口用于 FPGA 程序的在线下载与在线调试,支持硬件断点、单步执行、寄存器查看等调试功能,大幅提升 FPGA 开发调试效率;复位按键用于系统紧急重启,当程序异常或系统故障时,可快速复位系统,保障开发调试便捷性。

PCB 设计中,将该模块布置在电路板边缘位置,方便开发人员连接下载线、调试线,提升操作便捷性;优化串口信号与 JTAG 信号的布线,缩短信号线长度,减少信号干扰,确保程序下载稳定、调试信息传输无误,避免出现程序下载失败、调试信息丢失、调试指令无响应等问题;复位按键附近布置下拉电阻,增强复位稳定性,避免误触发复位;同时设计调试指示灯,直观显示调试状态。

(四)扩展接口模块(功能扩展单元)

扩展接口模块的核心作用是扩展开发板的功能边界,适配多种外部外设,满足不同场景下的开发需求,主要集成 GPIO 扩展接口、UART 串口接口、SPI 高速接口、I2C 接口、ADC 模拟输入接口等多种标准化接口。各接口均采用标准化封装与引脚定义,方便开发人员连接传感器(如温度传感器、湿度传感器)、显示模块(如 OLED 屏)、存储模块(如 SD 卡)、通信模块等外部设备,可灵活拓展开发板的功能,适配多种入门级 FPGA 开发项目。

PCB 设计层面,将所有扩展接口集中布置在电路板边缘,便于接线操作,同时避免与其他模块的布线冲突;每个扩展接口均设计专用接地引脚与滤波电容,抑制接口信号干扰,提升接口通信稳定性;严格按照接口信号特性规划布线,区分高速接口与低速接口、数字接口与模拟接口的布线区域,避免不同接口信号之间的串扰;接口布线采用短直布线策略,减少信号延迟,确保扩展外设与开发板之间的通信顺畅、数据传输准确。

(五)时钟模块(时序控制单元)

时钟模块是整个系统时序控制的核心,为 FPGA 高速数字逻辑运算、单片机正常工作及各接口通信提供稳定、精准的时钟信号,是保障系统时序一致性与工作稳定性的关键,主要由无源晶振、有源晶振、时钟缓冲器及匹配电阻组成。根据器件需求,FPGA 采用高速有源晶振,提供 50MHz、100MHz 两种可选高频时钟信号,满足 FPGA 高速信号处理与时序控制需求;单片机采用无源晶振,提供低频时钟信号,兼顾工作稳定性与低功耗需求;时钟缓冲器用于时钟信号的放大与缓冲,确保时钟信号均匀传输至各需时器件,保障时序一致性。

PCB 设计中,将时钟模块尽量靠近 FPGA 与单片机的时钟引脚,缩短时钟信号线长度,减少时钟信号的延迟、衰减与干扰;时钟信号线采用阻抗匹配设计,通过调整线宽与线间距,使时钟信号阻抗匹配至标准值,避免信号反射;时钟模块周围布置接地防护圈,形成电磁隔离,有效隔离外部电磁干扰,确保时钟信号的稳定性与准确性;同时严格控制时钟信号线与其他信号线的间距,避免时钟信号干扰其他模块的正常工作。

(六)LED 指示模块(状态显示单元)

LED 指示模块主要用于直观显示开发板的工作状态,方便开发人员快速判断系统运行情况、排查故障,主要由电源指示灯、FPGA 工作指示灯、单片机工作指示灯、IO 口状态指示灯组成。各指示灯功能明确:电源指示灯用于指示开发板是否正常供电;FPGA 工作指示灯用于指示 FPGA 芯片是否正常工作(如程序下载成功、正常运行);单片机工作指示灯用于指示单片机的工作状态;IO 口状态指示灯用于指示对应 GPIO 口的电平状态(高电平亮、低电平灭),便于开发人员调试 IO 口功能。

PCB 设计中,将所有 LED 指示灯均匀布置在电路板边缘,便于开发人员观察;每个 LED 指示灯均串联限流电阻,精准控制通过 LED 的电流,避免电流过大烧毁器件;指示灯布线采用统一的接地设计,减少对其他模块的信号干扰;同时优化指示灯的丝印标注,明确每个指示灯的对应功能,提升调试便捷性。

(七)接地模块(抗干扰核心单元)

接地模块是提升开发板抗干扰能力、保障信号完整性与电源完整性的关键,采用多层接地设计,明确划分模拟地(AGND)、数字地(DGND)、电源地(PGND)三大地平面,各接地平面分工明确、互不干扰。其中,数字地主要为 FPGA、单片机、扩展接口等数字器件提供统一的接地参考,确保数字信号稳定传输;模拟地主要为 ADC 接口、时钟模块等模拟器件提供接地参考,避免模拟信号受到干扰;电源地为电源供电模块提供接地参考,滤除电源噪声,避免电源噪声干扰其他模块。

PCB 设计过程中,严格执行"模拟地与数字地单点连接"原则,避免数字信号干扰模拟信号,确保模拟信号的采集与传输准确性;增大接地平面面积,减少接地电阻与接地电感,提升接地可靠性;针对时钟信号、高速接口信号等关键信号,采用"地线包围"设计,进一步增强抗干扰能力;所有接地过孔均匀分布,确保接地顺畅,形成完整的接地网络,为整个开发板提供稳定的接地参考。

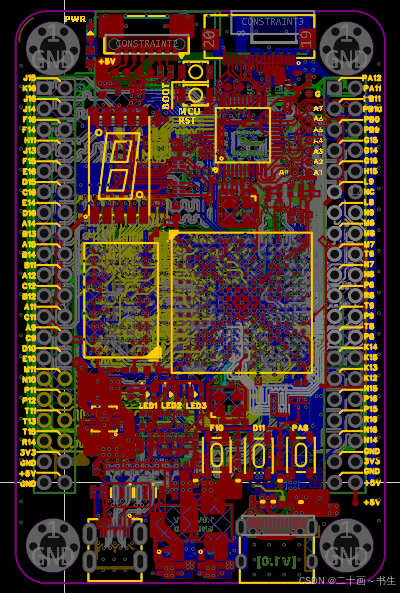

三、6 层 PCB 电路板绘制关键技术要点总结

相较于 4 层及以下层数的 PCB,6 层 PCB 设计的核心难点在于层叠规划、信号完整性控制、电源完整性控制及可制造性设计,结合本次逻辑派 FPGA-G1 开发板的设计需求与实践经验,针对 6 层 PCB 绘制过程中的核心技术要点、难点及解决方案进行总结,确保设计成果既满足功能需求、性能要求,又符合嘉立创 PCB 生产工艺规范,便于后期投产与调试,具体要点总结如下:

(一)层叠规划要点(基础核心要点)

层叠规划是 6 层 PCB 设计的基础,直接决定信号传输质量、抗干扰能力及可制造性,本次设计结合开发板的信号特性与供电需求,采用"信号层-接地层-电源层-电源层-接地层-信号层"的对称层叠结构,具体层叠顺序为 Top 层(信号层)→GND1 层(接地层)→Power1 层(电源层)→Power2 层(电源层)→GND2 层(接地层)→Bottom 层(信号层),核心要点如下:

-

对称层叠设计:采用对称结构可有效平衡 PCB 板的应力,减少电路板翘曲变形,适配嘉立创 6 层 PCB 生产工艺要求,降低生产不良率;

-

层间对应关系:接地层与电源层相邻布置,利用层间电容效应抑制电源噪声,提升电源完整性,同时为信号传输提供稳定的参考平面;

-

信号层布置:高速信号(如 FPGA 高速 IO、时钟信号、SPI 信号)优先布置在 Top 层与 Bottom 层,且上下均对应接地层,形成"微带线"传输结构,大幅减少信号干扰与信号反射,提升信号完整性;

-

电源层分割:将不同电压等级的电源(3.3V、1.8V、1.2V)分别布置在 Power1 层与 Power2 层,实现清晰的电源分割,避免不同电源域之间的干扰,同时便于布线与后期调试维护。

(二)BGA 器件扇出设计要点(重点难点)

本次设计中 FPGA 采用 BGA 封装,其引脚密度高、引脚间距小,扇出设计是 6 层 PCB 绘制的重点与难点,扇出质量直接影响后续布线效率、信号传输质量及器件工作稳定性,核心设计要点如下:

-

扇出方式选择:优先采用"通孔扇出"方式,靠近 BGA 引脚的过孔尽量密集布置,确保每个引脚都能顺利扇出,避免出现布线拥堵、引脚无法引出的问题;

-

扇出布线优化:扇出布线尽量短而直,缩短信号传输路径,减少信号延迟与信号衰减,扇出后的信号线快速连接至对应层的布线区域,避免在 BGA 封装下方长时间停留,减少信号串扰;

-

接地防护设计:在 BGA 封装下方预留足够数量的接地过孔,均匀分布,增强接地效果,抑制 BGA 内部信号的串扰,同时为核心芯片提供良好的散热通道;

-

引脚优先级规划:扇出过程中,优先保障电源引脚、关键信号引脚的扇出,避开此类引脚的布线冲突,确保电源引脚的扇出布线宽度满足电流需求,关键信号引脚的扇出布线避免干扰。

(三)信号完整性设计要点(性能核心要点)

FPGA 开发板包含大量高速信号(时钟信号、SPI 高速信号、FPGA 高速 IO 信号),信号完整性直接决定系统工作的稳定性与可靠性,是本次 6 层 PCB 设计的核心性能控制点,具体要点如下:

-

信号线长度控制:严格控制高速信号线的长度,避免过长导致信号衰减、延迟与反射,对于差分信号(如需要),确保两根差分线的长度匹配,误差控制在 5mil 以内,保障差分信号的传输质量;

-

阻抗匹配设计:根据不同信号的特性,设定合理的阻抗值(如高速信号 50Ω、视频信号 75Ω),通过调整信号线的线宽、线间距及层间距离,实现阻抗匹配,减少信号反射,提升信号完整性;

-

信号线隔离设计:避免高速信号线与低速信号线、模拟信号线交叉布置,划分独立的高速信号布线区域与低速信号布线区域,高速信号线尽量远离电路板边缘及大功率器件,减少外部电磁干扰与串扰;

-

关键信号防护设计:对于时钟信号、FPGA 核心控制信号等关键信号,采用"地线包围"或"差分对"设计,增强抗干扰能力,同时避免关键信号干扰其他模块的正常工作。

(四)电源完整性设计要点(稳定核心要点)

本次设计涉及多电源域、大电流供电(如 FPGA 核心电源),电源完整性设计的核心目标是为各模块提供稳定、纯净的供电,避免电源噪声、电压跌落等问题影响系统性能,具体要点如下:

-

电源分割优化:合理划分电源区域,将不同电压等级的电源布置在不同的电源层,分割边界清晰,避免不同电源域之间的串扰,同时便于后期调试与故障排查;

-

电源布线优化:增大电源布线的线宽与电源层的面积,减少线损与电压跌落,确保大电流供电时(如 FPGA 核心电源)无发热、电压不稳定等问题,电源布线尽量短而直,避免迂回布线;

-

滤波与去耦设计:在每个器件的电源引脚附近,均布置去耦电容(0.1μF)与高频滤波电容(10nF),电容尽量靠近引脚与接地过孔,有效滤除电源噪声,为器件提供瞬时稳定电流;在电源芯片的输出端,布置储能电容,稳定输出电压,避免电压波动;

-

电源芯片散热设计:优化电源芯片的布局,为电源芯片预留足够的散热空间,必要时增大电源芯片的散热焊盘,确保电源芯片在大电流供电时正常工作,避免因过热导致性能下降或损坏。

(五)可制造性设计(DFM)要点(生产适配要点)

设计过程中充分结合嘉立创 6 层 PCB 生产工艺规范,兼顾设计性能与可制造性,确保设计文件可直接用于投产,降低生产难度与生产成本,核心要点如下:

-

生产规范遵循:严格按照嘉立创 6 层 PCB 生产规范,控制线宽(最小线宽≥6mil)、线间距(最小线间距≥6mil)、过孔大小(最小过孔直径≥0.3mm),避免超出生产能力,降低生产不良率;

-

器件布局优化:器件布局均匀合理,避免过于密集,为焊接、调试预留足够的操作空间与散热空间,尤其是大功率器件与 BGA 封装器件,需预留足够的散热与焊接空间;

-

工艺边设计:在电路板边缘预留足够的工艺边(≥5mm),便于生产过程中的定位、加工与检测,避免生产过程中损坏电路板或器件;

-

丝印与焊盘设计:优化丝印设计,确保丝印清晰、准确,器件标号唯一,便于后期焊接、调试与维护,避免丝印覆盖过孔、焊盘,影响焊接质量;焊盘设计符合器件封装要求,确保焊接可靠性。

(六)DRC 检查与优化要点(质量管控要点)

DRC(设计规则检查)是确保 PCB 设计无误、规避设计隐患的关键步骤,需贯穿整个 PCB 设计流程,通过严格的 DRC 检查与优化,保障设计质量,核心要点如下:

-

设计规则预设:设计前期,结合嘉立创生产规范、项目功能需求及信号特性,设置合理的 DRC 检查规则,涵盖线宽、线间距、过孔、阻抗、接地、扇出等所有关键设计环节,为后续设计与检查提供依据;

-

实时检查修正:布线过程中,实时开启 DRC 检查功能,及时发现并修正布线错误(如短路、开路、线间距不足、阻抗不匹配等),避免错误累积,降低后期优化难度;

-

全面检查验证:布线完成后,进行全面的 DRC 检查,确保无任何违规项,同时结合信号完整性、电源完整性要求,检查器件布局、布线优化、接地设计等是否合理,确保设计满足性能需求;4. 针对性优化:针对 DRC 检查中发现的问题,结合信号特性、可制造性要求进行针对性优化,避免为了满足 DRC 规则而牺牲信号质量与功能需求,实现设计规则与性能需求的平衡。

四、PCB展示图