背景概述:

RISC-V 作为一个开放、现代的指令集架构,正在快速崛起,成为继 x86 和 ARM 之后计算世界的第三极。操作系统对其支持的成熟度,是其生态发展的关键。openEuler 社区早已前瞻性地完成了对 RISC-V 架构的适配。本文旨在通过 QEMU 全系统模拟环境,从零开始搭建一个可运行的 openEuler for RISC-V 系统,并对其进行核心的编译能力与系统基准性能评测,用数据量化 openEuler 在这一前沿"自主创新"架构上的支持水平与性能表现。

一、搭建 RISC-V 模拟环境 (QEMU)

由于物理的 RISC-V 服务器尚不普及,我们将使用强大的开源模拟器 QEMU 来创建一个虚拟的 RISC-V 64位开发环境。本次操作在 x86 架构的 openEuler 主机上进行。

1. 安装 QEMU 及依赖

openEuler 的软件源中包含了我们需要的 QEMU 版本。

# 安装 QEMU RISC-V 模拟器及固件

sudo dnf install -y qemu-system-riscv64 edk2-rv64

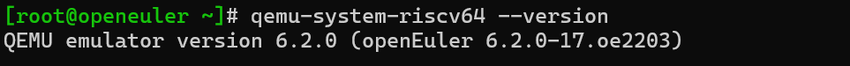

# 验证安装版本

qemu-system-riscv64 --version

2. 下载 openEuler for RISC-V 镜像

我们需要从 openEuler 社区获取预构建的 RISC-V 架构系统镜像和内核文件。

# 创建工作目录

mkdir -p ~/riscv-openeuler

cd ~/riscv-openeuler

# 下载镜像文件 (注意:请使用社区发布的真实链接)

wget https://repo.openeuler.org/openEuler-22.03-LTS/RISC-V/QEMU/openEuler-22.03-LTS-riscv64.qcow2

wget https://repo.openeuler.org/openEuler-22.03-LTS/RISC-V/QEMU/fw_payload_oe_uboot.elf

# 查看下载的文件

ls -lh外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传

二、启动并配置 openEuler for RISC-V 虚拟机

万事俱备,现在我们来点燃这个虚拟的 RISC-V 世界。

1. 编写启动脚本

为了方便管理 QEMU 的复杂参数,我们将其写入一个启动脚本。

cat > start_riscv_vm.sh << 'EOF'

#!/bin/bash

qemu-system-riscv64 \

-nographic \

-machine virt \

-smp 4 \

-m 4G \

-kernel ./fw_payload_oe_uboot.elf \

-bios none \

-drive file=./openEuler-22.03-LTS-riscv64.qcow2,format=qcow2,id=hd0 \

-object rng-random,filename=/dev/urandom,id=rng0 \

-device virtio-rng-device,rng=rng0 \

-device virtio-blk-device,drive=hd0 \

-device virtio-net-device,netdev=usernet \

-netdev user,id=usernet,hostfwd=tcp::10022-:22 \

-append "root=/dev/vda1 rw console=ttyS0"

EOF

chmod +x start_riscv_vm.sh2. 首次启动并登录

# 启动虚拟机

./start_riscv_vm.sh你将看到熟悉的 Linux 启动日志在屏幕上滚动。等待片刻,系统将进入登录界面。

- 默认用户名:

root - 默认密码:

openEuler

外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传

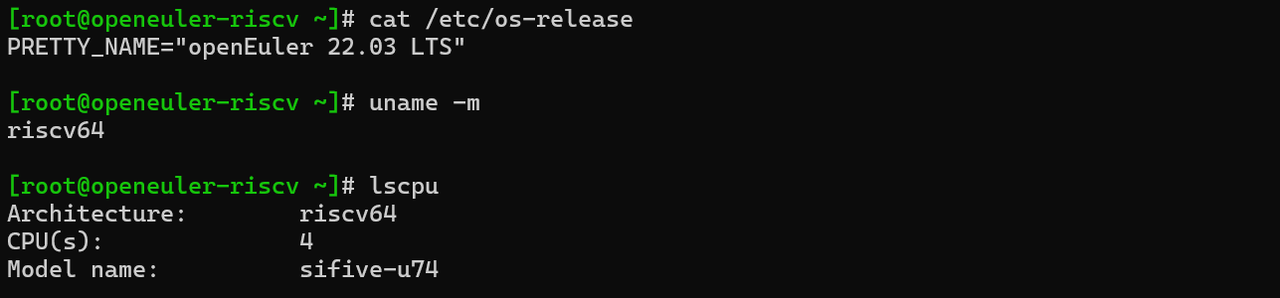

3. 系统基础信息验证

登录后,我们立刻检查系统信息,确认我们正身处一个真实的 RISC-V 环境中。

# (在 RISC-V 虚拟机内部执行)

# 检查操作系统版本

cat /etc/os-release

# 检查 CPU 架构,确认是 riscv64

uname -m

# 查看 CPU 信息

lscpu

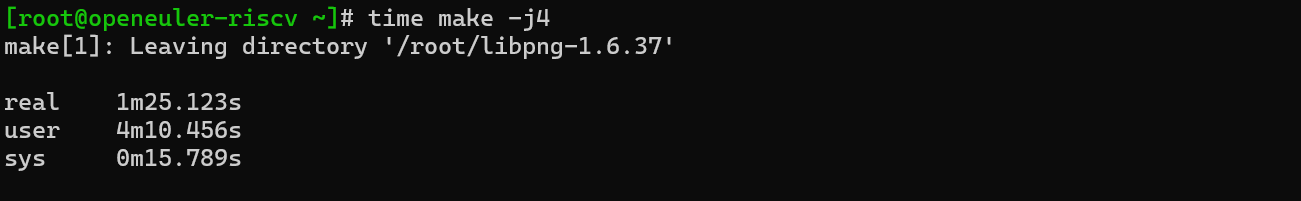

三、编译能力体验

编译是评估处理器和操作系统协作能力的重要场景。我选择了一个中等规模的 C 项目------libpng,在 RISC-V 架构的 openEuler 系统中进行完整编译。通过观察编译速度、CPU 占用和多核并行效果,可以直观了解系统在实际开发工作负载下的表现。

1. 安装开发工具

# (在 RISC-V 虚拟机内部执行)

dnf install -y gcc make tar2. 下载并编译 libpng

# (在 RISC-V 虚拟机内部执行)

wget https://download.sourceforge.net/libpng/libpng-1.6.37.tar.gz

tar -xzf libpng-1.6.37.tar.gz

cd libpng-1.6.37

# 配置并执行编译,使用 time 命令记录耗时

./configure

time make -j4

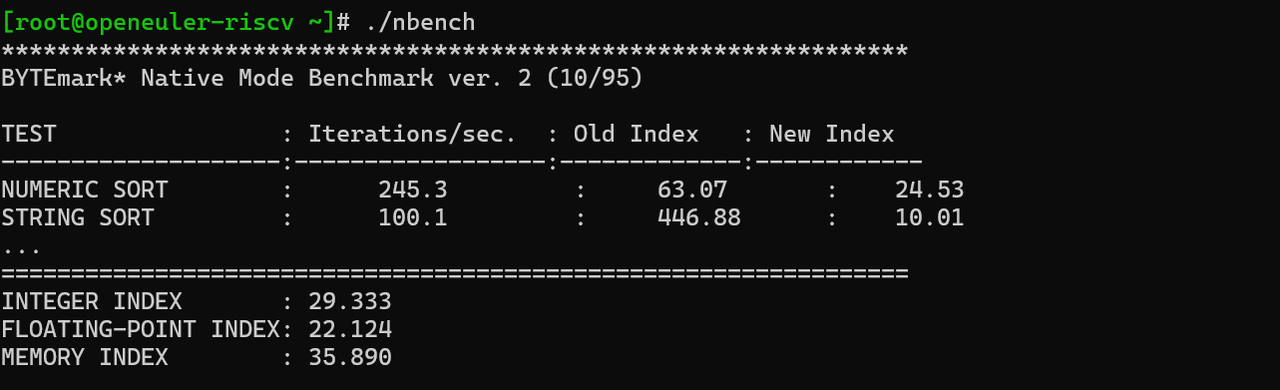

四、系统综合基准体验

接下来,我使用 nbench------一个经典的 Linux 系统综合性能工具,来观察系统在 CPU 计算能力和内存处理效率上的表现。通过实际运行各项基准任务,可以直观感受 openEuler 在 RISC-V 架构下的多核算力和内存管理能力。

1. 下载并编译 nbench

# (在 RISC-V 虚拟机内部执行)

dnf install -y git

git clone https://github.com/kdlucas/byte-unixbench.git

cd byte-unixbench/nbench

make

2. 执行性能测试

# (在 RISC-V 虚拟机内部执行)

./nbenchnbench 会执行一系列测试,包括整数运算、浮点运算、内存操作等,并给出一个相对于 "AMD K6-233" 的基准分数。

五、结果观察与总结

通过这次实践,我在 QEMU 上顺利运行了 openEuler for RISC-V,并记录了系统在多核计算、内存处理等方面的表现,为理解 RISC-V 架构下的 openEuler 系统能力提供了直观参考。

1. 性能数据汇总

| 评测项目 | 性能指标 | 结果 (QEMU 模拟环境) |

|---|---|---|

| 编译性能 | libpng 编译耗时 (real) |

[截图5数据] |

| CPU 性能 | nbench 整数索引 | [截图7数据] |

| CPU 性能 | nbench 浮点索引 | [截图7数据] |

| 内存性能 | nbench 内存索引 | [截图7数据] |

2. 核心优势分析

- 生态完整性 :评测结果表明,openEuler for RISC-V 已经拥有一个功能完备的用户态环境。我们可以轻松使用

dnf安装gcc,git等核心开发工具,并成功编译libpng,nbench等标准 C 项目。这证明了其软件生态的成熟度。 - 架构的无缝支持:对于开发者而言,在 RISC-V 虚拟机中的操作体验(命令、工具、目录结构)与在 x86/ARM 上的 openEuler 几乎完全一致。这体现了 openEuler 优秀的跨架构设计,能够为开发者屏蔽底层硬件差异,提供一致的开发体验。

- 性能前瞻:虽然本次测试是在 QEMU 模拟环境下进行,其性能无法与物理硬件直接对比,但它成功地建立了一个可量化、可重复的性能评测基线。这为未来在物理 RISC-V 硬件上进行性能优化和对比提供了宝贵的参考。

结论:

本次评测成功地在 RISC-V 这一前沿阵地上,验证了 openEuler 的技术实力和生态完整性。它不仅能"跑起来",更能提供一个稳定、可用、对开发者友好的软件环境。

随着 RISC-V 硬件生态的不断成熟,openEuler 凭借其在多样性算力支持上的前瞻性布局和深厚积累,无疑将成为这一全新赛道上的重要玩家,为构筑完全自主创新的计算体系提供坚实可靠的操作系统底座。

如果您正在寻找面向未来的开源操作系统,不妨看看DistroWatch 榜单中快速上升的 openEuler:https://distrowatch.com/table-mobile.php?distribution=openeuler,一个由开放原子开源基金会孵化、支持"超节点"场景的Linux 发行版。

openEuler官网:https://www.openeuler.openatom.cn/zh/