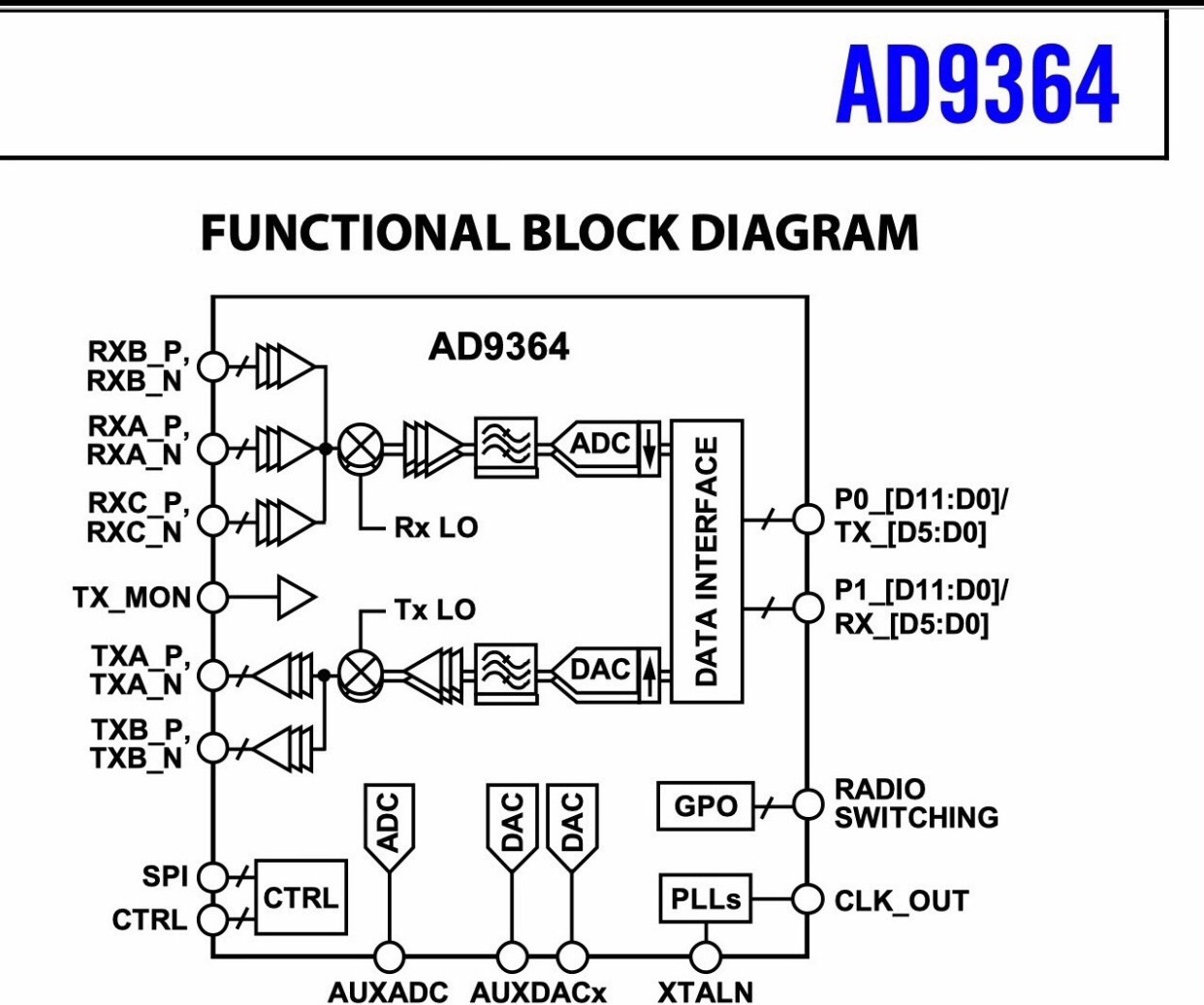

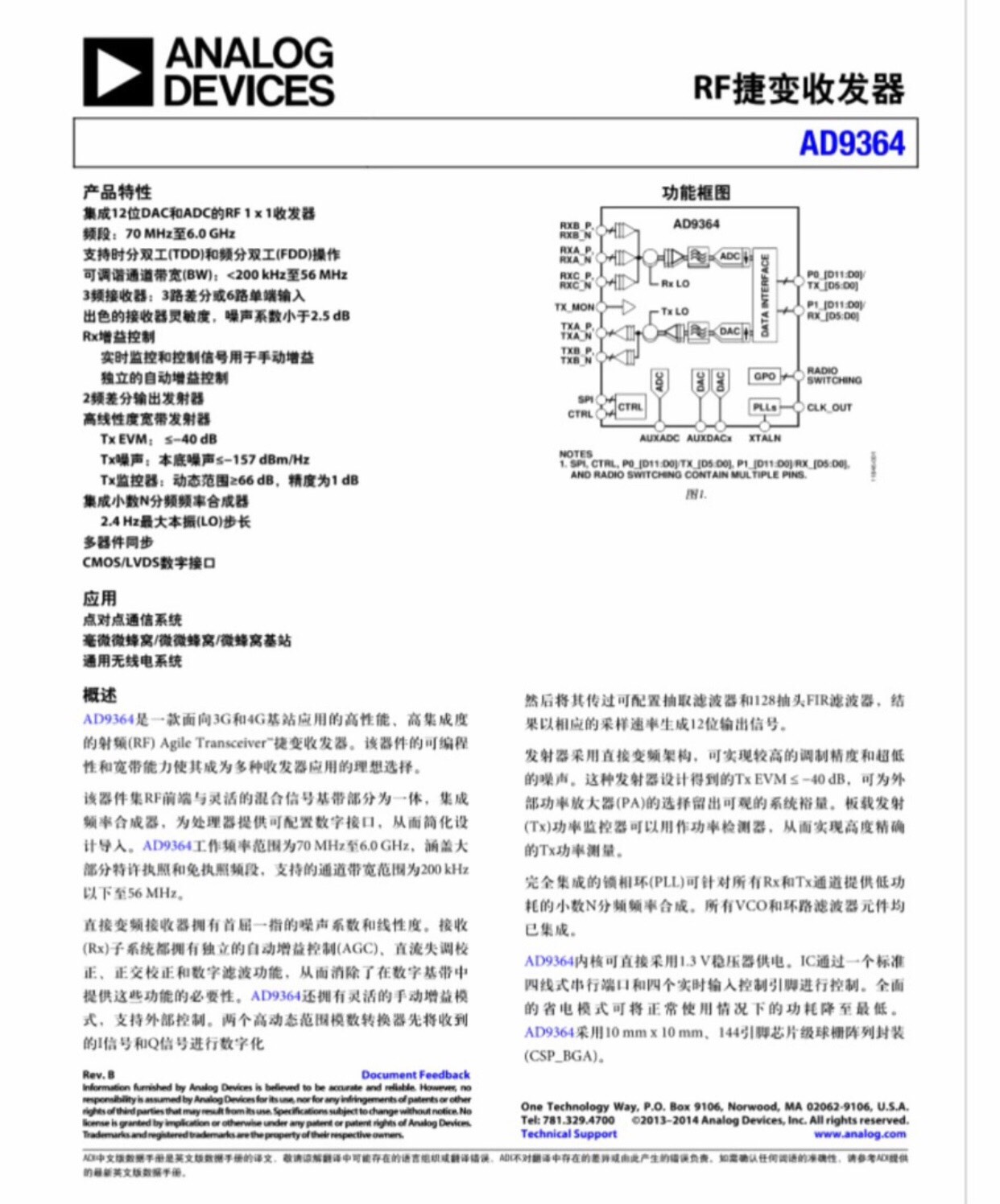

模拟ic设计,AD9364,adi的射频收发机模块的reserve电路,可用于基站应用,规模较大,是综合性能较好的射频收发机芯片。 芯片正常在70MHz-6.2GHZ工作,电路规模非常大,有adc,PLL,NX,RX等等模块,可以长期参考学习使用,适合有一定经验的模拟设计工程师,电路可以直接导入到cadence查看结构和宽长比等参数。

在模拟IC设计的领域里,ADI的AD9364射频收发机模块犹如一颗璀璨的明星,尤其是它的reserve电路,在基站应用方面大放异彩。这可是一款规模较大,综合性能十分出色的射频收发机芯片哦。

一、AD9364 的工作频段

AD9364能在 70MHz - 6.2GHZ 的频率范围内正常工作,如此宽泛的频段,为其在多种通信场景中的应用提供了可能。想象一下,从相对低频的信号处理到高频段的高速数据传输,AD9364 都能应对自如,这背后是复杂而精妙的电路设计在支撑。

二、丰富的内部模块

这款芯片可不是"吃素的",它内部集成了众多重要模块,像 ADC(模拟数字转换器)、PLL(锁相环)、NX 以及 RX 等等。每个模块都各司其职,共同协作完成射频信号的收发处理。

ADC 模块

ADC 的作用不言而喻,它负责将模拟信号转换为数字信号,以便后续数字电路进行处理。在代码层面,如果我们要对 ADC 采集的数据进行简单处理,比如计算采集数据的均值,在Python中可以这样写:

python

# 假设 adc_data 是从 ADC 获取的一组数据列表

adc_data = [12, 15, 18, 20, 22]

total = sum(adc_data)

count = len(adc_data)

average = total / count

print(f"ADC 数据均值: {average}")这里简单的几行代码,展示了对 ADC 采集数据的一个基础处理思路。实际在 AD9364 中,ADC 模块会将接收到的射频模拟信号精准地转换为数字信号,这些数字信号会被传递到芯片内的其他数字处理模块进行进一步分析和处理。

PLL 模块

PLL(锁相环)模块则是负责产生稳定的时钟信号。时钟信号对于整个芯片的稳定运行至关重要,它就像是乐队的指挥,各个模块都按照它的节奏工作。在Verilog 代码中,一个简单的 PLL 模块示例可以这样写:

verilog

module simple_pll (

input wire clk_in, // 输入时钟信号

output reg clk_out // 输出经过锁相环处理的时钟信号

);

reg [31:0] counter;

always @(posedge clk_in) begin

if (counter == 32'd1000) begin // 假设经过1000个周期调整一次输出时钟

clk_out = ~clk_out;

counter = 32'd0;

end else begin

counter = counter + 1;

end

end

endmodule这段 Verilog 代码构建了一个简易的 PLL 模块,通过计数器对输入时钟信号进行分频等处理,产生稳定的输出时钟信号。在 AD9364 中,PLL 模块更加复杂和精确,它确保芯片内各个模块能在准确的时钟驱动下高效工作。

三、庞大的电路规模及学习价值

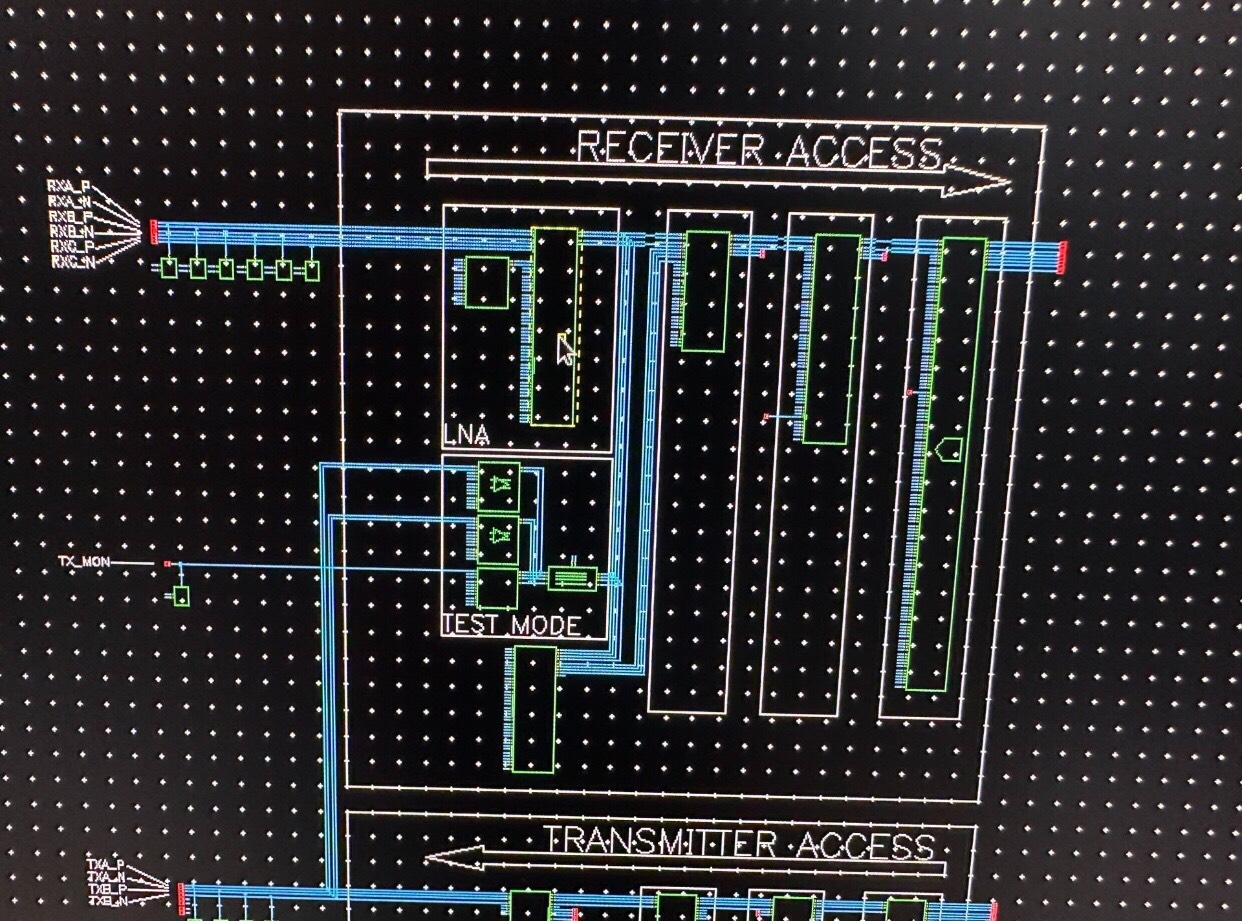

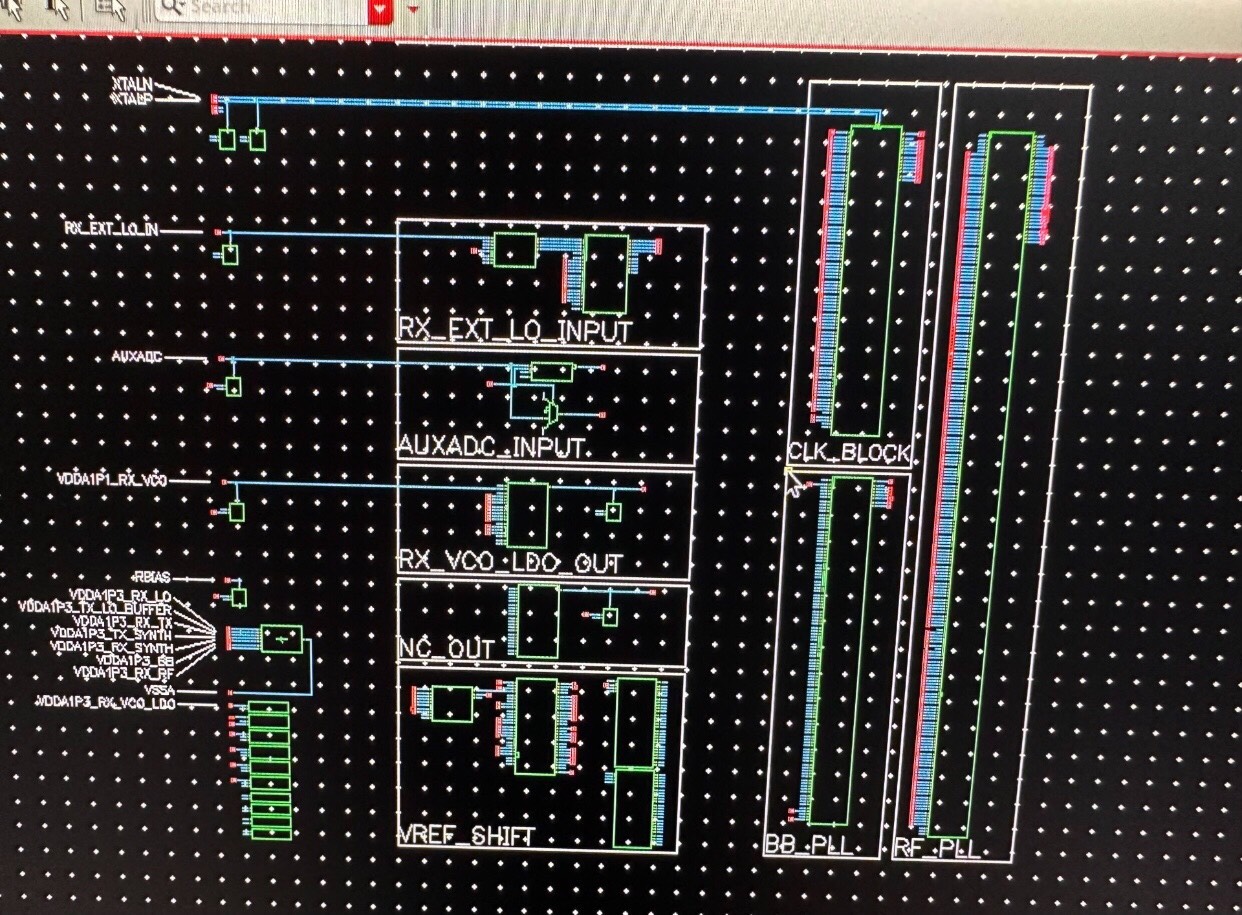

AD9364 的电路规模相当庞大,这对于有一定经验的模拟设计工程师来说,是一个绝佳的长期参考学习素材。它里面各种模块的设计思路、电路布局以及它们之间的协同工作方式,都蕴含着深厚的模拟IC设计知识。

而且,这个电路可以直接导入到 Cadence 软件中查看结构和宽长比等参数。在 Cadence 里,你可以像探险家一样,深入探索 AD9364 电路的每一个角落,了解电阻、电容、晶体管等元件的布局和参数设置,从而更好地理解模拟IC设计的精髓。

总之,AD9364 这款射频收发机芯片,无论是对于从事基站应用开发的工程师,还是渴望提升模拟IC设计能力的学习者,都有着不可估量的价值,值得我们深入研究和学习。